\n

## Diagram: DRAM Bank Operation with PRAC Timing

### Overview

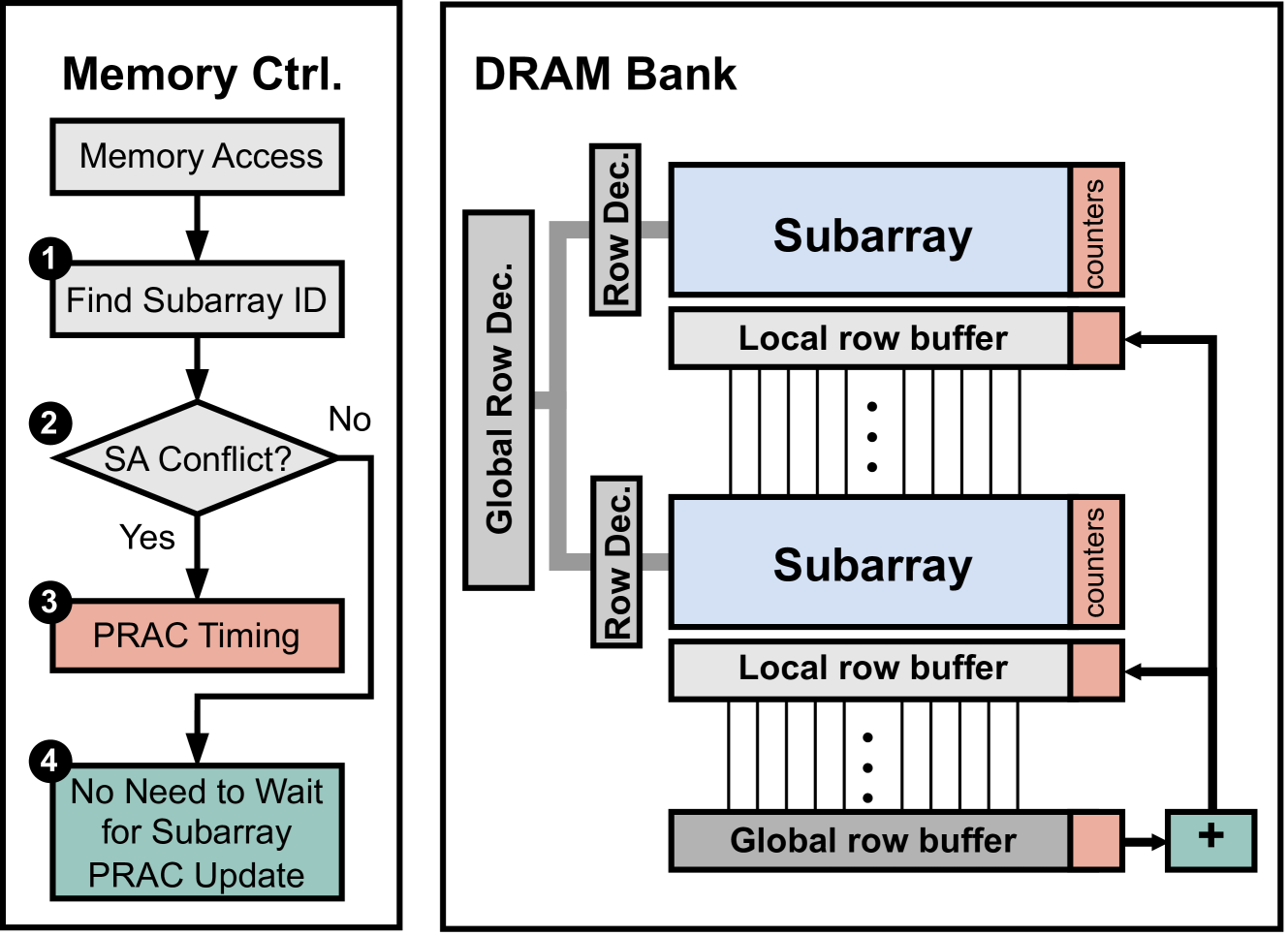

The image is a diagram illustrating the operation of a DRAM bank, specifically focusing on how the memory controller handles subarray conflicts and PRAC (Precharge Access) timing. The diagram is split into two main sections: "Memory Ctrl." (Memory Controller) on the left and "DRAM Bank" on the right. It depicts a flow chart within the memory controller and the internal structure of the DRAM bank, showing how they interact.

### Components/Axes

The diagram consists of the following components:

* **Memory Ctrl. (Memory Controller):** Contains blocks representing "Memory Access", "Find Subarray ID", "SA Conflict?", "PRAC Timing", and "No Need to Wait for Subarray PRAC Update".

* **DRAM Bank:** Contains "Global Row Dec.", "Row Dec.", "Subarray" (repeated twice), "Local row buffer" (repeated twice), "Global row buffer", and "counters" (repeated twice).

* **Flow Arrows:** Indicate the direction of data flow and decision-making.

* **Numbered Steps:** 1, 2, 3, and 4 mark the sequence of operations.

### Detailed Analysis or Content Details

The diagram illustrates the following process:

1. **Memory Access:** The process begins with a memory access request.

2. **Find Subarray ID:** The memory controller identifies the subarray associated with the access.

3. **SA Conflict?:** A decision is made whether there is a subarray (SA) conflict.

* **Yes:** If a conflict exists, the process proceeds to "PRAC Timing".

* **No:** If no conflict exists, the process proceeds to "No Need to Wait for Subarray PRAC Update".

4. **PRAC Timing:** This block represents the timing required for precharge access, likely to resolve the subarray conflict.

5. **No Need to Wait for Subarray PRAC Update:** This indicates that the operation can proceed without waiting for a PRAC update, as there was no conflict.

Within the DRAM Bank section:

* **Global Row Dec.:** Drives the "Row Dec." signals.

* **Row Dec.:** Selects specific rows within the subarrays.

* **Subarray:** Contains a "Local row buffer" and a series of dotted lines representing data storage.

* **Local row buffer:** Stores data from the selected subarray rows.

* **counters:** Connected to the subarrays, likely for addressing or timing purposes.

* **Global row buffer:** A larger buffer connected to both subarrays.

* The DRAM Bank contains two subarrays stacked vertically.

* The "counters" are positioned to the right of each subarray.

* The "Global row buffer" is positioned below the second subarray.

* A "+" symbol is present at the bottom-right of the DRAM Bank section, likely indicating a summation or combination of data.

### Key Observations

* The diagram highlights the importance of managing subarray conflicts in DRAM operation.

* The PRAC timing mechanism is presented as a solution to resolve these conflicts.

* The DRAM bank structure shows a hierarchical arrangement with global and local row buffers.

* The diagram focuses on the control flow and data path within the DRAM system.

### Interpretation

The diagram demonstrates a simplified model of how a memory controller manages access to a DRAM bank, specifically addressing the issue of subarray conflicts. The PRAC timing mechanism is presented as a critical step in resolving these conflicts, ensuring data integrity and efficient memory access. The hierarchical structure of the DRAM bank, with global and local row buffers, suggests a strategy for optimizing data storage and retrieval. The diagram implies that the memory controller actively monitors for subarray conflicts and adjusts the timing accordingly to maintain system performance. The "+" symbol at the bottom right suggests that the data from the two subarrays may be combined or processed in some way. This diagram is a high-level overview and does not delve into the specific details of the PRAC timing algorithm or the data processing performed by the "+" symbol. It serves as a conceptual illustration of the key components and interactions within a DRAM system.