# Technical Document Extraction: Memory Controller and DRAM Bank Architecture

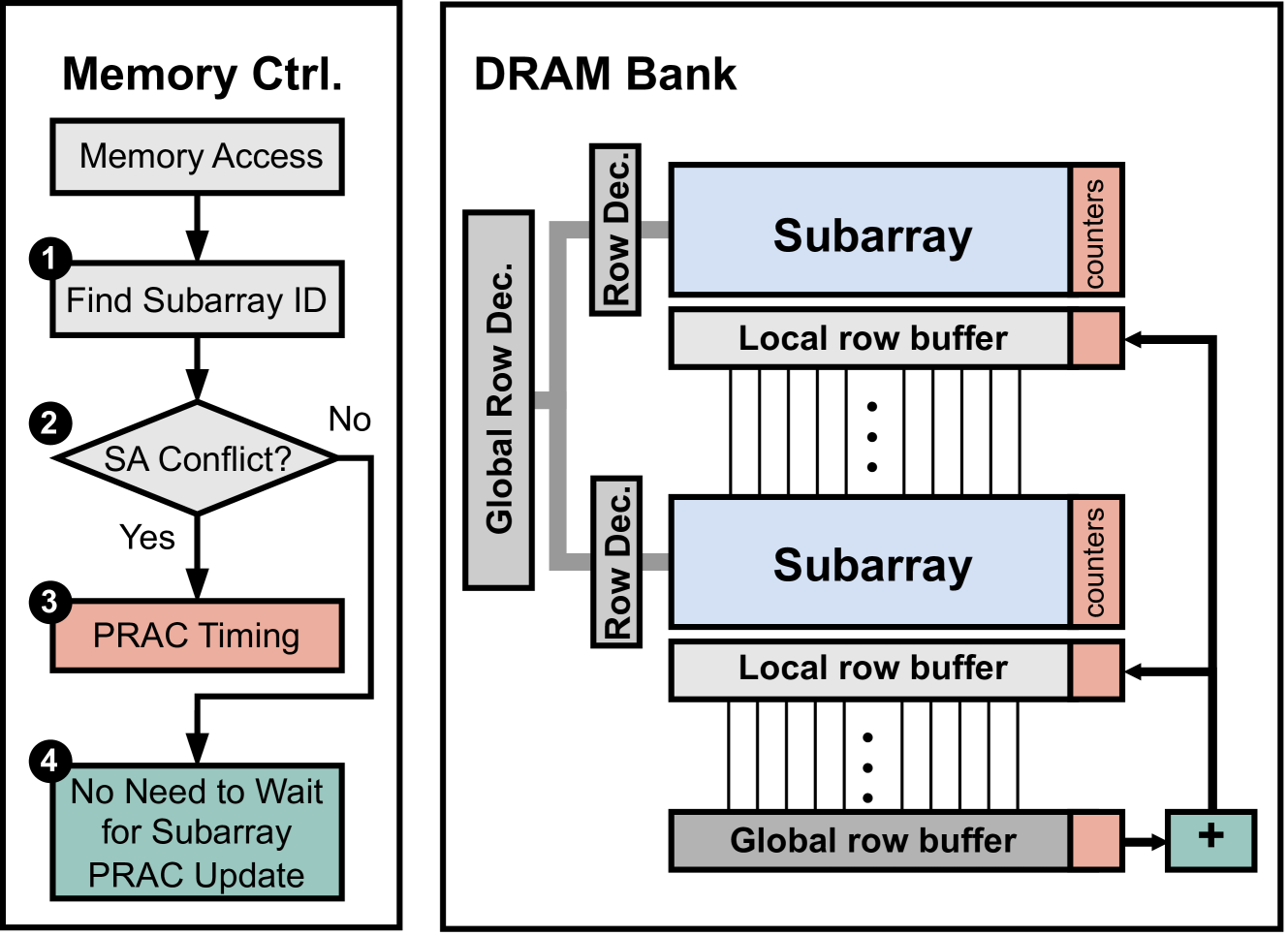

## Left Section: Memory Controller (Memory Ctrl.) Flowchart

### Components and Flow:

1. **Memory Access**

- **Input**: Initiates memory access request.

- **Output**: Triggers "Find Subarray ID" step.

2. **Find Subarray ID**

- **Purpose**: Identifies the target subarray for memory access.

- **Output**: Feeds into "SA Conflict?" decision node.

3. **SA Conflict?** (Decision Diamond)

- **Yes Path**:

- **PRAC Timing** (Step 3):

- **Function**: Manages PRAC (Precharge to Active) timing constraints.

- **Output**: Triggers "No Need to Wait for Subarray PRAC Update" (Step 4).

- **No Path**:

- **Loop**: Returns to "Find Subarray ID" (Step 1).

4. **No Need to Wait for Subarray PRAC Update**

- **Function**: Confirms subarray is ready for access without PRAC delay.

- **Output**: Completes memory access cycle.

### Color Coding:

- **Pink**: Decision nodes and timing steps (e.g., "SA Conflict?", "PRAC Timing").

- **Green**: Final confirmation step ("No Need to Wait...").

---

## Right Section: DRAM Bank Architecture

### Hierarchical Structure:

1. **Global Row Decoder**

- **Input**: Receives row address signals.

- **Output**: Routes signals to individual subarrays.

2. **Subarrays** (2 instances shown)

- **Structure**:

- **Blue Blocks**: Represent subarray memory cells.

- **Pink Counters**: Track access operations (e.g., row activations).

- **Connections**:

- Linked to **Local Row Buffers** via vertical lines.

3. **Local Row Buffers** (2 instances)

- **Function**: Temporarily store data during row access.

- **Connections**:

- Feed into **Global Row Buffer** via horizontal lines.

4. **Global Row Buffer**

- **Role**: Aggregates data from all local buffers for output.

- **Output**: Final data path marked with a "+" symbol.

### Spatial Grounding:

- **Vertical Flow**:

- Global Row Decoder → Subarrays → Local Row Buffers → Global Row Buffer.

- **Color Legend**:

- **Blue**: Subarrays.

- **Gray**: Buffers (Local/Global).

- **Pink**: Counters.

---

## Key Observations:

1. **Memory Controller Logic**:

- Prioritizes conflict resolution ("SA Conflict?") to optimize PRAC timing.

- Avoids unnecessary delays via conditional checks.

2. **DRAM Bank Design**:

- Hierarchical buffering (local → global) minimizes latency.

- Counters enable real-time monitoring of access patterns.

3. **Integration**:

- Memory controller coordinates with DRAM bank via subarray ID resolution.

- PRAC timing management ensures synchronization between controller and bank.

## Notes:

- No numerical data or trends present; diagram focuses on architectural flow and component interactions.

- All labels and textual elements transcribed verbatim.

- Color coding aligns with component roles (e.g., pink for timing/counters).