# Technical Diagram Analysis: Xylo HDK System Architecture

## Diagram Overview

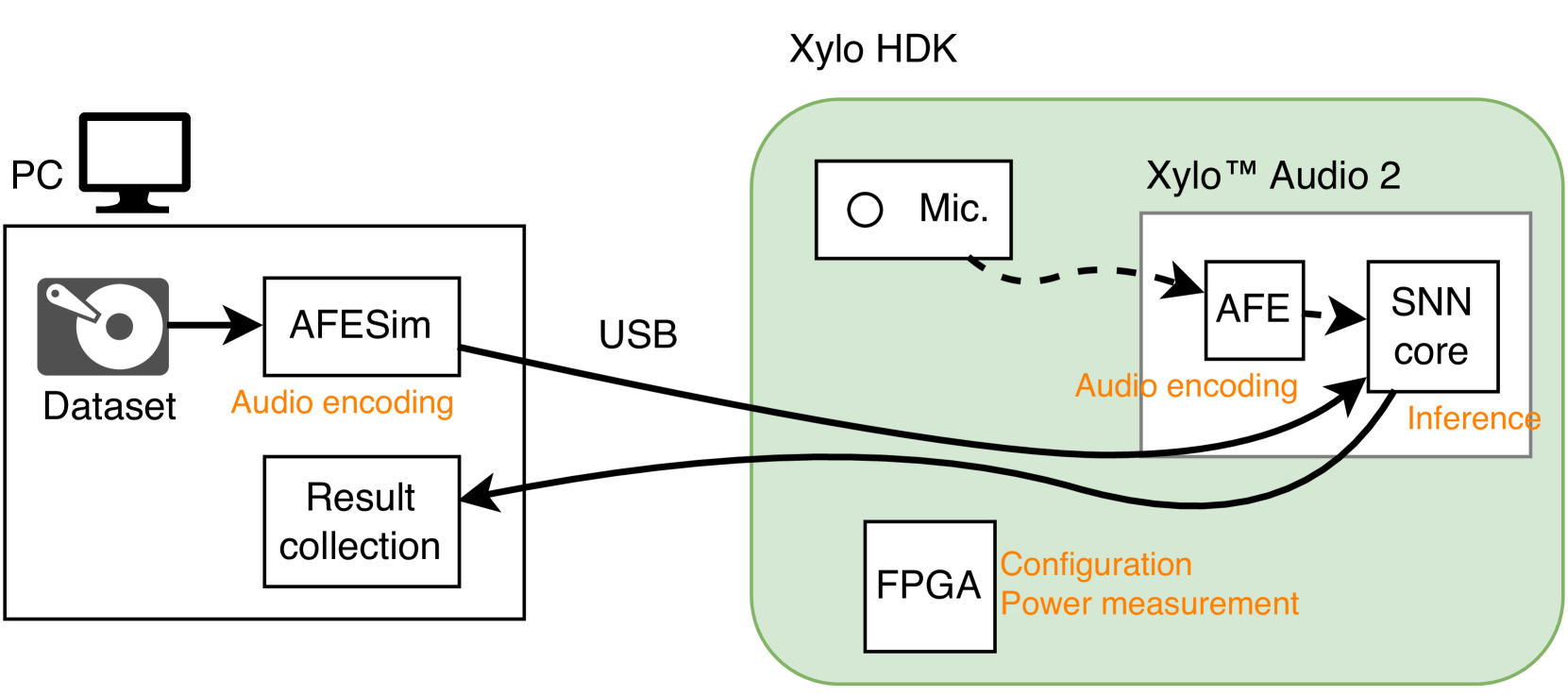

This flowchart illustrates the data flow and processing pipeline between a PC and Xylo HDK hardware components. The diagram uses two primary color-coded regions:

- **White background**: PC-side processing

- **Light green background**: Xylo HDK hardware components

## PC-Side Processing (White Region)

1. **Dataset** (Floppy disk icon)

- Represents input data source

- Connected via USB to AFESim

2. **AFESim** (Text box)

- Processes dataset through "Audio encoding"

- Outputs to "Result collection"

3. **Result collection** (Text box)

- Receives processed data from AFESim

## Xylo HDK Hardware (Green Region)

1. **Microphone (Mic.)** (Circle icon)

- Connected via dashed line to AFE

- Represents audio input source

2. **AFE (Analog Front End)** (Text box)

- Performs "Audio encoding"

- Connected to both:

- SNN core (via solid line)

- FPGA (via dashed line)

3. **SNN core (Spiking Neural Network)** (Text box)

- Receives encoded audio from AFE

- Performs "Inference" processing

4. **FPGA (Field-Programmable Gate Array)** (Text box)

- Handles "Configuration" and "Power measurement"

- Connected to AFE via dashed line

## Data Flow Pathways

1. **Primary Path (Solid Lines)**

- PC → Dataset → AFESim → Audio encoding → Result collection

- Xylo HDK: Mic. → AFE → Audio encoding → SNN core → Inference

2. **Secondary Path (Dashed Lines)**

- AFESim ↔ FPGA (Configuration/Power measurement)

- AFE ↔ FPGA (Configuration)

## Key Technical Components

- **Audio encoding**: Appears in both PC and Xylo HDK paths

- **Inference**: Exclusive to SNN core processing

- **Power measurement**: FPGA-specific function

- **Configuration**: Dual-purpose (AFE-FPGA and AFESim-FPGA)

## Spatial Component Relationships

- PC components form a linear left-to-right flow

- Xylo HDK components arranged in a functional block diagram

- USB connection serves as the primary data bridge between systems

- Dashed lines indicate bidirectional/configuration relationships

## Process Flow Logic

1. Data originates in PC Dataset

2. Processed through AFESim (audio encoding)

3. Results collected and sent to Xylo HDK

4. Xylo HDK processes real-time audio through:

- AFE encoding

- SNN core inference

- FPGA configuration/power monitoring

## Technical Constraints

- No numerical data or chart elements present

- All connections use either solid (data flow) or dashed (configuration) lines

- No legend elements required due to consistent iconography

- Color coding strictly differentiates system boundaries

## System Integration Points

1. USB interface between PC and Xylo HDK

2. AFE-FPGA configuration link

3. AFESim-FPGA bidirectional communication

4. SNN core as central inference processor

This architecture demonstrates a hybrid system combining software processing (PC) with hardware-accelerated neural network inference (Xylo HDK), utilizing FPGA for low-level configuration and power management.