## DRAM Architecture Diagram

### Overview

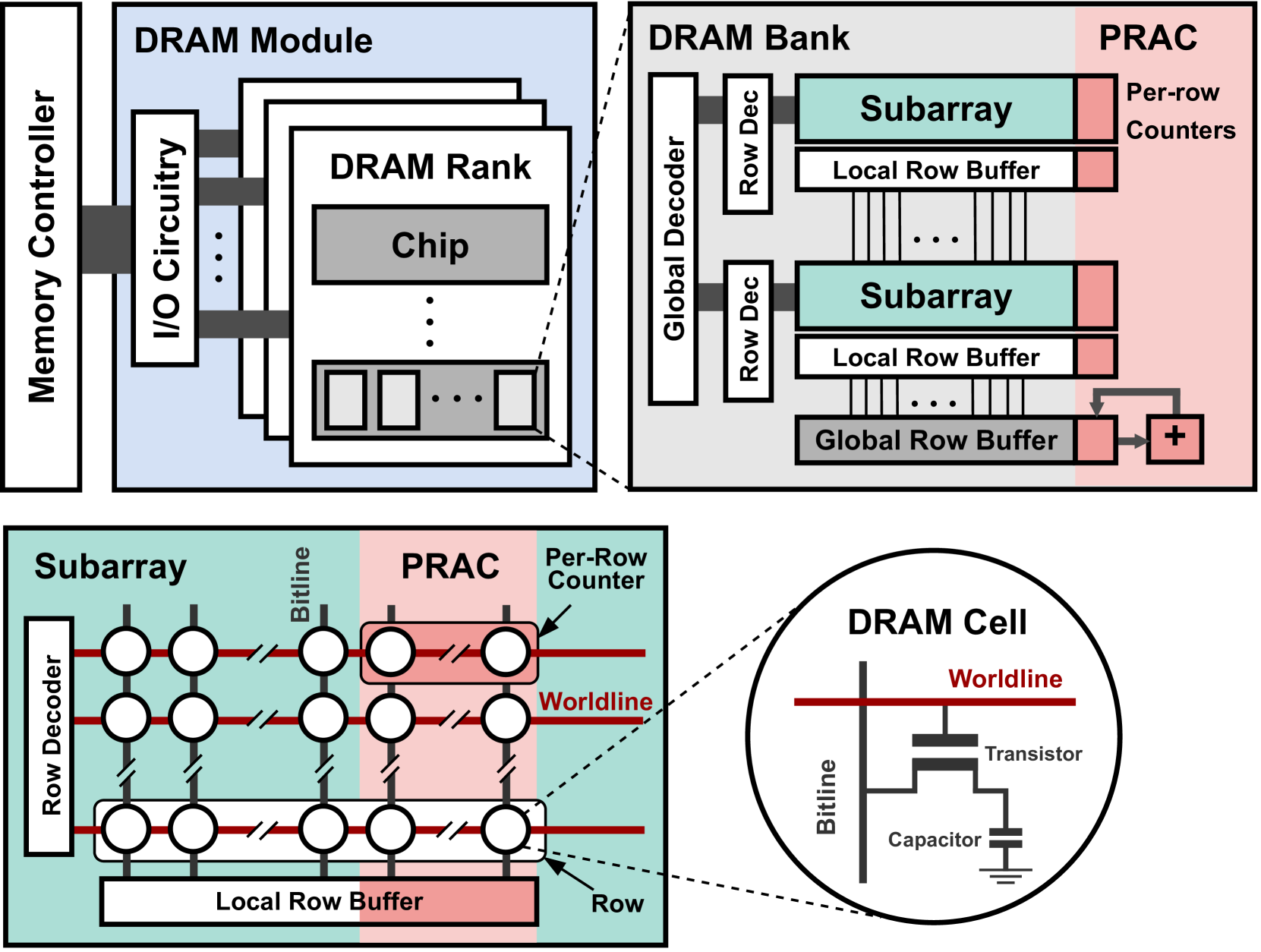

The image is a diagram illustrating the architecture of a DRAM (Dynamic Random-Access Memory) system, breaking it down from the module level to the individual cell level. It shows the hierarchical structure, including the DRAM module, DRAM bank, subarray, and DRAM cell, highlighting components like row decoders, bitlines, wordlines, and the PRAC (Per-Row Activation Counter).

### Components/Axes

* **Memory Controller:** The outermost component, containing I/O Circuitry.

* **DRAM Module:** Contains multiple DRAM Ranks.

* **DRAM Rank:** Contains multiple Chips.

* **DRAM Bank:** Contains Global Decoder, Row Decoders, Subarrays, Local Row Buffers, and a Global Row Buffer.

* **Subarray:** Contains Row Decoder, Bitlines, Worldlines, Local Row Buffer, and Row.

* **PRAC (Per-Row Activation Counter):** Associated with each subarray and the global row buffer.

* **DRAM Cell:** Contains a Worldline, Bitline, Transistor, and Capacitor.

### Detailed Analysis

1. **DRAM Module:**

* Located in the top-left of the image.

* Contains multiple DRAM Ranks stacked vertically.

* Each DRAM Rank contains multiple Chips.

* Connected to the Memory Controller via I/O Circuitry.

2. **DRAM Bank:**

* Located in the top-center of the image.

* Contains two Subarrays stacked vertically.

* Each Subarray has a Local Row Buffer.

* A Global Row Buffer is at the bottom.

* Global Decoder and Row Decoders are present.

* PRAC (Per-row Counters) are associated with each Subarray.

* The Global Row Buffer connects to a summation block "+".

3. **Subarray:**

* Located in the bottom-left of the image.

* Shows a grid of DRAM cells.

* Row Decoder is on the left.

* Bitlines run vertically.

* Worldlines run horizontally.

* Local Row Buffer is at the bottom.

* PRAC (Per-Row Counter) is present on the right.

4. **DRAM Cell:**

* Located in the bottom-right of the image, shown in a magnified view.

* Consists of a Worldline, Bitline, Transistor, and Capacitor.

* The Transistor connects the Bitline to the Capacitor, controlled by the Worldline.

### Key Observations

* The diagram illustrates the hierarchical organization of DRAM, from the module down to the individual cell.

* The PRAC is a key component, likely used for tracking row activations.

* The DRAM cell structure shows the basic components of a memory cell.

### Interpretation

The diagram provides a detailed overview of DRAM architecture, emphasizing the organization and key components at different levels of abstraction. The inclusion of the PRAC suggests a mechanism for managing or optimizing row activations, potentially to improve performance or reduce power consumption. The diagram is useful for understanding the fundamental structure and operation of DRAM memory systems.