\n

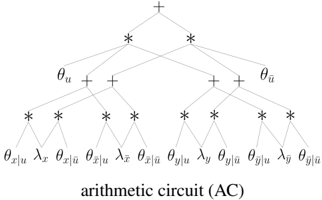

## Diagram: Arithmetic Circuit (AC)

### Overview

The image depicts a binary tree diagram representing an arithmetic circuit (AC). The circuit performs a series of multiplications and additions, culminating in a final addition at the root. The diagram is structured hierarchically, with leaf nodes representing variables and intermediate nodes representing operations.

### Components/Axes

The diagram consists of the following components:

* **Leaf Nodes:** Represented by variables: θ<sub>xu</sub>, λ<sub>x</sub>, x<sub>r|a</sub>, θ<sub>r|u</sub>, λ<sub>x</sub>, x<sub>r|a</sub>, θ<sub>yu</sub>, λ<sub>y</sub>, y<sub>r|a</sub>, θ<sub>g|u</sub>, λ<sub>g</sub>, g<sub>r|a</sub>.

* **Multiplication Nodes:** Represented by the symbol "*". These nodes take two inputs and perform multiplication.

* **Addition Nodes:** Represented by the symbol "+". These nodes take two inputs and perform addition.

* **Root Node:** The topmost node, also an addition node, representing the final result of the circuit.

* **Label:** "arithmetic circuit (AC)" located at the bottom center of the diagram.

### Detailed Analysis / Content Details

The diagram can be described as follows, starting from the bottom and moving upwards:

1. **Level 1 (Leaf Nodes):** The bottom row consists of 12 variables: θ<sub>xu</sub>, λ<sub>x</sub>, x<sub>r|a</sub>, θ<sub>r|u</sub>, λ<sub>x</sub>, x<sub>r|a</sub>, θ<sub>yu</sub>, λ<sub>y</sub>, y<sub>r|a</sub>, θ<sub>g|u</sub>, λ<sub>g</sub>, g<sub>r|a</sub>.

2. **Level 2:** Six multiplication nodes, each taking two leaf nodes as input.

* θ<sub>xu</sub> * λ<sub>x</sub>

* λ<sub>x</sub> * x<sub>r|a</sub>

* θ<sub>r|u</sub> * λ<sub>x</sub>

* λ<sub>x</sub> * x<sub>r|a</sub>

* θ<sub>yu</sub> * λ<sub>y</sub>

* λ<sub>y</sub> * y<sub>r|a</sub>

* θ<sub>g|u</sub> * λ<sub>g</sub>

* λ<sub>g</sub> * g<sub>r|a</sub>

3. **Level 3:** Two addition nodes, each taking two multiplication nodes as input.

* (θ<sub>xu</sub> * λ<sub>x</sub>) + (λ<sub>x</sub> * x<sub>r|a</sub>)

* (θ<sub>r|u</sub> * λ<sub>x</sub>) + (λ<sub>x</sub> * x<sub>r|a</sub>)

* (θ<sub>yu</sub> * λ<sub>y</sub>) + (λ<sub>y</sub> * y<sub>r|a</sub>)

* (θ<sub>g|u</sub> * λ<sub>g</sub>) + (λ<sub>g</sub> * g<sub>r|a</sub>)

4. **Level 4:** Two multiplication nodes, each taking two addition nodes as input.

* [(θ<sub>xu</sub> * λ<sub>x</sub>) + (λ<sub>x</sub> * x<sub>r|a</sub>)] * [(θ<sub>r|u</sub> * λ<sub>x</sub>) + (λ<sub>x</sub> * x<sub>r|a</sub>)]

* [(θ<sub>yu</sub> * λ<sub>y</sub>) + (λ<sub>y</sub> * y<sub>r|a</sub>)] * [(θ<sub>g|u</sub> * λ<sub>g</sub>) + (λ<sub>g</sub> * g<sub>r|a</sub>)]

5. **Level 5 (Root Node):** A final addition node taking the outputs of the two multiplication nodes as input.

* [(θ<sub>xu</sub> * λ<sub>x</sub>) + (λ<sub>x</sub> * x<sub>r|a</sub>)] * [(θ<sub>r|u</sub> * λ<sub>x</sub>) + (λ<sub>x</sub> * x<sub>r|a</sub>)] + [(θ<sub>yu</sub> * λ<sub>y</sub>) + (λ<sub>y</sub> * y<sub>r|a</sub>)] * [(θ<sub>g|u</sub> * λ<sub>g</sub>) + (λ<sub>g</sub> * g<sub>r|a</sub>)]

### Key Observations

The circuit is symmetrical in its structure, with two identical branches converging at the root. The use of multiplication and addition suggests that the circuit is designed to compute a product of sums or a similar arithmetic expression. The variables with subscripts "r|a" likely represent some form of conditional or masked values.

### Interpretation

This diagram represents a computational model for an arithmetic operation. The circuit's structure suggests it's performing a weighted sum of products. The variables θ, λ, x, y, and g likely represent parameters, weights, and input values, respectively. The "r|a" notation could indicate a conditional application of the input value, potentially representing a routing or activation mechanism. The overall purpose of the circuit is to compute a complex function based on these inputs and weights. The diagram is a visual representation of a mathematical expression, and understanding the meaning of the variables is crucial to interpreting the circuit's functionality. The circuit could be part of a larger system, such as a neural network or a signal processing algorithm.