## Diagram: Autoregressive Decoding and Verification Process

### Overview

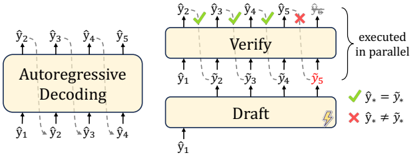

The diagram illustrates a multi-stage computational process involving autoregressive decoding, parallel verification, and draft finalization. It uses directional arrows, checkmarks (✓), and X marks to represent data flow, validation outcomes, and error states.

### Components/Axes

1. **Main Blocks**:

- **Autoregressive Decoding**: A rectangular block with dashed upward arrows labeled `ŷ₁` to `ŷ₅` (predicted outputs).

- **Verify**: A rectangular block with solid arrows from `ŷ₁` to `ŷ₅`, annotated with green checkmarks (✓) for matches and a red X for mismatch.

- **Draft**: A rectangular block with a lightning bolt symbol, receiving inputs from the Verify block.

2. **Legend**:

- Green checkmark (✓): `ŷᵢ = ŷᵢ` (correct match)

- Red X: `ŷᵢ ≠ ŷᵢ` (mismatch/error)

3. **Flow Indicators**:

- Dashed arrows: Initial autoregressive decoding outputs.

- Solid arrows: Verification phase.

- Lightning bolt: Finalization/drafting step.

### Detailed Analysis

- **Autoregressive Decoding**:

- Generates sequential predictions `ŷ₁` to `ŷ₅` (left-to-right flow).

- Dashed arrows suggest iterative or probabilistic generation.

- **Verification**:

- Parallel execution of validation checks (indicated by "executed in parallel" annotation).

- `ŷ₂`, `ŷ₃`, `ŷ₄` pass validation (✓), while `ŷ₅` fails (✗).

- `ŷ₁` is excluded from verification (grayed-out arrow).

- **Draft Finalization**:

- Only validated outputs (`ŷ₂`, `ŷ₃`, `ŷ₄`) propagate to the Draft stage.

- Lightning bolt symbolizes irreversible commitment to final outputs.

### Key Observations

1. **Parallel Verification**: All outputs except `ŷ₁` are validated simultaneously, optimizing throughput.

2. **Error Propagation**: The single mismatch (`ŷ₅`) is isolated, preventing cascading failures.

3. **Selective Finalization**: Only validated outputs (`ŷ₂`, `ŷ₃`, `ŷ₄`) proceed to drafting, ensuring quality control.

### Interpretation

This diagram represents a **robust autoregressive pipeline** with built-in quality assurance. The parallel verification step enables efficient error detection, while the Draft stage acts as a gatekeeper for final outputs. The exclusion of `ŷ₁` from verification suggests it may represent an initial anchor or fixed reference point. The red X on `ŷ₅` highlights the system's ability to identify and reject erroneous predictions, critical for applications like text generation or code synthesis where errors propagate catastrophically. The lightning bolt in the Draft stage implies a "commit to memory" operation, possibly indicating state persistence or output finalization in hardware-accelerated systems.