## System Diagram: FPGA Architecture for Deep Learning

### Overview

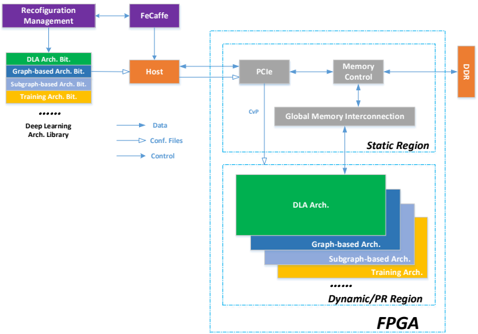

The image presents a system diagram illustrating an FPGA architecture designed for deep learning applications. It highlights the interaction between different components, including reconfiguration management, a host processor, memory control, and a deep learning architecture library. The diagram distinguishes between static and dynamic/PR (Partial Reconfiguration) regions within the FPGA.

### Components/Axes

* **Top-Left:** "Reconfiguration Management" (purple block) connected to "FeCaffe" (gray block) via a data flow arrow.

* **Left:** "Deep Learning Arch. Library" consisting of stacked blocks:

* "DLA Arch. Bit." (green)

* "Graph-based Arch. Bit." (blue)

* "Subgraph-based Arch. Bit." (light blue)

* "Training Arch. Bit." (yellow)

* **Center:** "Host" (orange block) connected to the "Deep Learning Arch. Library" via data flow arrows.

* **Top-Right:** "DDR" (orange block).

* **Center-Right:** "Static Region" (enclosed in a dashed blue box) containing:

* "PCIe" (gray block)

* "Memory Control" (gray block)

* "Global Memory Interconnection" (gray block)

* **Bottom-Center:** "Dynamic/PR Region" (enclosed in a dashed blue box) containing stacked blocks:

* "DLA Arch." (green)

* "Graph-based Arch." (blue)

* "Subgraph-based Arch." (light blue)

* "Training Arch." (yellow)

* **Bottom:** "FPGA" label.

* **Data Flow Arrows:**

* "Data" (solid line with arrowhead)

* "Conf. Files" (dashed line with arrowhead)

* "Control" (dotted line with arrowhead)

### Detailed Analysis

* **Reconfiguration Management and FeCaffe:** The "Reconfiguration Management" block feeds into the "FeCaffe" block, suggesting a process of managing and configuring the FPGA.

* **Deep Learning Arch. Library:** The library contains different architectural bitstreams for deep learning tasks, including DLA (Deep Learning Accelerator), graph-based, subgraph-based, and training architectures.

* **Host Interaction:** The "Host" processor interacts with both the "Deep Learning Arch. Library" and the "Static Region" of the FPGA.

* **Static Region:** The "Static Region" includes PCIe, Memory Control, and Global Memory Interconnection, indicating the fixed infrastructure for communication and memory access. "CvP" is a small label and arrow connecting PCIe to Global Memory Interconnection.

* **Dynamic/PR Region:** The "Dynamic/PR Region" contains the actual deep learning architectures that can be dynamically reconfigured.

* **Data Flow:** The arrows indicate the flow of data, configuration files, and control signals between the different components.

### Key Observations

* The architecture separates static and dynamic regions within the FPGA, allowing for partial reconfiguration of the deep learning accelerators.

* The "Deep Learning Arch. Library" provides a collection of pre-designed architectures for different deep learning tasks.

* The "Host" processor acts as a central control point for managing the FPGA and interacting with the deep learning accelerators.

### Interpretation

The diagram illustrates a flexible FPGA-based architecture for deep learning. The separation of static and dynamic regions enables partial reconfiguration, allowing for efficient utilization of FPGA resources and adaptation to different deep learning workloads. The "Deep Learning Arch. Library" provides a modular approach to deep learning acceleration, enabling developers to select and deploy the most appropriate architecture for their specific needs. The "Host" processor plays a crucial role in managing the FPGA and coordinating the execution of deep learning tasks. The presence of "FeCaffe" suggests integration with the Caffe deep learning framework.