## System Architecture Diagram: FPGA-Based Reconfigurable Deep Learning Accelerator

### Overview

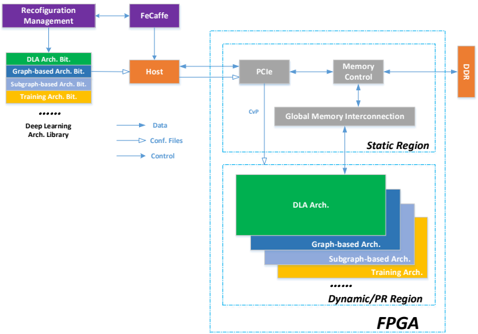

This image is a technical system architecture diagram illustrating a reconfigurable computing platform for deep learning workloads. It depicts a host system interacting with an FPGA (Field-Programmable Gate Array) that is partitioned into static and dynamic regions. The dynamic region can be reconfigured with different deep learning architecture blocks managed by a host-side library. The diagram uses color-coded blocks and labeled arrows to show data, configuration, and control flow.

### Components/Axes

The diagram is organized into three primary spatial regions:

**1. Host-Side Components (Left & Center):**

* **Reconfiguration Management** (Purple box, top-left): Manages the dynamic reconfiguration process.

* **FeCaffe** (Light blue box, top-center): Likely a framework or tool for managing deep learning models (name suggests a Caffe derivative).

* **Deep Learning Arch. Library** (Dark blue box, bottom-left): A repository containing multiple architecture blocks.

* **DLA Arch. Blk.** (Green box)

* **Graph-based Arch. Blk.** (Blue box)

* **Training Arch. Blk.** (Orange box)

* **...** (Ellipsis indicating additional blocks)

* **Host** (Orange box, center): The central processing unit that orchestrates operations, sends data, and issues control commands.

**2. FPGA Device (Right, within large dashed box):**

The FPGA is divided into two main regions:

* **Static Region** (Top half of FPGA box): Contains fixed, non-reconfigurable hardware logic.

* **PCIe** (Grey box): Peripheral Component Interconnect Express interface for host communication.

* **Memory Control** (Grey box): Manages memory access.

* **Global Memory Interconnection** (Grey box): Network-on-chip for memory access.

* **DDR4** (Orange vertical box, far right): External Double Data Rate 4 memory.

* **Dynamic/PR Region** (Bottom half of FPGA box): The Partial Reconfiguration region where different accelerator architectures can be loaded at runtime.

* **DLA Arch.** (Green box, top of stack)

* **Graph-based Arch.** (Blue box)

* **Subgraph-based Arch.** (Light blue box)

* **Training Arch.** (Orange box)

* **...** (Ellipsis indicating additional architectures)

**3. Legend (Center-left):**

* **Solid Blue Arrow**: Data

* **Dashed Blue Arrow**: Conf. Files (Configuration Files)

* **Dotted Blue Arrow**: Control

### Detailed Analysis

**Component Relationships and Flow:**

1. **Configuration Flow:** The `Reconfiguration Management` block sends configuration files (dashed arrows) to the `Host` and the `FeCaffe` framework. The `Host` then sends configuration files to the FPGA's `PCIe` block, which loads the appropriate architecture into the `Dynamic/PR Region`.

2. **Data Flow:** The `Host` sends data (solid arrows) to the FPGA via `PCIe`. Within the FPGA, data flows from `PCIe` to `Memory Control`, then through the `Global Memory Interconnection` to the active architecture in the `Dynamic/PR Region` (e.g., `DLA Arch.`). Processed data can be stored in or retrieved from `DDR4` memory.

3. **Control Flow:** The `Host` issues control commands (dotted arrows) to the `Reconfiguration Management` block and directly to the FPGA's `PCIe` interface to manage operations.

4. **Architecture Loading:** The `Deep Learning Arch. Library` provides the source architecture blocks (`DLA Arch. Blk.`, etc.). These are presumably compiled and sent by the `Host` to be instantiated in the FPGA's `Dynamic/PR Region`, creating a corresponding hardware accelerator (`DLA Arch.`, etc.).

**Spatial Grounding:**

* The **Legend** is positioned in the center-left, between the Host Library and the Host block.

* The **FPGA** box occupies the entire right half of the diagram.

* Within the FPGA, the **Static Region** is in the upper portion, and the **Dynamic/PR Region** is in the lower portion.

* The **DDR4** memory is positioned on the far right edge, connected to the Static Region's memory control logic.

### Key Observations

* **Reconfigurability:** The core concept is the separation of the FPGA into a static region (fixed infrastructure) and a dynamic region (swappable accelerators). This allows the same hardware to be optimized for different deep learning tasks (inference, graph processing, training) by loading different "Arch." blocks.

* **Host-Centric Control:** The `Host` is the central coordinator, managing both data movement and the reconfiguration process via dedicated management blocks (`Reconfiguration Management`, `FeCaffe`).

* **Hierarchical Memory:** The architecture shows a clear memory hierarchy from the Host's memory, through PCIe, to the FPGA's internal interconnection, and finally to external DDR4.

* **Abstraction:** The library on the host side abstracts the hardware architectures (`DLA Arch. Blk.`), which are then realized as physical circuits in the FPGA's dynamic region (`DLA Arch.`).

### Interpretation

This diagram represents a **high-performance, flexible computing system** designed for deep learning. The key innovation is the use of **FPGA Partial Reconfiguration (PR)** to create a hardware platform that can morph its circuitry to match the specific computational pattern of different neural network types (e.g., standard DNNs, graph-based models) or phases (training vs. inference).

The system's value proposition is **efficiency and adaptability**. Instead of using fixed hardware (like a GPU) that may be suboptimal for certain tasks, or multiple dedicated chips, this architecture allows a single FPGA to be time-multiplexed across various workloads, potentially offering better performance-per-watt for specialized tasks. The `FeCaffe` and `Reconfiguration Management` blocks are critical software layers that hide the complexity of hardware reconfiguration from the end-user, making the system practical. The explicit separation of configuration, control, and data paths is a hallmark of a well-designed, high-throughput system where management operations do not interfere with the primary data processing pipeline.