TECHNICAL ASSET FINGERPRINT

311c0478b6c50307eb80169d

Click to view fullscreen

Press ESC or click to close

FOUND IN PAPERS

EXPERT: gemini-3-flash-free VERSION 1

RUNTIME: google-free/gemini-3-flash-preview

INTEL_VERIFIED

## Diagram Type: Architectural Flow Diagram of an Executing Machine

### Overview

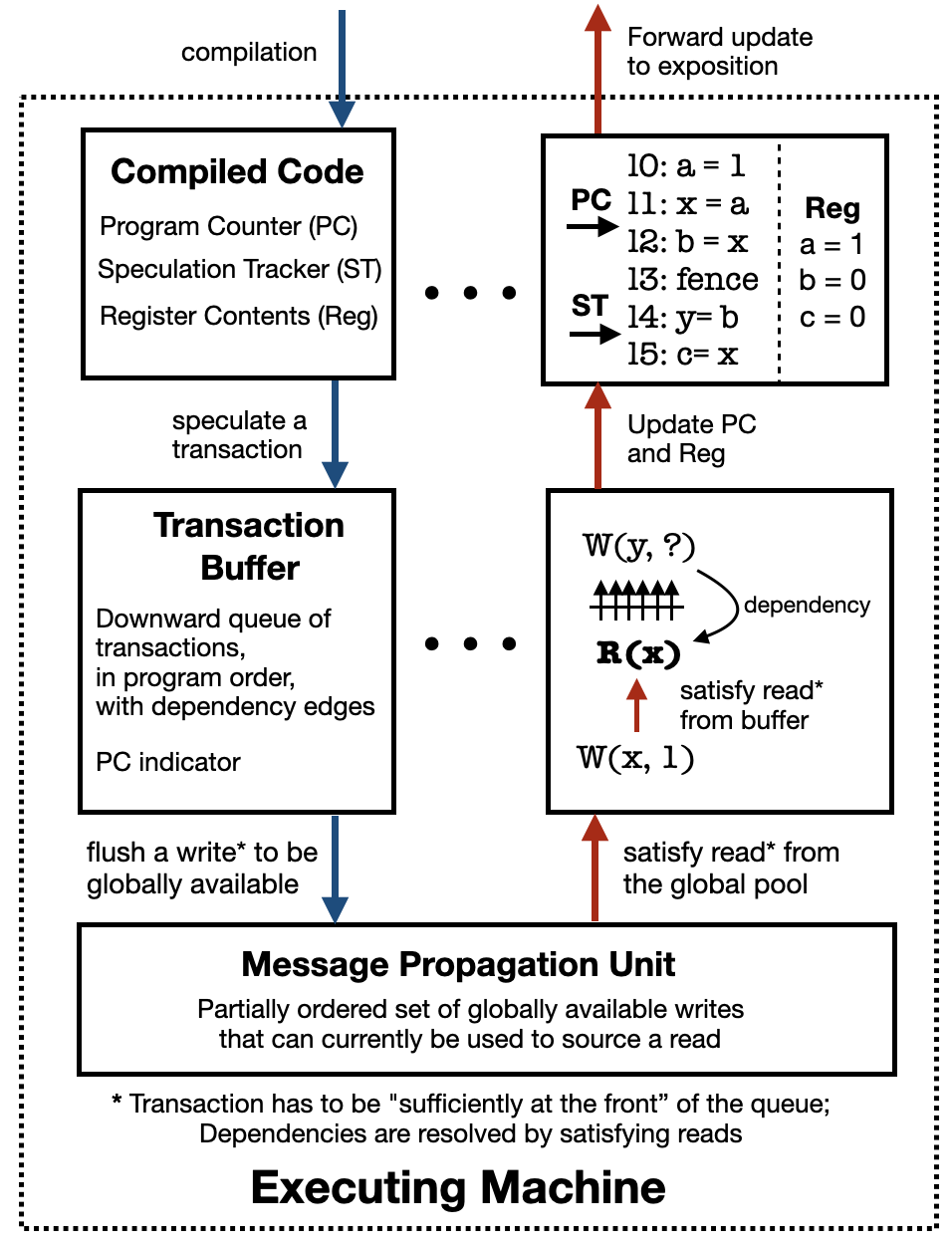

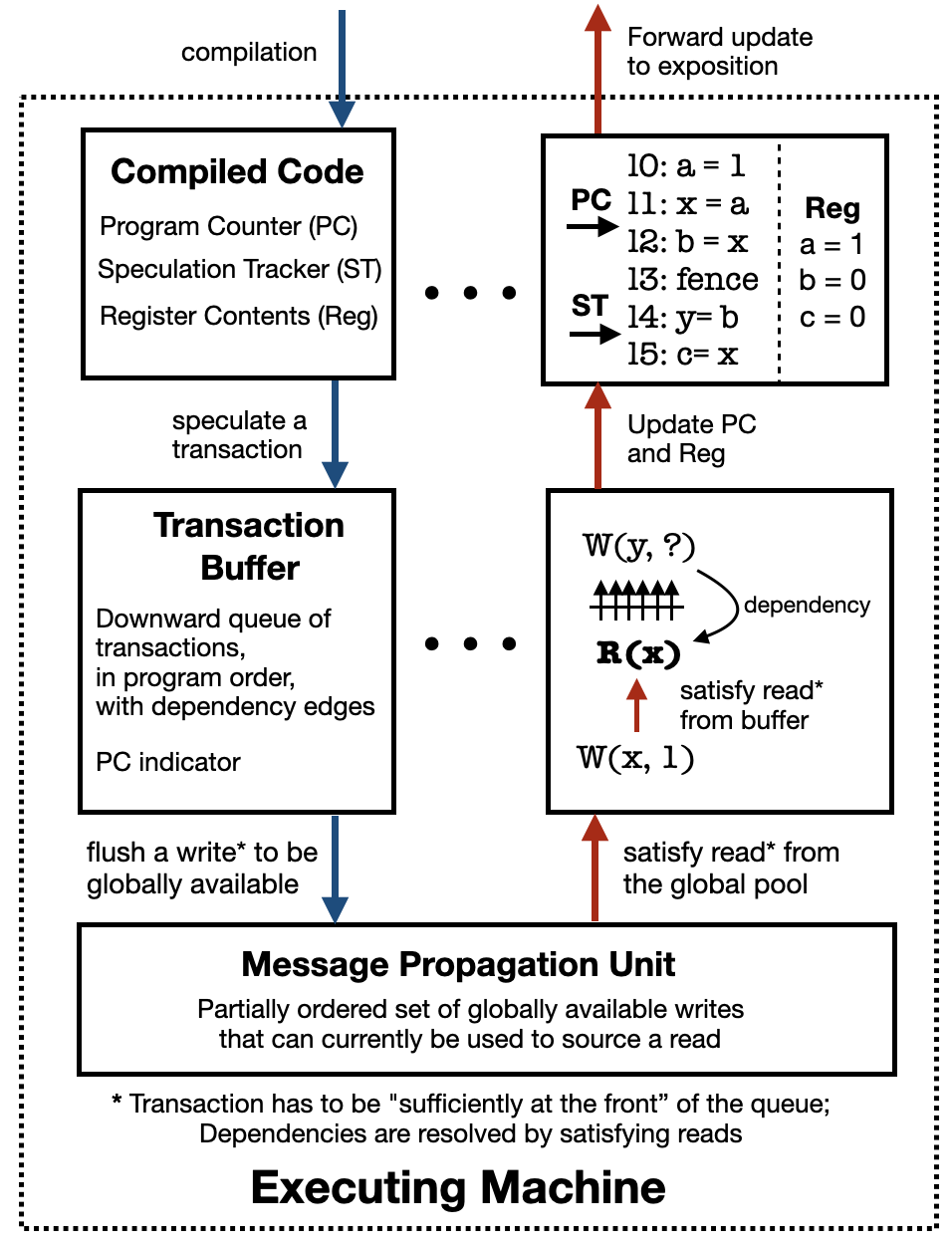

This diagram illustrates the internal architecture and operational flow of an "Executing Machine," likely representing a formal model for speculative execution and memory consistency. The system is divided into two primary vertical paths: a downward flow (blue arrows) representing the speculative issuance of instructions and an upward flow (red arrows) representing the resolution of dependencies and the commitment of state. The entire process is contained within a dashed boundary labeled "Executing Machine."

### Components/Axes

The diagram is organized into three horizontal layers and two vertical columns, with a global unit at the bottom.

* **Left Column (Speculative Path):**

* **Top-Left Block ("Compiled Code"):** Contains the static program state, including the Program Counter (PC), Speculation Tracker (ST), and Register Contents (Reg).

* **Middle-Left Block ("Transaction Buffer"):** A queue-based structure that holds transactions in program order, including dependency edges and a PC indicator.

* **Right Column (Execution/Resolution Path):**

* **Top-Right Block (State/Code View):** Shows a specific code snippet with pointers for the PC and ST, alongside current register values.

* **Middle-Right Block (Dependency Resolution):** Illustrates the interaction between Read (R) and Write (W) operations and how dependencies are satisfied.

* **Bottom Unit:**

* **"Message Propagation Unit":** A shared space for globally available writes.

* **Flow Indicators:**

* **Blue Arrows (Downward):** Represent the progression from compilation to speculation and finally to flushing writes.

* **Red Arrows (Upward):** Represent the progression from satisfying reads from the global pool to updating the architectural state and forwarding updates.

* **Legend/Notes (Bottom):**

* An asterisk (*) note explains constraints on transactions and dependency resolution.

---

### Content Details

#### 1. Top Layer: Code and State

* **Left Side:** Labeled **"Compiled Code"**. Lists components:

* Program Counter (PC)

* Speculation Tracker (ST)

* Register Contents (Reg)

* **Right Side:** Displays a code execution snapshot:

* **Code Snippet:**

* `10: a = 1`

* `11: x = a` (Indicated by **PC** arrow)

* `12: b = x`

* `13: fence`

* `14: y = b` (Indicated by **ST** arrow)

* `15: c = x`

* **Registers (Reg):**

* `a = 1`

* `b = 0`

* `c = 0`

* **Flow:** A blue arrow labeled **"compilation"** enters the top-left. A red arrow labeled **"Forward update to exposition"** exits the top-right.

#### 2. Middle Layer: Buffering and Dependencies

* **Left Side:** Labeled **"Transaction Buffer"**.

* **Description:** "Downward queue of transactions, in program order, with dependency edges. PC indicator."

* **Right Side:** Operational logic for memory access.

* **Operations:** Shows `W(y, ?)` at the top, `R(x)` in the middle, and `W(x, 1)` at the bottom.

* **Visuals:** A curved arrow labeled **"dependency"** connects `W(y, ?)` to `R(x)`. A horizontal line with vertical comb-like marks sits between them.

* **Internal Flow:** A red arrow points from `W(x, 1)` to `R(x)`, labeled **"satisfy read* from buffer"**.

* **Flow:**

* Blue arrow from top-left to middle-left: **"speculate a transaction"**.

* Red arrow from middle-right to top-right: **"Update PC and Reg"**.

#### 3. Bottom Layer: Global Propagation

* **Block Title:** **"Message Propagation Unit"**

* **Description:** "Partially ordered set of globally available writes that can currently be used to source a read."

* **Flow:**

* Blue arrow from middle-left to bottom: **"flush a write* to be globally available"**.

* Red arrow from bottom to middle-right: **"satisfy read* from the global pool"**.

#### 4. Footer Notes

* "* Transaction has to be 'sufficiently at the front' of the queue; Dependencies are resolved by satisfying reads"

* **Main Label:** **Executing Machine** (Centered at the bottom).

---

### Key Observations

* **Speculation Gap:** The **PC** is at line 11, but the **ST** (Speculation Tracker) has already reached line 14. This indicates the machine is speculating three instructions ahead of the current architectural program counter.

* **Dependency Handling:** The middle-right block shows that a read `R(x)` can be satisfied locally from the buffer (by `W(x, 1)`) before it ever needs to reach the global Message Propagation Unit.

* **Ordering:** The Transaction Buffer maintains "program order," but the Message Propagation Unit is a "partially ordered set," suggesting a relaxed memory model where writes may become globally visible in a different order than they were issued, subject to the "flush" constraints.

---

### Interpretation

This diagram describes a **Speculative Out-of-Order Execution Model** with a focus on memory consistency.

1. **Speculative Execution:** The separation of PC and ST shows that the machine "guesses" or pre-fetches instructions (the blue path) into a Transaction Buffer. This allows the processor to work on instructions before it is certain they should execute (e.g., before a previous branch is resolved).

2. **Memory Renaming/Buffering:** The "Transaction Buffer" acts similarly to a Load/Store Queue or Reorder Buffer. It allows the machine to satisfy a read (`R(x)`) from a local, pending write (`W(x, 1)`)—a technique known as **store-to-load forwarding**.

3. **Commitment and Visibility:** The red path represents the "retirement" or "commitment" phase. An instruction only updates the architectural state (PC and Reg) and becomes "globally available" (via the Message Propagation Unit) once it is no longer speculative and its dependencies are resolved.

4. **The "Fence" Instruction:** Line 13 in the code is a `fence`. In this model, a fence likely acts as a barrier that prevents the ST from moving too far ahead or forces the flushing of the Transaction Buffer to the Message Propagation Unit to ensure strict ordering for subsequent operations (like `y = b` at line 14).

5. **Peircean Analysis:** The "dots" (...) between the left and right columns suggest a mapping or a "mirroring" of state. The left side is the *intent* (what we plan to do speculatively), and the right side is the *realization* (how those plans are actually resolved and committed). The "Executing Machine" is thus a system that manages the tension between high-speed speculation and the requirement for consistent, ordered results.

DECODING INTELLIGENCE...