\n

## Diagram: Execution Machine Architecture

### Overview

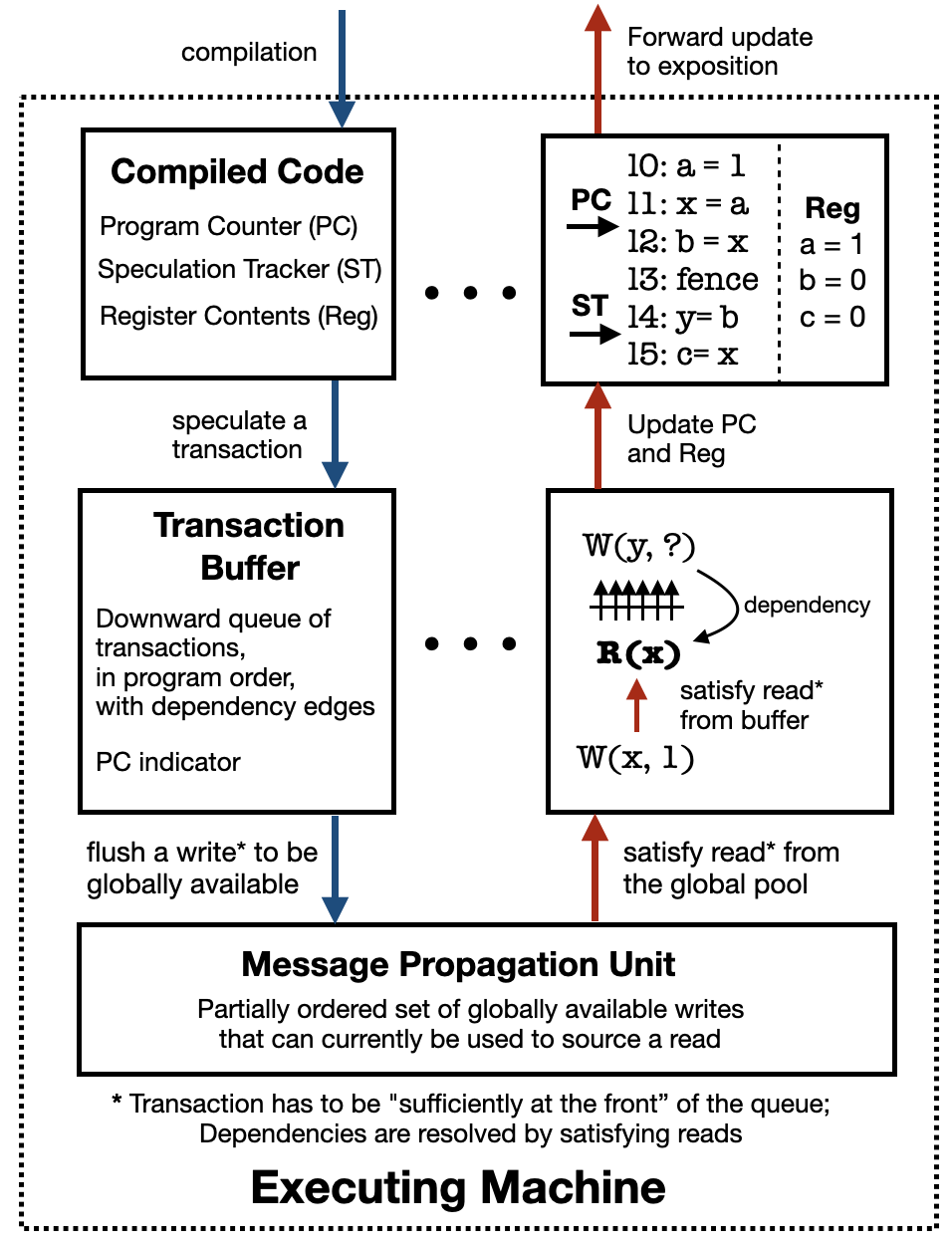

This diagram illustrates the architecture of an executing machine, detailing the flow of instructions from compiled code through a transaction buffer and message propagation unit to register updates. It depicts a system designed for speculative execution and dependency tracking. The diagram is segmented into four main areas: Compiled Code, Transaction Buffer, Message Propagation Unit, and Executing Machine. Arrows indicate the direction of data flow and control.

### Components/Axes

The diagram contains the following components:

* **Compiled Code:** Includes Program Counter (PC), Speculation Tracker (ST), and Register Contents (Reg).

* **Transaction Buffer:** A downward queue of transactions in program order, with dependency edges. Includes a PC indicator.

* **Message Propagation Unit:** A partially ordered set of globally available writes.

* **Executing Machine:** The overall system.

* **Data Flow Arrows:** Represent the movement of instructions and data.

* **Text Blocks:** Instructions and descriptions within each component.

* **Registers:** Displayed with initial values (a=1, b=0, c=0).

### Detailed Analysis or Content Details

**1. Compiled Code (Top-Left):**

* **Program Counter (PC):** Indicates the current instruction being processed.

* **Speculation Tracker (ST):** Tracks speculative transactions.

* **Register Contents (Reg):** Shows the current values of registers: a=1, b=0, c=0.

* **Instruction List:** A list of instructions is shown, numbered 10-15:

* 10: a = 1

* 11: x = a

* 12: b = x

* 13: fence

* 14: y = b

* 15: c = x

**2. Transaction Buffer (Center-Left):**

* Described as a "Downward queue of transactions, in program order, with dependency edges."

* Contains a "PC indicator."

* The action "speculate a transaction" is indicated by an arrow entering the buffer.

**3. Message Propagation Unit (Bottom-Center):**

* Described as a "Partially ordered set of globally available writes that can currently be used to source a read."

* Includes operations:

* W(y, ?) - Write to y with an unknown value.

* W(x, 1) - Write 1 to x.

* R(x) - Read from x.

* An arrow labeled "flush a write* to be globally available" enters the unit.

* An arrow labeled "satisfy read* from the global pool" exits the unit.

* An arrow labeled "satisfy read* from buffer" exits the unit.

* An arrow labeled "dependency" connects R(x) to W(x,1).

**4. Executing Machine (Bottom):**

* The overall system encompassing the other components.

* Includes an "Update PC and Reg" block, receiving input from the Message Propagation Unit.

**5. External Inputs/Outputs:**

* "Compilation" arrow enters the Compiled Code section from the top.

* "Forward update to exposition" arrow exits the Compiled Code section from the top.

**6. Footnotes:**

* "* Transaction has to be 'sufficiently at the front' of the queue;"

* "Dependencies are resolved by satisfying reads"

### Key Observations

* The system utilizes speculative execution, as indicated by the "Speculation Tracker" and the "speculate a transaction" arrow.

* Dependencies between transactions are explicitly represented by edges within the Transaction Buffer and the dependency arrow in the Message Propagation Unit.

* The Message Propagation Unit acts as an intermediary between the Transaction Buffer and the register updates, ensuring data consistency.

* The "fence" instruction (instruction 13) likely serves as a synchronization point.

* The diagram emphasizes the flow of data and control, highlighting the stages of instruction processing.

### Interpretation

This diagram depicts a sophisticated execution model likely used in a high-performance processor or a system designed for parallel processing. The use of a Transaction Buffer and Message Propagation Unit suggests an attempt to mitigate the performance bottlenecks associated with traditional sequential execution. Speculative execution allows the system to proceed with instructions before their dependencies are fully resolved, potentially improving performance. However, the Speculation Tracker and dependency tracking mechanisms are crucial for ensuring correctness in the event of mis-speculation.

The "fence" instruction is a key element in maintaining memory consistency, preventing out-of-order execution from violating data dependencies. The Message Propagation Unit's role in satisfying reads from both the buffer and the global pool indicates a hierarchical memory system, potentially with caching.

The diagram is a high-level architectural overview, focusing on the key components and their interactions. It doesn't delve into the specific implementation details of each component, but it provides a clear understanding of the overall system design. The annotations and footnotes provide important context, clarifying the purpose and behavior of certain elements. The diagram suggests a system optimized for handling complex dependencies and maximizing throughput through speculative execution.