## Diagram: MLIR-based Compilation Pipeline for C++ to Target ISA

### Overview

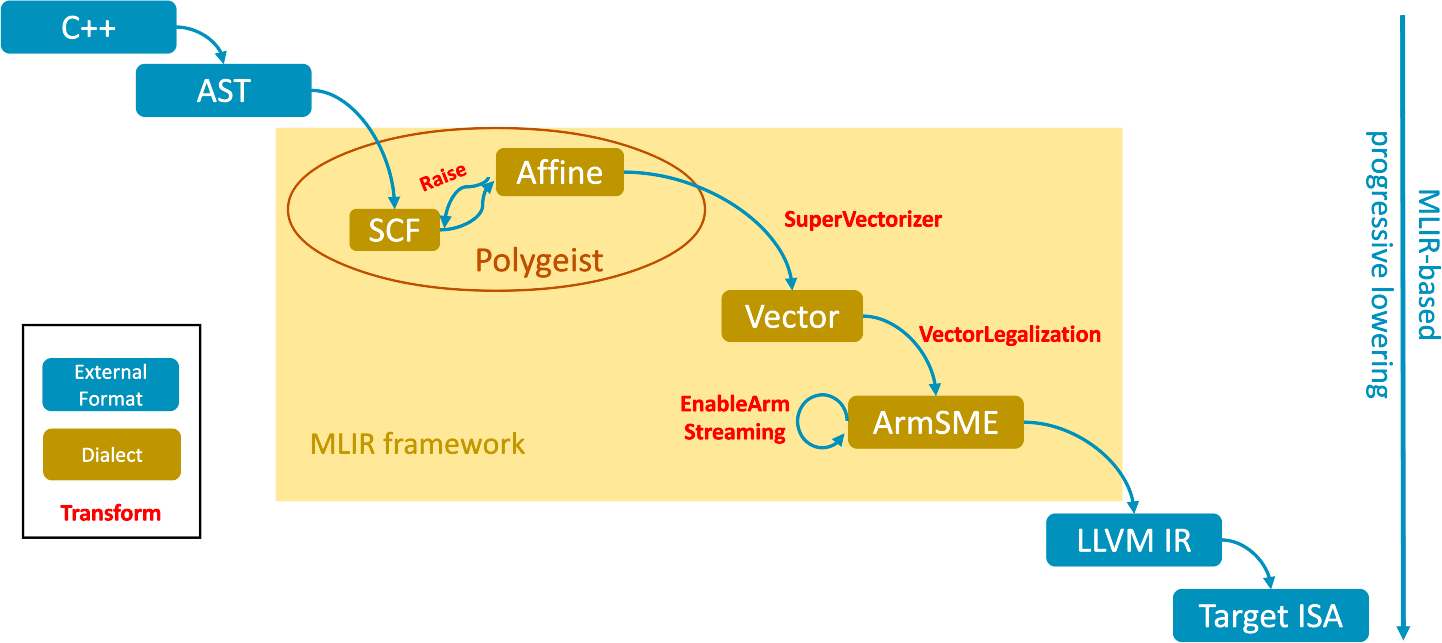

The image is a technical flowchart illustrating a compilation pipeline that transforms C++ source code into a target Instruction Set Architecture (ISA). The process is centered around the MLIR (Multi-Level Intermediate Representation) framework, showing a progressive lowering of abstraction levels. The diagram uses color-coded boxes and labeled arrows to denote different types of components and transformations.

### Components/Axes

**Legend (Bottom-Left Corner):**

* **Blue Box:** "External Format"

* **Gold Box:** "Dialect"

* **Red Text:** "Transform"

**Main Flow Components (from top-left to bottom-right):**

1. **C++** (Blue, External Format) - The starting source code.

2. **AST** (Blue, External Format) - Abstract Syntax Tree, the initial parsed representation.

3. **MLIR framework** (Large yellow background area) - The core processing environment containing:

* **SCF** (Gold, Dialect) - Structured Control Flow dialect.

* **Affine** (Gold, Dialect) - Dialect for affine operations and loop optimizations.

* **Polygeist** (Brown oval label) - Encircles SCF and Affine, indicating a related tool or phase.

* **Vector** (Gold, Dialect) - Dialect for vector operations.

* **ArmSME** (Gold, Dialect) - Dialect for Arm Scalable Matrix Extension.

4. **LLVM IR** (Blue, External Format) - LLVM Intermediate Representation.

5. **Target ISA** (Blue, External Format) - The final target-specific instruction set.

**Transform Labels (Red Text on Arrows):**

* **Raise** (on arrow from SCF to Affine)

* **SuperVectorizer** (on arrow from Affine to Vector)

* **VectorLegalization** (on arrow from Vector to ArmSME)

* **EnableArmStreaming** (on a self-referential loop arrow on ArmSME)

**Vertical Annotation (Right Edge):**

* **"MLIR-based progressive lowering"** - Describes the overall direction and nature of the pipeline.

### Detailed Analysis

The pipeline flow is as follows:

1. **C++** code is parsed into an **AST**.

2. The **AST** is lowered into the MLIR framework, entering the **SCF** dialect.

3. Within the MLIR framework, a **"Raise"** transform promotes operations from the **SCF** dialect to the **Affine** dialect. The **Polygeist** label suggests this SCF/Affine phase is managed by a tool or component of that name.

4. The **Affine** representation is processed by the **"SuperVectorizer"** transform, converting it to the **Vector** dialect.

5. The **Vector** dialect undergoes **"VectorLegalization"** to become the **ArmSME** dialect, tailored for Arm's architecture.

6. The **ArmSME** dialect has a self-loop labeled **"EnableArmStreaming"**, indicating a configuration or mode-setting transformation within that dialect.

7. Finally, the **ArmSME** dialect is lowered out of the MLIR framework to **LLVM IR**.

8. The **LLVM IR** is compiled to the final **Target ISA**.

The entire process within the yellow box is labeled as the **"MLIR framework"**, and the vertical text confirms this is a **"progressive lowering"** strategy, moving from high-level, target-agnostic representations to low-level, target-specific code.

### Key Observations

* **Color-Coding Consistency:** The diagram strictly adheres to its legend. All external formats (C++, AST, LLVM IR, Target ISA) are blue. All internal MLIR dialects (SCF, Affine, Vector, ArmSME) are gold. All transformation steps are labeled in red.

* **Spatial Organization:** The flow is diagonal from top-left to bottom-right, visually reinforcing the concept of "lowering." The MLIR framework is clearly demarcated as the central processing stage.

* **Specific Target Focus:** The pipeline is explicitly designed for Arm architectures, as evidenced by the dedicated **ArmSME** dialect and the **"EnableArmStreaming"** transform.

* **Tool Integration:** The **Polygeist** oval indicates that the initial SCF-to-Affine raising is likely handled by an external tool or specific component named Polygeist, integrated into the MLIR flow.

### Interpretation

This diagram depicts a sophisticated, modern compiler architecture for C++ code targeting Arm processors, likely for high-performance computing or machine learning workloads where matrix operations (via SME) are critical.

The pipeline demonstrates a clear separation of concerns:

1. **Frontend:** Handles language-specific parsing (C++ to AST).

2. **Middle-end (MLIR):** Performs progressive, dialect-based lowering and optimization. The use of specialized dialects (Affine for loops, Vector for SIMD, ArmSME for matrix extensions) allows for targeted optimizations at each level of abstraction. The "Raise" step is particularly interesting, as it suggests an attempt to recover higher-level structure (Affine) from a lower-level control flow representation (SCF) to enable better optimizations.

3. **Backend:** Leverages the mature LLVM ecosystem (LLVM IR) for final code generation to the target ISA.

The **"progressive lowering"** philosophy is key. Instead of a single, complex transformation from high-level to machine code, the process is broken into many smaller, well-defined steps (transforms) between intermediate representations (dialects). This makes the compiler more modular, easier to maintain, and better able to incorporate new optimizations or target-specific features (like ArmSME). The presence of the **"EnableArmStreaming"** loop suggests the compiler can dynamically configure the target hardware's operational mode, which is a advanced feature for performance tuning.