\n

## Diagram: MLIR-based Progressive Lowering

### Overview

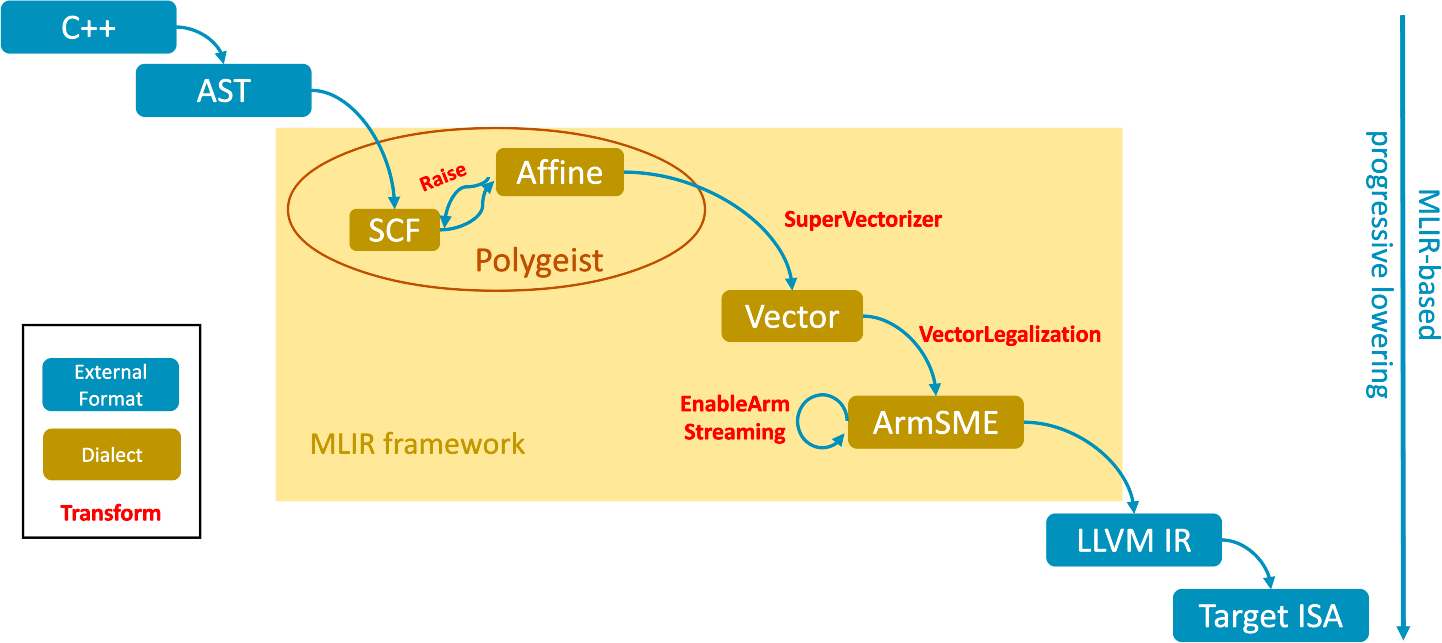

This diagram illustrates the process of progressive lowering within the MLIR (Multi-Level Intermediate Representation) framework, starting from C++ code and ending at the Target ISA (Instruction Set Architecture). It depicts a series of transformations and intermediate representations involved in compiling C++ code for a specific target architecture. The diagram uses arrows to indicate the flow of data and transformations.

### Components/Axes

The diagram consists of the following components:

* **Input:** C++ code.

* **Intermediate Representations:** AST (Abstract Syntax Tree), MLIR framework (containing dialects like SCF, Affine, Polygeist), Vector, LLVM IR.

* **Transformations:** Raise, Supervectorizer, VectorLegalization, EnableArm Streaming, ArmSME.

* **Output:** Target ISA.

* **Framework:** MLIR-based progressive lowering (indicated by a teal arrow on the right side).

* **External Elements:** External Format, Dialect, Transform (represented as a red box on the left side).

### Detailed Analysis or Content Details

The diagram shows a flow starting from the top and moving downwards.

1. **C++ to AST:** C++ code is transformed into an Abstract Syntax Tree (AST), represented by a light blue oval.

2. **AST to MLIR Framework:** The AST is then processed within the MLIR framework, a large yellow rectangle.

3. **MLIR Dialects & Transformations:** Within the MLIR framework, several dialects and transformations are applied:

* **SCF (System of Control Flow):** A yellow oval with a curved arrow pointing to "Raise".

* **Affine:** A yellow oval with a curved arrow pointing to "Raise".

* **Polygeist:** A yellow oval.

* **Raise:** A label on a curved arrow connecting SCF and Affine.

* **Supervectorizer:** A yellow rectangle connected to the MLIR framework.

* **Vector:** A yellow rectangle connected to the Supervectorizer and VectorLegalization.

* **VectorLegalization:** A label on an arrow connecting Vector to EnableArm Streaming.

* **EnableArm Streaming:** A yellow oval.

* **ArmSME:** A yellow oval connected to EnableArm Streaming.

4. **MLIR to LLVM IR:** The MLIR framework outputs LLVM IR (Intermediate Representation).

5. **LLVM IR to Target ISA:** Finally, LLVM IR is lowered to the Target ISA.

6. **External Elements:** A red box on the left side contains "External Format", "Dialect", and "Transform". These appear to represent inputs or considerations for the MLIR framework.

### Key Observations

* The diagram emphasizes a progressive lowering approach, where code is transformed through multiple intermediate representations.

* The MLIR framework serves as a central hub for these transformations.

* Specific optimizations like Supervectorization and VectorLegalization are highlighted.

* The inclusion of "EnableArm Streaming" and "ArmSME" suggests a focus on optimizing for ARM architectures.

* The diagram does not contain numerical data or precise values. It is a conceptual representation of a compilation process.

### Interpretation

The diagram illustrates a modern compiler pipeline leveraging the MLIR framework. MLIR's strength lies in its ability to represent code at various levels of abstraction, enabling optimizations tailored to specific target architectures. The progressive lowering approach allows for optimizations to be applied at each stage, ultimately resulting in more efficient code for the Target ISA. The presence of ARM-specific optimizations (EnableArm Streaming, ArmSME) indicates that this pipeline is designed to generate high-performance code for ARM processors. The "Raise" transformation suggests a process of increasing the level of abstraction within the MLIR framework, potentially for further optimization. The red box on the left indicates that external formats, dialects, and transformations can influence the MLIR framework. The diagram is a high-level overview and does not delve into the specifics of each transformation or optimization.