## Diagram: DRAM Timing Sequences - Unsafe Baseline vs. Practical Approaches

### Overview

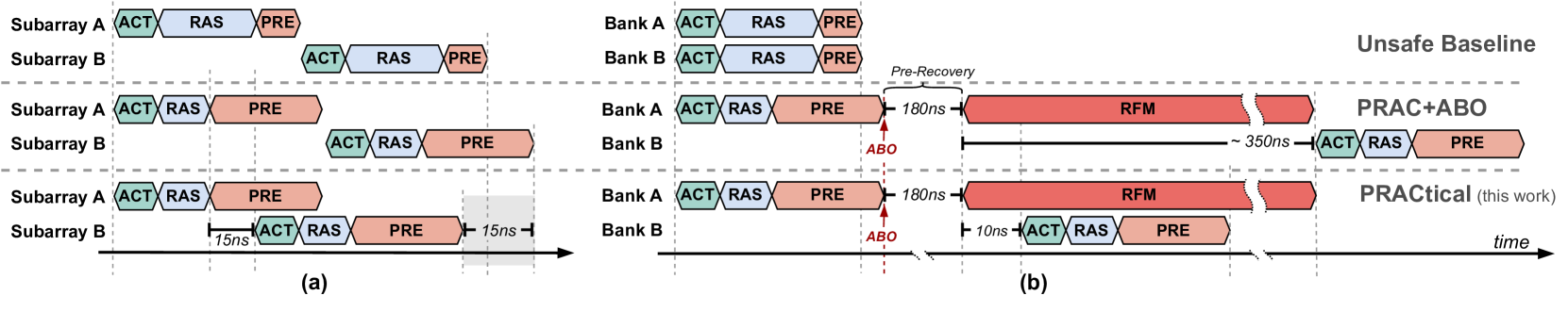

The image presents a comparative diagram illustrating DRAM timing sequences for an "Unsafe Baseline" and two "Practical" approaches: "PRAC+ABO" and "Practical (this work)". The diagram focuses on the timing of ACT (Activate), RAS (Row Address Strobe), and PRE (Precharge) commands across two memory banks (A and B) or subarrays. The diagram is split into two main sections (a) and (b), representing different scenarios.

### Components/Axes

* **Horizontal Axis:** Represents time, with increasing time moving from left to right. The scale is not explicitly defined but durations are indicated in nanoseconds (ns).

* **Vertical Axis:** Represents memory banks or subarrays. In (a), it shows Subarray A and Subarray B. In (b), it shows Bank A and Bank B.

* **Command Blocks:** Rectangular blocks labeled "ACT", "RAS", and "PRE" represent the timing of these DRAM commands. The blocks are color-coded: ACT (green), RAS (red), PRE (orange).

* **Arrows:** Arrows indicate the duration of commands and the timing relationships between them.

* **Labels:**

* "Subarray A", "Subarray B"

* "Bank A", "Bank B"

* "ACT", "RAS", "PRE"

* "Pre-Recovery"

* "RFM" (Redundant Fault Management)

* "ABO" (Address Bank Optimization)

* "Unsafe Baseline"

* "PRAC+ABO"

* "Practical (this work)"

* "15ns", "180ns", "350ns", "10ns"

### Detailed Analysis / Content Details

**Section (a) - Unsafe Baseline:**

* **Subarray A:** ACT, RAS, PRE sequence.

* **Subarray B:** ACT, RAS, PRE sequence, with a 15ns delay indicated after RAS.

* The timing between ACT and RAS is very short, and the PRE command follows closely after RAS.

**Section (b) - PRAC+ABO and Practical (this work):**

* **PRAC+ABO (Top):**

* Bank A: ACT, RAS, PRE sequence.

* Bank B: ACT, RAS, ABO sequence.

* A 180ns duration is indicated for the PRE command in Bank A.

* ABO is shown to occur after RAS in Bank B.

* RFM is shown to occur after PRE in Bank A.

* **Practical (this work) (Bottom):**

* Bank A: ACT, RAS, PRE sequence.

* Bank B: ACT, RAS, ABO sequence.

* A 180ns duration is indicated for the PRE command in Bank A.

* ABO is shown to occur after RAS in Bank B.

* RFM is shown to occur after PRE in Bank A.

* A 10ns delay is indicated after RAS in Bank B.

* A 350ns duration is indicated for the RFM command.

### Key Observations

* The "Unsafe Baseline" (a) has the shortest timing between commands, potentially leading to timing violations.

* Both "Practical" approaches (PRAC+ABO and Practical) introduce delays and additional steps (ABO, RFM) to improve reliability.

* The "PRAC+ABO" approach has a 180ns PRE command duration in Bank A, while the "Practical" approach has a 350ns RFM duration.

* The "Practical" approach introduces a 10ns delay after RAS in Bank B.

* The diagram highlights the trade-off between performance (shorter timings) and reliability (longer timings with additional steps).

### Interpretation

The diagram demonstrates the evolution of DRAM timing strategies to address reliability concerns. The "Unsafe Baseline" represents a potentially faster but less reliable approach, while the "Practical" approaches prioritize reliability by introducing delays and redundancy management (RFM). The inclusion of Address Bank Optimization (ABO) in "PRAC+ABO" suggests an attempt to mitigate the performance impact of the added delays. The differences in timing durations (180ns vs. 350ns) and the 10ns delay in the "Practical" approach indicate different optimization strategies for managing redundancy and ensuring data integrity. The diagram suggests that the "Practical (this work)" approach is a refinement of the "PRAC+ABO" approach, potentially offering a better balance between performance and reliability. The diagram is a visual representation of a technical problem and the proposed solutions, likely within the context of DRAM design or memory controller development.