TECHNICAL ASSET FINGERPRINT

4608f7b82cb8afa7377f05bf

Click to view fullscreen

Press ESC or click to close

FOUND IN PAPERS

EXPERT: healer-alpha-free VERSION 1

RUNTIME: free/openrouter/healer-alpha

INTEL_VERIFIED

\n

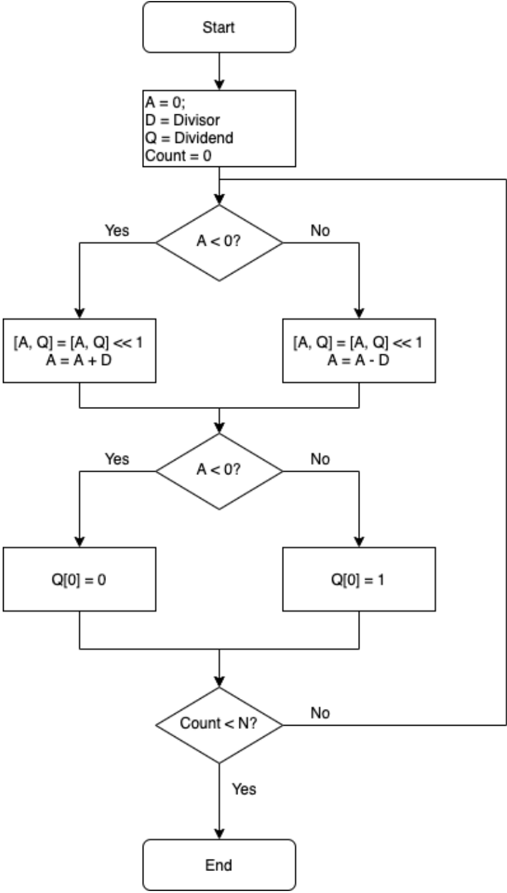

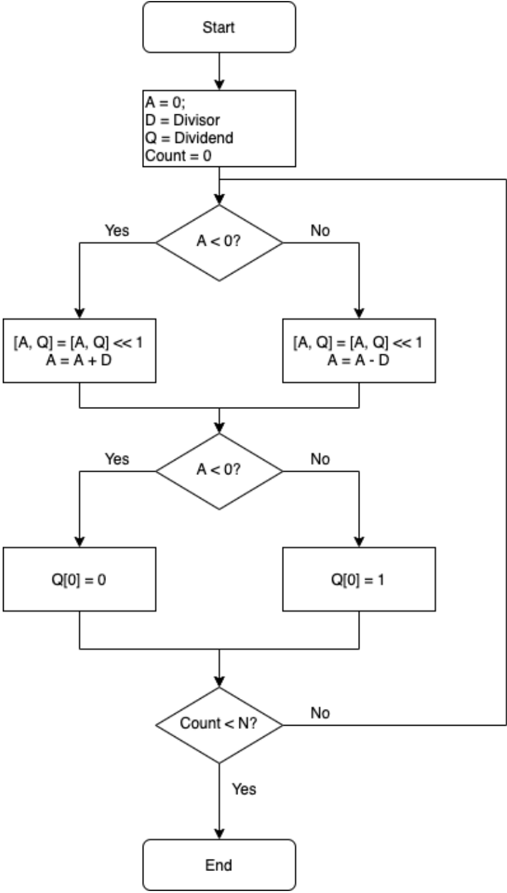

## Flowchart: Division Algorithm Process

### Overview

The image displays a flowchart representing a step-by-step algorithmic process, likely for performing division (possibly a restoring division algorithm). The flowchart uses standard symbols: rounded rectangles for start/end, rectangles for process steps, and diamonds for decision points. The flow proceeds from top to bottom with conditional branches.

### Components/Axes

The flowchart consists of the following components, listed in order of flow:

1. **Start Terminal**: A rounded rectangle at the top labeled "Start".

2. **Initialization Process Block**: A rectangle containing the initialization of variables:

* `A = 0;`

* `D = Divisor`

* `Q = Dividend`

* `Count = 0`

3. **First Decision Diamond**: A diamond labeled `A < 0?`. It has two outgoing branches:

* **Yes** branch (left)

* **No** branch (right)

4. **Process Blocks (Post First Decision)**:

* **Left (Yes) Branch Block**: A rectangle containing:

* `[A, Q] = [A, Q] << 1`

* `A = A + D`

* **Right (No) Branch Block**: A rectangle containing:

* `[A, Q] = [A, Q] << 1`

* `A = A - D`

5. **Second Decision Diamond**: A diamond labeled `A < 0?`. It has two outgoing branches:

* **Yes** branch (left)

* **No** branch (right)

6. **Process Blocks (Post Second Decision)**:

* **Left (Yes) Branch Block**: A rectangle containing `Q[0] = 0`.

* **Right (No) Branch Block**: A rectangle containing `Q[0] = 1`.

7. **Loop Decision Diamond**: A diamond labeled `Count < N?`. It has two outgoing branches:

* **No** branch (right) which loops back to the point just before the first decision diamond (`A < 0?`).

* **Yes** branch (down) which proceeds to the end.

8. **End Terminal**: A rounded rectangle at the bottom labeled "End".

### Detailed Analysis

The algorithm follows this precise sequence:

1. **Start**.

2. **Initialize**: Set accumulator `A` to 0. Load the divisor into variable `D` and the dividend into variable `Q`. Initialize a loop counter `Count` to 0.

3. **First Check**: Evaluate if `A < 0`.

* **If Yes (A is negative)**: Perform a left shift on the combined register pair `[A, Q]` by 1 bit. Then, add the divisor `D` to `A`.

* **If No (A is non-negative)**: Perform a left shift on the combined register pair `[A, Q]` by 1 bit. Then, subtract the divisor `D` from `A`.

4. **Second Check**: Evaluate if `A < 0` again.

* **If Yes (A is negative)**: Set the least significant bit of the quotient (`Q[0]`) to 0.

* **If No (A is non-negative)**: Set the least significant bit of the quotient (`Q[0]`) to 1.

5. **Loop Check**: Evaluate if the loop counter `Count` is less than a predefined number `N` (likely the number of bits in the dividend).

* **If No (Count >= N)**: The loop is complete. Follow the "No" branch back to the input of the first decision diamond (`A < 0?`). *Note: The flowchart does not show an explicit increment of `Count` within the loop body.*

* **If Yes (Count < N)**: The process is complete. Proceed to "End".

6. **End**.

### Key Observations

* **Loop Structure**: The process contains a loop that repeats until a condition (`Count < N?`) is met. The "No" branch of this condition loops back, indicating the loop continues while `Count` is *not* less than `N` (i.e., while `Count >= N`). This is an unusual loop condition and may be a point of confusion or a specific design choice.

* **Missing Increment**: The variable `Count` is initialized to 0 but there is no visible step within the loop body that increments it. For the loop to terminate, `Count` must be incremented elsewhere or `N` must be 0.

* **Dual Decision on A**: The value of `A` is checked for negativity twice in succession, with different operations performed after each check. This is characteristic of algorithms that adjust a remainder and set quotient bits accordingly.

* **Register Pair Operation**: The notation `[A, Q] << 1` suggests a combined left-shift operation on the accumulator `A` and the quotient/dividend register `Q`, which is a common operation in binary division algorithms.

### Interpretation

This flowchart depicts the control logic for a binary division algorithm, most likely a variant of the **restoring division** algorithm. Here's how the elements relate:

* **Purpose**: The algorithm computes the quotient and remainder of dividing `Q` (Dividend) by `D` (Divisor). The quotient is built bit-by-bit in `Q`, and the remainder is ultimately held in `A`.

* **Process Logic**:

1. The algorithm works by repeatedly shifting the dividend left into the accumulator (`A`) and comparing/ subtracting the divisor.

2. The first decision (`A < 0?`) and subsequent operation (add or subtract `D`) effectively perform a trial subtraction. If `A` was already negative before the shift, adding `D` compensates. If `A` was non-negative, subtracting `D` tests if the divisor fits.

3. The second decision (`A < 0?`) checks the result of the trial subtraction. The outcome determines the next bit of the quotient (`Q[0]`): 1 if the subtraction was successful (A non-negative), 0 if it failed (A negative, requiring a restore in the next cycle).

4. The loop repeats this shift-test-set process for a number of iterations (`N`), corresponding to the number of bits in the dividend.

* **Notable Anomaly/Uncertainty**: The loop control is atypical. The condition `Count < N?` leading to "Yes" for termination suggests the loop runs while `Count >= N`. Given `Count` starts at 0, this would cause immediate termination unless `N` is negative or zero. It is highly probable that the intended logic is the inverse: the loop should continue while `Count < N` (i.e., the "Yes" branch should loop back). Alternatively, the label "Yes" and "No" on the loop decision diamond may be swapped. This is a critical point for verification against the intended algorithm specification.

* **Missing Detail**: The flowchart does not specify the bit-width of the registers or the value of `N`. It also omits the step where `Count` is incremented, which is essential for the loop to progress.

In summary, the flowchart provides a clear visual representation of the decision and processing steps in a division algorithm but contains a potential logical inconsistency in its loop termination condition and omits the counter increment step.

DECODING INTELLIGENCE...