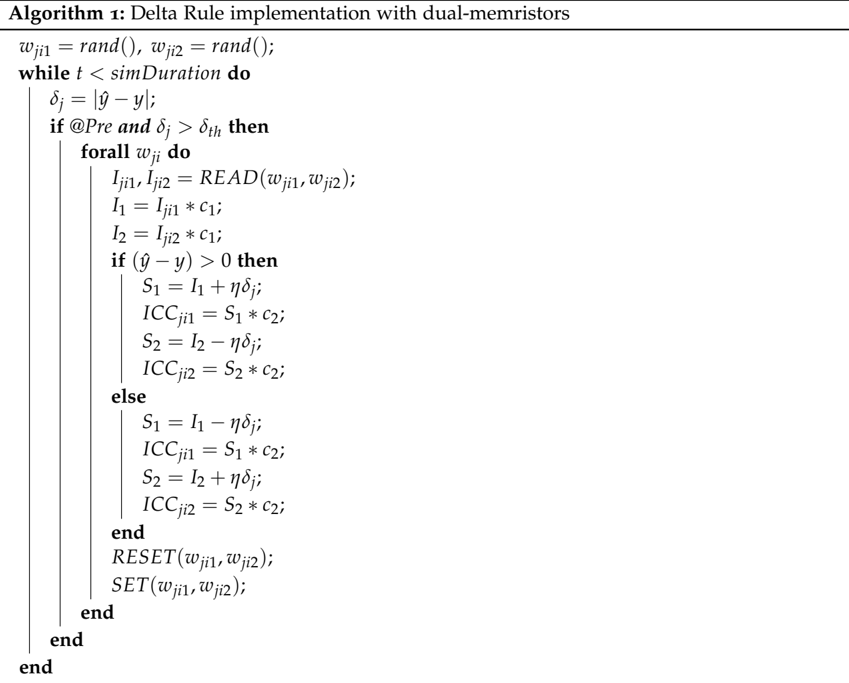

## Pseudocode: Delta Rule Implementation with Dual-Memristors

### Overview

The image contains pseudocode for implementing the Delta Rule algorithm using dual-memristors. The code structure includes variable initialization, iterative loops, conditional logic, and arithmetic operations.

### Components/Axes

- **Variables**:

- `w_ji1`, `w_ji2`: Dual-memristor weights initialized via `rand()`.

- `simDuration`: Simulation duration threshold for the `while` loop.

- `δ_j`: Error term calculated as `|ŷ - y|`.

- `I_ji1`, `I_ji2`: Intermediate current values derived from `READ(w_ji1, w_ji2)`.

- `I_1`, `I_2`: Scaled currents using constants `c_1`, `c_2`.

- `S_1`, `S_2`: Final synaptic states updated based on error sign.

- `ICC_ji1`, `ICC_ji2`: Intermediate current corrections.

- **Control Flow**:

- `while t < simDuration`: Iterates until simulation time exceeds `simDuration`.

- `if @Pre and δ_j > δ_th`: Conditional block for pre-synaptic error threshold checks.

- `for all w_ji`: Iterates over all memristor pairs.

- `if (ŷ - y) > 0`: Adjusts synaptic states based on error polarity.

- `else`: Handles negative error cases.

### Detailed Analysis

1. **Initialization**:

- `w_ji1` and `w_ji2` are randomly initialized using `rand()`.

2. **Main Loop**:

- The `while` loop runs while `t < simDuration`, simulating time-dependent updates.

3. **Error Calculation**:

- `δ_j = |ŷ - y|` computes the absolute error between predicted (`ŷ`) and actual (`y`) outputs.

4. **Pre-Synaptic Check**:

- If `@Pre` (likely a flag for pre-synaptic activation) and `δ_j > δ_th` (error exceeds threshold), the algorithm proceeds to update memristors.

5. **Current Calculation**:

- `READ(w_ji1, w_ji2)` retrieves current values from memristors.

- `I_1 = I_ji1 * c_1` and `I_2 = I_ji2 * c_2` scale currents using constants.

6. **Synaptic State Update**:

- **Positive Error (`ŷ - y > 0`)**:

- `S_1 = I_1 + ηδ_j` and `S_2 = I_2 - ηδ_j` adjust synaptic states with learning rate `η`.

- `ICC_ji1 = S_1 * c_2` and `ICC_ji2 = S_2 * c_2` compute intermediate corrections.

- **Negative Error (`ŷ - y ≤ 0`)**:

- `S_1 = I_1 - ηδ_j` and `S_2 = I_2 + ηδ_j` invert adjustment logic.

- `ICC_ji1 = S_1 * c_2` and `ICC_ji2 = S_2 * c_2` update corrections.

7. **Reset and Set Operations**:

- `RESET(w_ji1, w_ji2)` and `SET(w_ji1, w_ji2)` finalize weight updates.

### Key Observations

- **Dual-Memristor Symmetry**: The algorithm treats `w_ji1` and `w_ji2` symmetrically, with opposing adjustments based on error polarity.

- **Error-Driven Updates**: Synaptic states (`S_1`, `S_2`) and corrections (`ICC_ji1`, `ICC_ji2`) depend directly on the error term `δ_j`.

- **Thresholding**: The `@Pre` flag and `δ_th` threshold introduce conditional logic to control updates.

### Interpretation

This pseudocode models the Delta Rule for synaptic weight updates in a neural network using dual-memristors. The algorithm:

1. **Learns from Errors**: Adjusts memristor weights (`w_ji1`, `w_ji2`) proportionally to the error `δ_j`, scaled by learning rate `η`.

2. **Handles Polarity**: Positive/negative errors trigger opposite updates to `S_1` and `S_2`, mimicking biological synaptic plasticity.

3. **Scales with Constants**: Constants `c_1`, `c_2` modulate current-to-state conversions, likely representing hardware-specific parameters.

4. **Iterative Refinement**: The `while` loop ensures continuous updates until the simulation duration is reached.

The code reflects a hardware-aware implementation of the Delta Rule, emphasizing memristor-based synaptic modeling and error-driven learning.