## Logic Circuit Diagram: Two-Input Combinational Circuit

### Overview

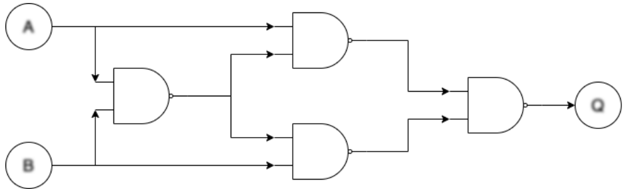

The image displays a digital logic circuit diagram with two primary inputs (A and B) and one output (Q). The circuit is composed of four logic gates interconnected by lines representing electrical connections. The diagram flows from left (inputs) to right (output).

### Components/Axes

* **Inputs:** Two circular nodes on the left side, labeled **A** (top) and **B** (bottom).

* **Output:** One circular node on the right side, labeled **Q**.

* **Logic Gates:** Four gates are present, identified by their standard symbols:

1. One **NAND gate** (AND gate shape with a circle/bubble on its output).

2. Three **AND gates** (standard D-shaped symbol without an output bubble).

* **Connections:** Lines with arrows indicate the direction of signal flow from inputs, through the gates, to the final output.

### Detailed Analysis

**Circuit Topology and Signal Flow:**

1. **Input Stage:** Input **A** splits into two paths. Input **B** also splits into two paths.

2. **First Gate (NAND):** The top path from **A** and the top path from **B** feed into the inputs of a **NAND gate**. The output of this NAND gate is `(A NAND B)` or `NOT (A AND B)`.

3. **Second Stage (Two AND Gates):**

* The output of the NAND gate splits and feeds into one input of two separate AND gates.

* The other input of the **top AND gate** comes directly from input **A**.

* The other input of the **bottom AND gate** comes directly from input **B**.

* Therefore, the top AND gate computes `A AND (A NAND B)`.

* The bottom AND gate computes `B AND (A NAND B)`.

4. **Final Stage (Output AND Gate):** The outputs from the two second-stage AND gates feed into the inputs of a final **AND gate**.

5. **Output:** The output of this final AND gate is the circuit's output, **Q**.

**Boolean Expression:**

The logical function performed by the circuit can be expressed as:

`Q = [ A · (A · B)' ] · [ B · (A · B)' ]`

Where `·` represents AND, and `'` represents NOT.

### Key Observations

* **Gate Types:** The circuit uses a mix of NAND and AND gates. The NAND gate is the only gate with an inversion bubble.

* **Signal Fan-out:** Both primary inputs (A, B) and the output of the first NAND gate are used as inputs to multiple subsequent gates.

* **Structural Symmetry:** The circuit has a symmetric structure in its second stage, with parallel paths for signals derived from A and B.

### Interpretation

This diagram represents a combinational logic circuit, meaning its output Q is determined solely by the current states of inputs A and B, with no memory or feedback loops.

**Logical Function Analysis:**

Simplifying the Boolean expression reveals the circuit's purpose:

1. Let `N = (A · B)'` (the output of the NAND gate).

2. Then `Q = (A · N) · (B · N) = A · B · N · N = A · B · N` (since `N · N = N`).

3. Substituting back: `Q = A · B · (A · B)'`.

4. This is equivalent to `Q = (A · B) · NOT(A · B)`.

5. A logical term ANDed with its own negation is always **FALSE (0)**. Therefore, `Q = 0` for all possible input combinations of A and B.

**Conclusion:**

The circuit, as drawn, implements a logic function that **always outputs a logical 0 (low signal)**, regardless of the inputs A and B. This could be:

* An intentional design for a specific application requiring a constant false output.

* A pedagogical example to demonstrate circuit analysis and Boolean simplification.

* A potential error in the diagram, where a gate type (e.g., the final AND gate) might have been intended to be an OR or XOR gate to create a more useful function like an XOR or equivalence checker.

The diagram is clear and follows standard conventions, making the signal flow and gate functions unambiguous for technical analysis.