## Diagram: Compilation Flow for Fortran Code

### Overview

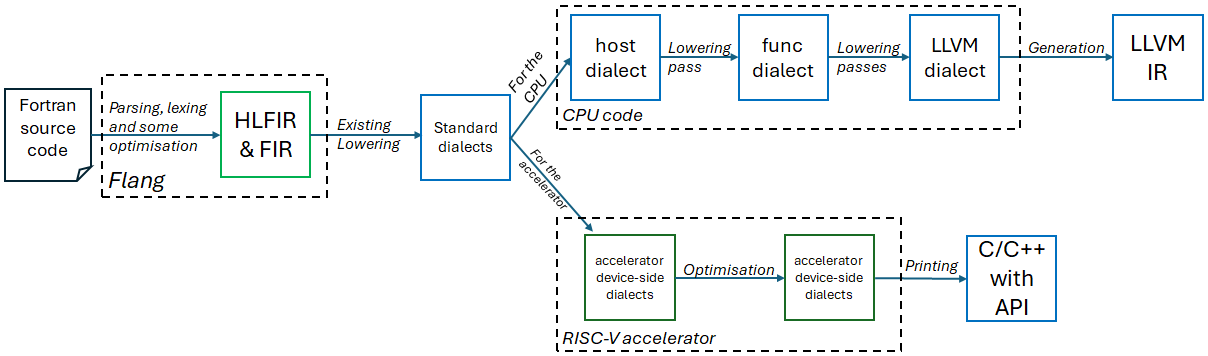

The image is a diagram illustrating the compilation flow of Fortran source code, targeting both CPU and RISC-V accelerator architectures. It shows the stages of compilation, including parsing, lowering, optimization, and code generation.

### Components/Axes

* **Input:** Fortran source code

* **Intermediate Representations:** HLFIR & FIR, Standard dialects, host dialect, func dialect, LLVM dialect, accelerator device-side dialects

* **Output:** LLVM IR, C/C++ with API

* **Tools/Processes:** Flang, Parsing, lexing and some optimisation, Existing Lowering, Lowering pass, Lowering passes, Generation, Optimisation, Printing

* **Target Architectures:** CPU code, RISC-V accelerator

### Detailed Analysis or ### Content Details

1. **Fortran Source Code Input:**

* A box labeled "Fortran source code" in the top-left corner represents the initial input.

* An arrow points from this box to a dashed-line box labeled "Flang".

* Inside the dashed box is the text "Parsing, lexing and some optimisation".

2. **HLFIR & FIR:**

* The output of "Flang" is a green box labeled "HLFIR & FIR".

3. **Standard Dialects:**

* An arrow labeled "Existing Lowering" points from "HLFIR & FIR" to a blue box labeled "Standard dialects".

4. **CPU Code Path:**

* An arrow labeled "For the CPU" points from "Standard dialects" to a dashed-line box labeled "CPU code".

* Inside the dashed box are three blue boxes: "host dialect", "func dialect", and "LLVM dialect".

* Arrows connect these boxes, labeled "Lowering pass" and "Lowering passes" respectively.

* An arrow labeled "Generation" points from "LLVM dialect" to a blue box labeled "LLVM IR".

5. **RISC-V Accelerator Path:**

* An arrow labeled "For the accelerator" points from "Standard dialects" to a dashed-line box labeled "RISC-V accelerator".

* Inside the dashed box are two green boxes: "accelerator device-side dialects" (appears twice).

* An arrow labeled "Optimisation" connects the first "accelerator device-side dialects" box to the second.

* An arrow labeled "Printing" points from the second "accelerator device-side dialects" box to a blue box labeled "C/C++ with API".

### Key Observations

* The diagram shows two distinct compilation paths: one for CPU and one for a RISC-V accelerator.

* The initial stages (Fortran source code to Standard dialects) are common to both paths.

* The CPU path involves lowering to host, func, and LLVM dialects before generating LLVM IR.

* The accelerator path involves optimization of accelerator device-side dialects before generating C/C++ code with an API.

### Interpretation

The diagram illustrates a compilation process that leverages Flang to parse Fortran code and generate intermediate representations suitable for different target architectures. The use of dialects allows for target-specific optimizations and code generation. The CPU path targets LLVM IR, a common intermediate representation for many architectures, while the RISC-V accelerator path generates C/C++ code with an API, suggesting a different approach to code execution on the accelerator. The diagram highlights the flexibility of the compilation process in supporting diverse hardware platforms.