## Table: Formalization of Logic Gates

### Overview

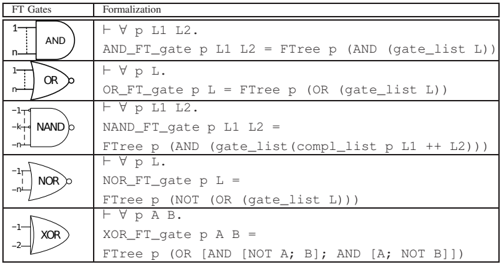

The image presents a table mapping five fundamental logic gates (AND, OR, NAND, NOR, XOR) to their formalized representations using logical operators and a function called `FTTree`. Each gate is depicted with its standard symbol and annotated with variables (e.g., `n`, `-1`, `-k`), while the corresponding formalization uses logical expressions and nested function calls.

---

### Components/Axes

- **Columns**:

1. **FT Gates**: Contains symbols for logic gates with annotations.

2. **Formalization**: Contains logical expressions using `FTTree`, `AND`, `OR`, `NOT`, and `gate_list`.

- **Annotations**:

- **AND Gate**: Labeled with `n` (input count).

- **NAND Gate**: Annotated with `-1` (inversion) and `-k` (complement).

- **NOR Gate**: Annotated with `-1` (inversion) and `-n` (negated input count).

- **XOR Gate**: Annotated with `-2` (two inputs).

---

### Detailed Analysis

#### Row 1: AND Gate

- **Symbol**: Standard AND gate with `n` inputs.

- **Formalization**:

`AND_FT_gate p L1 L2 = FTree p (AND (gate_list L))`

*Interpretation*: Represents an AND gate with inputs `L1` and `L2`, formalized using `FTTree` and `gate_list`.

#### Row 2: OR Gate

- **Symbol**: Standard OR gate with `n` inputs.

- **Formalization**:

`OR_FT_gate p L = FTree p (OR (gate_list L))`

*Interpretation*: Represents an OR gate with inputs `L`, formalized using `FTTree` and `gate_list`.

#### Row 3: NAND Gate

- **Symbol**: NAND gate with `-1` (inversion) and `-k` (complement) annotations.

- **Formalization**:

`NAND_FT_gate p L1 L2 = FTree p (AND (gate_list(compl_list p L1 ++ L2)))`

*Interpretation*: Combines `L1` (complemented) and `L2` via `compl_list`, then applies `AND` and `FTTree`.

#### Row 4: NOR Gate

- **Symbol**: NOR gate with `-1` (inversion) and `-n` (negated input count) annotations.

- **Formalization**:

`NOR_FT_gate p L = FTree p (NOT (OR (gate_list L)))`

*Interpretation*: Applies `NOT` to the result of `OR` over `gate_list L`, then uses `FTTree`.

#### Row 5: XOR Gate

- **Symbol**: XOR gate with `-2` (two inputs) annotation.

- **Formalization**:

`XOR_FT_gate p A B = FTree p (OR [AND [NOT A; B]; AND [A; NOT B]])`

*Interpretation*: Implements XOR as `(A AND NOT B) OR (NOT A AND B)` using nested `AND`/`NOT` operations.

---

### Key Observations

1. **Consistency**: All formalizations use `FTTree` as a wrapper function, suggesting a unified framework for gate representation.

2. **Complement Handling**: NAND and NOR gates explicitly use `compl_list` and `NOT` to handle inverted inputs.

3. **XOR Complexity**: XOR is decomposed into a combination of `AND`, `NOT`, and `OR`, reflecting its non-linear nature.

---

### Interpretation

This table formalizes logic gates into a structured format likely for use in formal verification, hardware description languages (HDLs), or symbolic computation. The `FTTree` function appears central, possibly representing a tree-based abstraction for gate operations. The annotations (`n`, `-1`, `-k`) indicate input counts and inversion rules, critical for defining gate behavior in formal systems. The decomposition of XOR into basic operations highlights the table’s focus on breaking down complex logic into foundational components.