## Diagram: SIMD Extension Comparison

### Overview

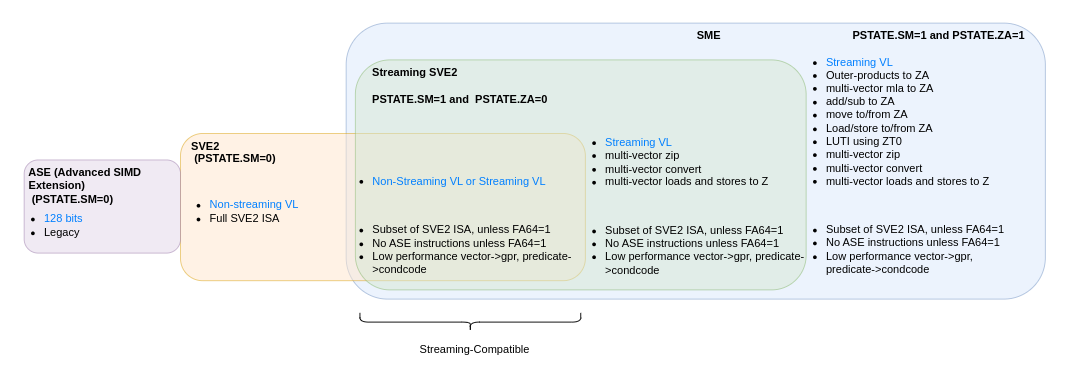

The image is a Venn diagram illustrating the relationship between different SIMD (Single Instruction, Multiple Data) extensions: ASE (Advanced SIMD Extension), SVE2, and SME. The diagram highlights the features and compatibility of these extensions based on the PSTATE.SM and PSTATE.ZA flags.

### Components/Axes

* **Shapes:** The diagram uses rounded rectangles to represent different SIMD extensions and their features.

* **Labels:**

* ASE (Advanced SIMD Extension) (PSTATE.SM=0) - Located on the left, in a light purple rounded rectangle.

* SVE2 (PSTATE.SM=0) - Located in the center-left, in a light orange rounded rectangle.

* Streaming SVE2 (PSTATE.SM=1 and PSTATE.ZA=0) - Located in the center, in a light green rounded rectangle.

* SME - Located in the center-right, implied by the overlap of the green and blue rounded rectangles.

* PSTATE.SM=1 and PSTATE.ZA=1 - Located on the right, in a light blue rounded rectangle.

* Streaming-Compatible - Located at the bottom, indicating the compatibility between Streaming SVE2 and SME.

* **Features:** Each section lists specific features or characteristics of the corresponding SIMD extension.

### Detailed Analysis or Content Details

* **ASE (Advanced SIMD Extension) (PSTATE.SM=0):**

* 128 bits

* Legacy

* **SVE2 (PSTATE.SM=0):**

* Non-streaming VL

* Full SVE2 ISA

* **Streaming SVE2 (PSTATE.SM=1 and PSTATE.ZA=0):**

* Non-Streaming VL or Streaming VL

* Subset of SVE2 ISA, unless FA64=1

* No ASE instructions unless FA64=1

* Low performance vector->gpr, predicate->condcode

* **SME (Implied by overlap):**

* Streaming VL

* multi-vector zip

* multi-vector convert

* multi-vector loads and stores to Z

* Subset of SVE2 ISA, unless FA64=1

* No ASE instructions unless FA64=1

* Low performance vector->gpr, predicate->condcode

* **PSTATE.SM=1 and PSTATE.ZA=1:**

* Streaming VL

* Outer-products to ZA

* multi-vector mla to ZA

* add/sub to ZA

* move to/from ZA

* Load/store to/from ZA

* LUTI using ZTO

* multi-vector zip

* multi-vector convert

* multi-vector loads and stores to Z

* Subset of SVE2 ISA, unless FA64=1

* No ASE instructions unless FA64=1

* Low performance vector->gpr, predicate->condcode

### Key Observations

* ASE is the most basic extension, with 128-bit support and legacy status.

* SVE2 builds upon ASE, providing non-streaming VL and a full ISA.

* Streaming SVE2 and SME share some features and are considered "Streaming-Compatible."

* The PSTATE.SM and PSTATE.ZA flags determine the specific features available in each extension.

* All extensions except ASE are subsets of SVE2 ISA unless FA64=1, and lack ASE instructions unless FA64=1. They also have low performance vector->gpr, predicate->condcode.

### Interpretation

The diagram illustrates the evolution and relationships between different SIMD extensions. It shows how SVE2 builds upon ASE and how Streaming SVE2 and SME offer advanced features for streaming workloads. The PSTATE flags play a crucial role in enabling or disabling specific features within these extensions. The diagram highlights the trade-offs between compatibility, performance, and feature set in the context of SIMD programming.