\n

## Diagram: Arm SVE2 and SME Feature Overview

### Overview

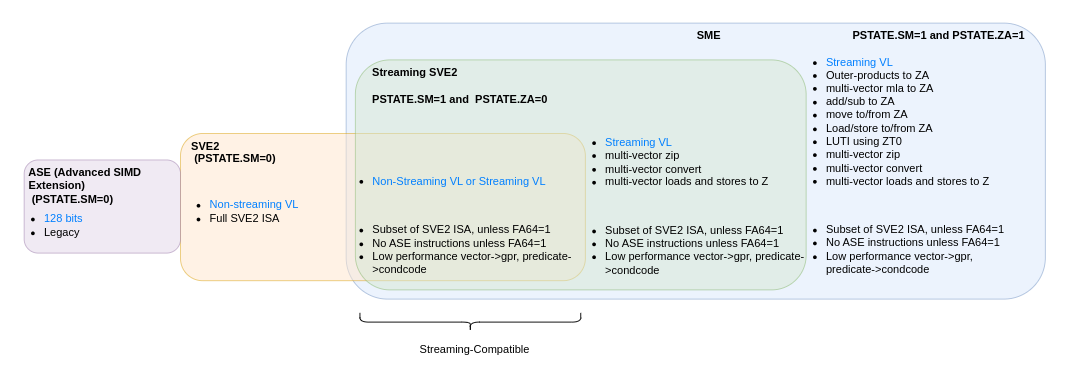

This diagram illustrates the relationship between SVE2 (Scalable Vector Extension 2), ASE (Advanced SIMD Extension), and SME (Scalable Matrix Extension) features in Arm processors. It visually represents the compatibility and capabilities of each feature set, particularly concerning streaming and non-streaming vector lengths (VL). The diagram uses colored boxes and text to delineate feature sets and their associated characteristics.

### Components/Axes

The diagram consists of three main rectangular blocks representing SVE2, Streaming SVE2, and SME. These blocks are interconnected to show compatibility. Text within each block details the features and conditions associated with each extension. A label at the bottom reads "Streaming-Compatible". The diagram also includes the PSTATE values associated with each feature.

### Detailed Analysis or Content Details

**SVE2 (PSTATE.SM=0)** (Leftmost Block - Orange)

* PSTATE.SM=0

* Non-streaming VL

* Full SVE2 ISA

**Streaming SVE2** (Center Block - Light Blue)

* PSTATE.SM=1 and PSTATE.ZA=0

* Streaming VL

* Non-Streaming VL or Streaming VL

* Subset of SVE2 ISA, unless FA64=1

* No ASE instructions unless FA64=1

* Low performance vector ->xpr, predicate->condcode

* Subset of SVE2 ISA, unless FA64=1

* No ASE instructions unless FA64=1

* Low performance vector ->xpr, predicate->condcode

**SME** (Rightmost Block - Green)

* PSTATE.SM=1 and PSTATE.ZA=1

* Streaming VL

* Outer-products to ZA

* multi-vector mla to ZA

* add/sub to ZA

* move to/from ZA

* Load/store to/from ZA

* LUTI using ZT0

* multi-vector zip

* multi-vector convert

* multi-vector loads and stores to Z

* Subset of SVE2 ISA, unless FA64=1

* No ASE instructions unless FA64=1

* Low performance vector ->xpr, predicate->condcode

**ASE (Advanced SIMD Extension)** (Small text within SVE2 block)

* 128 bits

* Legacy

### Key Observations

* SVE2 forms the base, with Streaming SVE2 and SME building upon it.

* Streaming SVE2 and SME both require PSTATE.SM=1, but differ in the value of PSTATE.ZA (0 vs. 1).

* All three feature sets can utilize a subset of the SVE2 ISA, contingent on the FA64 flag.

* The diagram highlights the importance of PSTATE values in determining the active feature set.

* ASE is presented as a legacy component within the SVE2 context.

* The "Low performance vector ->xpr, predicate->condcode" is repeated across Streaming SVE2 and SME.

### Interpretation

The diagram demonstrates the evolution of vector processing capabilities in Arm architectures. SVE2 provides the foundational scalable vector processing, while Streaming SVE2 extends this to support streaming data. SME further enhances this with specialized matrix processing capabilities, leveraging the ZA registers. The PSTATE flags act as configuration switches, enabling or disabling specific features. The inclusion of ASE as a legacy component suggests a transition towards the more modern SVE and SVE2 architectures. The repeated note about low performance vectors and predicate conditions suggests a potential performance trade-off when using certain configurations. The diagram is a high-level overview, focusing on compatibility and feature sets rather than detailed technical specifications. It's a useful tool for understanding the relationships between these different extensions and how they can be utilized in Arm processors.