## Diagram: SIMD Instruction Set Comparison

### Overview

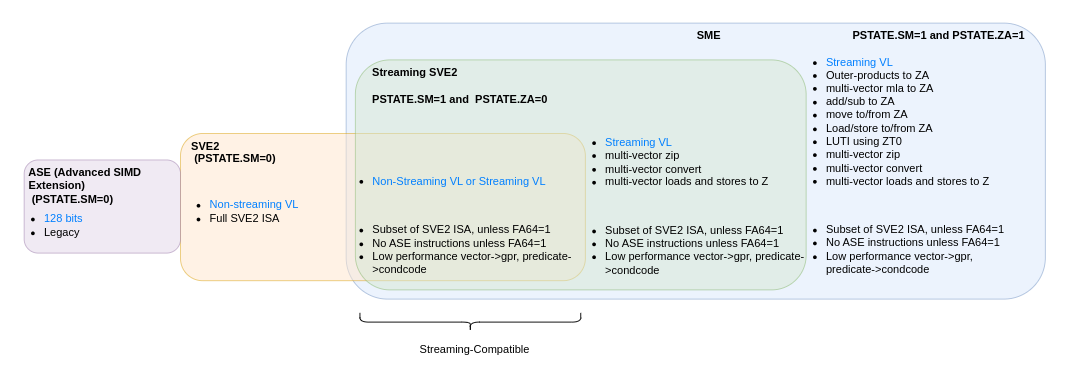

The diagram compares three SIMD (Single Instruction, Multiple Data) instruction sets: ASE (Advanced SIMD Extension), SVE2 (Scalable Vector Extension 2), and Streaming SVE2. It highlights their features, dependencies, and compatibility with streaming operations. The diagram uses color-coded boxes to represent each instruction set and includes a legend for spatial grounding.

### Components/Axes

- **Legend**: Located at the bottom center, labeled "Streaming-Compatible" with a green color.

- **Boxes**:

1. **Purple Box (ASE)**:

- Label: "ASE (Advanced SIMD Extension) (PSTATE.SM=0)"

- Features: "128 bits", "Legacy"

2. **Orange Box (SVE2)**:

- Label: "SVE2 (PSTATE.SM=0)"

- Features: "Non-streaming VL", "Full SVE2 ISA"

3. **Green Box (Streaming SVE2)**:

- Label: "Streaming SVE2 (PSTATE.SM=1 and PSTATE.ZA=0)"

- Sub-boxes:

- **Light Green**: "Non-Streaming VL or Streaming VL"

- **Darker Green**: "Streaming VL"

- **Text Elements**:

- Labels for PSTATE.SM and PSTATE.ZA flags.

- Feature lists for each instruction set (e.g., "multi-vector zip," "outer-products to ZA").

### Detailed Analysis

1. **ASE (Purple Box)**:

- 128-bit support.

- Legacy instructions (backward compatibility).

- No streaming capabilities (PSTATE.SM=0).

2. **SVE2 (Orange Box)**:

- Non-streaming vector load/store (VL).

- Full SVE2 ISA unless FA64=1 (a condition for subsetting instructions).

- Low-performance vector operations (e.g., `>gpr`, `predicate->condcode`).

- No ASE instructions unless FA64=1.

3. **Streaming SVE2 (Green Box)**:

- **Light Green Sub-box**:

- Combines non-streaming and streaming VL.

- Subset of SVE2 ISA unless FA64=1.

- No ASE instructions unless FA64=1.

- Low-performance vector operations.

- **Darker Green Sub-box (Streaming VL)**:

- Advanced features: multi-vector zip, convert, loads/stores to ZA.

- Requires PSTATE.SM=1 and PSTATE.ZA=0.

- Includes outer-products to ZA, add/sub to ZA, and LUTI using ZST0.

### Key Observations

- **Streaming Compatibility**: The green box (Streaming SVE2) is explicitly marked as "Streaming-Compatible" in the legend, indicating it supports advanced streaming operations.

- **Conditional Features**: Many features depend on PSTATE flags (e.g., PSTATE.SM=1 enables streaming, PSTATE.ZA=1 enables outer-products).

- **Legacy vs. Modern**: ASE (purple) is the oldest, while Streaming SVE2 (green) represents the most advanced, feature-rich set.

- **Performance Trade-offs**: Non-streaming SVE2 (orange) and Streaming SVE2 (green) include low-performance vector operations unless FA64=1.

### Interpretation

The diagram illustrates the evolution of SIMD instruction sets in a processor architecture:

1. **ASE** serves as the foundational, legacy-compatible set with basic 128-bit support.

2. **SVE2** introduces scalability but lacks streaming capabilities unless combined with Streaming SVE2.

3. **Streaming SVE2** enables advanced vector operations (e.g., multi-vector loads/stores, outer-products) but requires specific hardware states (PSTATE.SM=1 and PSTATE.ZA=1). The dependency on FA64=1 suggests compiler/runtime control over instruction subsets, balancing performance and compatibility.

Notable trends:

- **Increasing Complexity**: Features progress from basic (ASE) to advanced (Streaming SVE2).

- **Conditional Enablement**: Many features are gated by PSTATE flags or FA64=1, indicating runtime or compiler-driven optimization.

- **Legacy Support**: ASE retains legacy instructions, while newer sets phase them out unless explicitly enabled.

This diagram likely reflects a processor architecture's SIMD evolution, emphasizing trade-offs between performance, compatibility, and feature richness.