\n

## Diagram: Synapse Model

### Overview

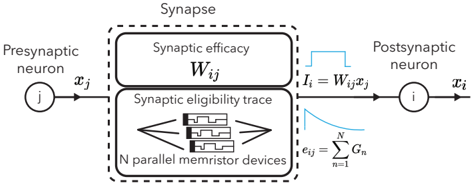

The image depicts a diagram of a synapse, illustrating the flow of information from a presynaptic neuron to a postsynaptic neuron. The synapse is represented as a processing unit containing synaptic efficacy and synaptic eligibility trace components, with the latter implemented using N parallel memristor devices. The diagram also includes equations representing the signal transmission and eligibility trace calculation.

### Components/Axes

The diagram consists of the following components:

* **Presynaptic Neuron:** Labeled "Presynaptic neuron" and represented by a circle with the input signal "x<sub>j</sub>".

* **Synapse:** Enclosed in a dashed box, labeled "Synapse".

* **Synaptic Efficacy:** A rectangular box within the synapse, labeled "Synaptic efficacy" and containing the variable "W<sub>ij</sub>".

* **Synaptic Eligibility Trace:** A rectangular box within the synapse, labeled "Synaptic eligibility trace" and containing a representation of N parallel memristor devices.

* **N parallel memristor devices:** Represented as a series of four rectangular blocks with pulse-like waveforms within them, labeled "N parallel memristor devices".

* **Postsynaptic Neuron:** Labeled "Postsynaptic neuron" and represented by a circle with the output signal "x<sub>i</sub>".

* **Signal Transmission Equation:** "I<sub>i</sub> = W<sub>ij</sub>x<sub>j</sub>" representing the signal transmission from the presynaptic to the postsynaptic neuron.

* **Eligibility Trace Equation:** "ε<sub>ij</sub> = ∑<sub>n=1</sub><sup>N</sup> G<sub>n</sub>" representing the calculation of the synaptic eligibility trace based on the memristor devices.

### Detailed Analysis or Content Details

The diagram illustrates the following flow:

1. A signal "x<sub>j</sub>" is transmitted from the presynaptic neuron (j) to the synapse.

2. Within the synapse, the signal is multiplied by the synaptic efficacy "W<sub>ij</sub>", resulting in the signal "I<sub>i</sub>" which is transmitted to the postsynaptic neuron (i).

3. The synaptic eligibility trace is calculated based on the output of N parallel memristor devices, represented by the summation equation "ε<sub>ij</sub> = ∑<sub>n=1</sub><sup>N</sup> G<sub>n</sub>".

4. The output of the synaptic eligibility trace influences the synaptic efficacy "W<sub>ij</sub>" (although the feedback loop is not explicitly shown).

The waveforms within the "N parallel memristor devices" block suggest a pulsed or time-varying signal. The equation for the synaptic eligibility trace indicates that the trace is a sum of contributions from each of the N memristor devices (G<sub>n</sub>).

### Key Observations

The diagram highlights the role of memristor devices in implementing the synaptic eligibility trace, which is a crucial component in synaptic plasticity models. The use of N parallel devices suggests a potential for increased computational capacity or robustness. The diagram focuses on the signal flow and mathematical representation of the synapse, rather than the physical structure of the synapse.

### Interpretation

This diagram represents a computational model of a synapse, likely used in the context of artificial neural networks or neuromorphic computing. The use of memristors as the core element of the synaptic eligibility trace suggests an attempt to mimic the biological mechanisms of synaptic plasticity. The equations provided formalize the relationship between the input signal, synaptic efficacy, and eligibility trace. The diagram suggests that the synaptic strength (W<sub>ij</sub>) is modulated by the activity of the presynaptic neuron (x<sub>j</sub>) and the state of the memristor devices (G<sub>n</sub>). The parallel architecture of the memristor devices could enable efficient and scalable implementation of synaptic plasticity. The diagram is a simplified representation of a complex biological system, focusing on the key computational elements and their interactions.