## Diagram: Mintaur Core Architecture

### Overview

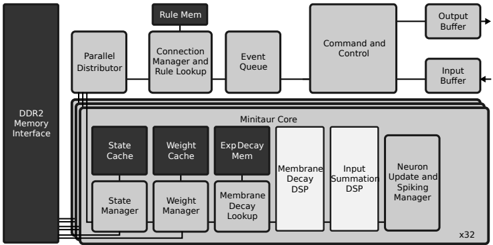

The diagram illustrates the architecture of the "Mintaur Core," a system designed for parallel processing and neural computation. It includes memory interfaces, data flow components, and specialized processing units. The system emphasizes modularity, with distinct blocks for memory management, event handling, and neural operations.

### Components/Axes

- **Left Side**:

- **DDR2 Memory Interface**: Connects to the system via multiple parallel channels.

- **Parallel Distributor**: Distributes data across the system.

- **Connection Manager and Rule Lookup**: Manages connections and rule-based logic.

- **Event Queue**: Buffers events for processing.

- **Central Block (Mintaur Core)**:

- **State Cache**: Managed by a **State Manager**.

- **Weight Cache**: Managed by a **Weight Manager**.

- **ExpDecay Mem**: Managed by an **ExpDecay Mem Manager**.

- **Membrane Decay Lookup**: Processes membrane decay operations.

- **Membrane Decay DSP**: Dedicated digital signal processor for membrane decay.

- **Input Summation DSP**: Handles input summation tasks.

- **Neuron Update and Spiking Manager**: Manages neuron activity updates and spiking events.

- **Right Side**:

- **Command and Control**: Central processing unit for system-wide coordination.

- **Output Buffer**: Temporarily stores output data.

- **Input Buffer**: Temporarily stores input data.

### Detailed Analysis

- **Data Flow**:

Data enters via the **DDR2 Memory Interface**, is distributed by the **Parallel Distributor**, and processed through the **Connection Manager** and **Rule Lookup**. Events are queued before entering the **Mintaur Core**.

- The **State Cache** and **Weight Cache** store transient and learned data, respectively.

- **ExpDecay Mem** likely implements exponential decay for memory retention or forgetting mechanisms.

- **Membrane Decay DSP** and **Input Summation DSP** handle specialized signal processing tasks.

- The **Neuron Update and Spiking Manager** orchestrates real-time neuron activity.

- Final outputs are routed through the **Command and Control** to the **Output Buffer**.

- **Key Labels**:

- All blocks are labeled with their functional roles (e.g., "State Manager," "Membrane Decay DSP").

- The **Mintaur Core** is the central processing unit, surrounded by memory and I/O components.

- The **x32** notation suggests a 32-wide data path or parallelism factor.

### Key Observations

1. **Modular Design**: The system separates memory, processing, and control units for scalability.

2. **Parallelism**: The **Parallel Distributor** and **x32** notation indicate high-throughput capabilities.

3. **Neural Focus**: Components like **Neuron Update and Spiking Manager** and **Membrane Decay DSP** suggest applications in neuromorphic computing or artificial neural networks.

4. **Efficiency**: Dedicated DSPs for membrane decay and input summation optimize performance for specific tasks.

### Interpretation

The architecture is tailored for systems requiring real-time neural computation, such as AI accelerators or brain-inspired processors. The **ExpDecay Mem** and **Membrane Decay DSP** imply mechanisms for dynamic memory management, critical for adaptive learning. The **Command and Control** acts as a central hub, ensuring synchronization between parallel processes. The **x32** parallelism factor highlights the system’s ability to handle large data volumes simultaneously, making it suitable for high-performance computing tasks.

No numerical data or trends are present in the diagram. The focus is on structural and functional relationships between components.