## System Diagram: Neuromorphic Computing Workflow

### Overview

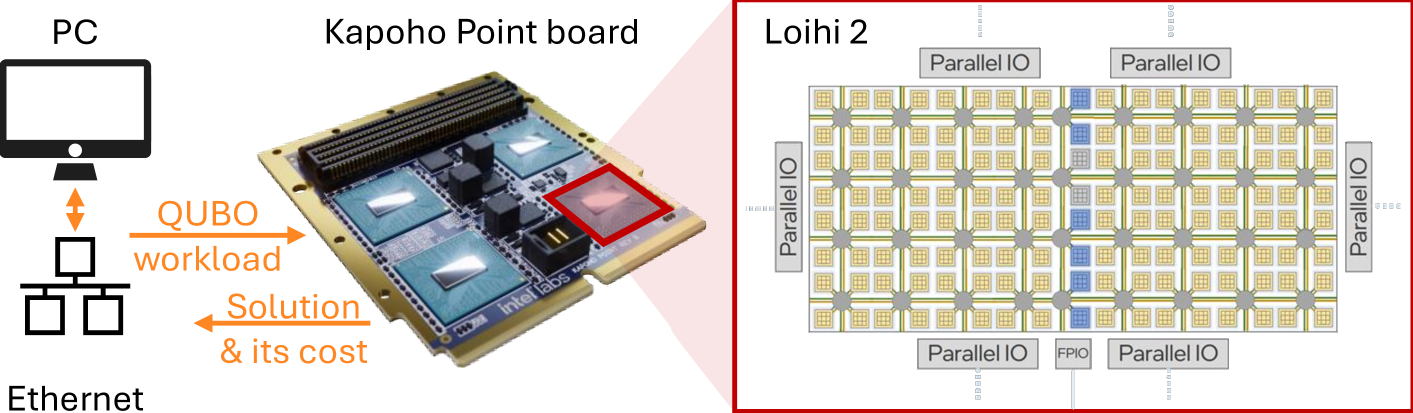

The image is a technical diagram illustrating the workflow and hardware architecture of a neuromorphic computing system. It shows the data flow from a host PC to a specialized hardware board (Kapoho Point) containing Intel's Loihi 2 neuromorphic chips, and the return of results. The diagram is split into two primary sections: a high-level system view on the left and a detailed chip architecture view on the right.

### Components/Axes

The diagram contains no traditional chart axes. Its components are labeled as follows:

**Left Section (System View):**

* **PC:** Represented by a desktop computer icon.

* **Ethernet:** Represented by a network switch icon connected to the PC.

* **Kapoho Point board:** A photograph of a physical circuit board. Text printed on the board reads "Intel Labs" and "Kapoho Point".

* **Data Flow Arrows:**

* An orange arrow points from the PC/Ethernet to the Kapoho Point board, labeled **"QUBO workload"**.

* An orange arrow points from the Kapoho Point board back to the PC/Ethernet, labeled **"Solution & its cost"**.

**Right Section (Chip Architecture View):**

* **Loihi 2:** The title for this section, indicating the chip architecture being detailed.

* **Parallel IO:** This label appears six times, positioned around the perimeter of the central grid (top-left, top-center, top-right, bottom-left, bottom-right, and left-center).

* **FPIO:** This label appears once at the bottom-center of the grid.

* **Central Grid:** A large grid composed of many small squares. The grid is organized into a matrix of larger tiles (approximately 12 columns by 8 rows). Within this grid:

* Most squares are a light yellow/beige color.

* A vertical column of squares, located roughly in the center (column 7 from the left), is colored blue.

* A few scattered squares are colored gray. Their positions are not perfectly regular but appear in the upper-left quadrant and near the center.

### Detailed Analysis

The diagram describes a computational pipeline:

1. **Input:** A **"QUBO workload"** (Quadratic Unconstrained Binary Optimization problem) is sent from a host system (PC via Ethernet) to the Kapoho Point board.

2. **Processing:** The workload is processed by the neuromorphic hardware on the Kapoho Point board, which is highlighted by a red box around one of the chips. The right side of the diagram zooms in on the architecture of one such chip, the **Loihi 2**.

3. **Chip Architecture:** The Loihi 2 chip is depicted as a grid-based architecture. The grid is surrounded by **Parallel IO** interfaces on multiple sides, suggesting high-bandwidth communication pathways. The **FPIO** (likely Fabric or Fast Programmable IO) is a distinct interface at the bottom. The colored squares within the grid (blue, gray, yellow) likely represent different types of cores, memory blocks, or functional units, though a specific legend is not provided in the image.

4. **Output:** The result of the computation, the **"Solution & its cost"**, is sent back from the board to the host system.

### Key Observations

* **Asymmetric Data Flow:** The input is a specific problem type (QUBO), while the output is a solution paired with its associated cost metric.

* **Hardware Emphasis:** The diagram focuses on the physical hardware (Kapoho Point board) and the internal architecture of the Loihi 2 chip, rather than software or algorithms.

* **Spatial Grounding of Labels:** The "Parallel IO" labels are strategically placed around the chip's perimeter, indicating distributed I/O resources. The "FPIO" is singular and centrally located at the bottom.

* **Color-Coded Grid Elements:** The blue column and scattered gray squares within the predominantly yellow grid suggest a non-uniform, potentially specialized or configured, internal chip layout. The blue column is a prominent vertical feature.

### Interpretation

This diagram illustrates the end-to-end process for solving optimization problems using Intel's neuromorphic hardware. The **QUBO workload** is a common formulation for complex optimization problems (like logistics, scheduling, or machine learning). The system offloads this computationally intensive task from a conventional PC to the specialized, energy-efficient **Loihi 2 neuromorphic chips** on the Kapoho Point board.

The **Loihi 2 architecture diagram** reveals a design optimized for parallel, distributed processing. The extensive **Parallel IO** suggests the chip is built to communicate efficiently with many neighbors or external components, which is critical for large-scale neural network simulations. The colored grid implies a heterogeneous architecture where different regions (blue, gray, yellow) may be dedicated to different functions—such as neural cores, memory, or routing fabric—allowing for efficient mapping of the QUBO problem onto the hardware.

The return of the **"Solution & its cost"** is crucial, as optimization algorithms often need to evaluate the quality (cost) of a proposed solution. This closed-loop system allows the host to receive not just an answer, but a measure of its optimality, enabling further decision-making. The overall message is one of specialized acceleration: using a unique neuromorphic architecture to solve a specific, hard class of problems more efficiently than a general-purpose computer.