# Technical Document Extraction: Kapoho Point Board and Loihi 2 Architecture

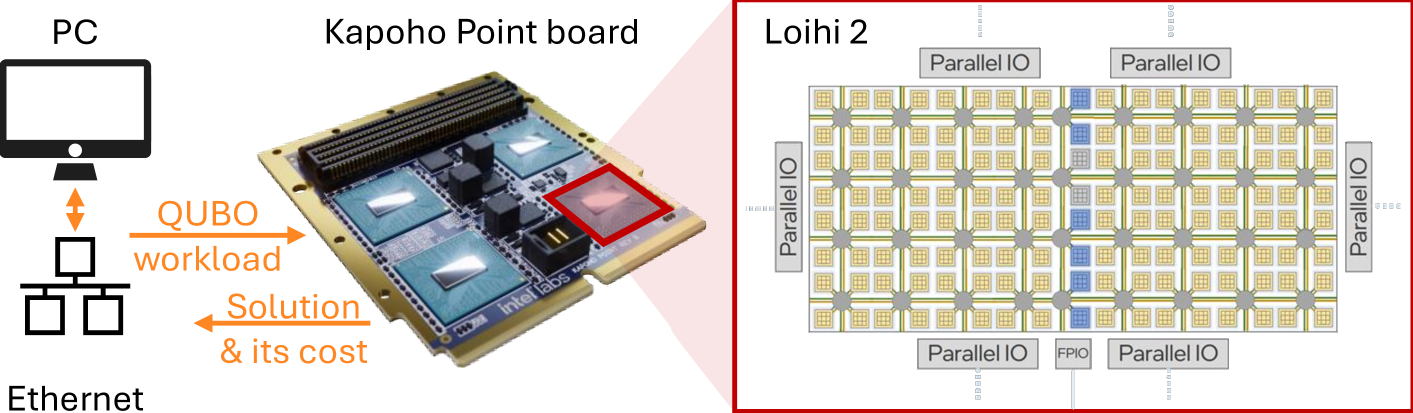

## 1. Kapoho Point Board Overview

*Diagram showing hardware architecture and workflow*

### Key Components:

- **PC**: Connected via Ethernet to the Kapoho Point board

- **Ethernet**: Communication link between PC and board

- **QUBO Workload**: Input/output flow indicated by orange bidirectional arrow

- **Solution & Cost**: Output flow from board to PC

- **Intel Loihi 2 Chips**: Four visible on the board (highlighted by red box)

## 2. Loihi 2 Core Architecture

*Detailed chip architecture visualization*

### Core Layout:

- **Grid Structure**: 8x8 array of cores (64 total)

- **Parallel IO**: Label on all four sides of the chip

- **FPGA**: Central processing unit (labeled "FPGA" in diagram)

- **Core States**:

- **Active Cores**: Blue squares (exact count unspecified)

- **Inactive Cores**: Gray squares (exact count unspecified)

### Spatial Relationships:

- **Core Coordinates**:

- X-axis: Left to Right (8 columns)

- Y-axis: Top to Bottom (8 rows)

- **FPGA Position**: Center of the 8x8 grid

## 3. Workflow Diagram Analysis

### Data Flow:

1. **Input**: QUBO workload from PC → Ethernet → Kapoho Point board

2. **Processing**:

- Distributed across Intel Loihi 2 chips

- FPGA coordinates core operations

3. **Output**: Solution and cost metrics returned to PC

## 4. Color Coding Legend

*Note: Legend colors not visually distinguishable in provided image. Labels used for identification:*

- **Blue**: Active cores (Parallel IO)

- **Gray**: Inactive cores (Parallel IO)

- **Red Box**: Highlighted Loihi 2 chip in Kapoho Point board

## 5. Technical Specifications

| Component | Description |

|--------------------|--------------------------------------|

| Kapoho Point Board | Hardware interface for Loihi 2 chips |

| Loihi 2 Chip | 64-core neuromorphic processor |

| Ethernet | Communication protocol |

| QUBO | Quadratic Unconstrained Binary Optimization problem type |

## 6. Architectural Notes

- **Modular Design**: Four Loihi 2 chips enable distributed computing

- **IO Optimization**: Parallel IO on all four sides suggests multi-directional data flow

- **FPGA Integration**: Centralized control for core coordination

*Note: No numerical data or quantitative metrics present in the diagrams. All information extracted from visual labels and spatial relationships.*