## Diagram: Out-of-Order Processor Pipeline with In-Order Retirement

### Overview

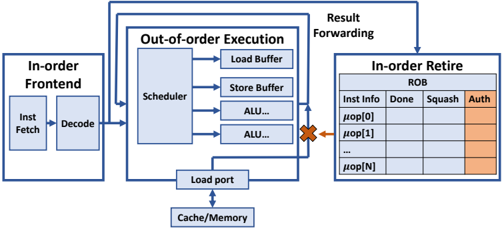

The image is a technical block diagram illustrating the microarchitecture of a modern processor core. It depicts the flow of instructions through three primary stages: an in-order frontend, an out-of-order execution engine, and an in-order retirement unit. A key feature highlighted is a blockage (marked with an orange "X") in the path from the execution engine to the retirement unit, indicating a pipeline stall or exception scenario.

### Components/Axes

The diagram is organized into three main rectangular blocks, connected by directional arrows indicating data and instruction flow.

1. **In-order Frontend (Left Block):**

* Contains two sub-blocks: `Inst Fetch` and `Decode`.

* An arrow flows from `Inst Fetch` to `Decode`.

* An arrow exits the `Decode` block and points to the central `Out-of-order Execution` block.

2. **Out-of-order Execution (Central Block):**

* This is the largest block, containing several key components:

* `Scheduler`: A central control unit.

* `Load Buffer`: Positioned to the right of the Scheduler.

* `Store Buffer`: Positioned below the Load Buffer.

* `ALU...`: Two blocks labeled `ALU...` are shown below the Store Buffer, indicating multiple Arithmetic Logic Units.

* **Internal Flow:** Arrows point from the `Scheduler` to the `Load Buffer`, `Store Buffer`, and both `ALU...` blocks.

* **External Connections:**

* A `Load port` block is connected below the main execution block.

* The `Load port` connects to a `Cache/Memory` block at the bottom of the diagram.

* A line labeled `Result Forwarding` originates from the execution block (likely from the ALUs/buffers) and loops back to the input of the `Scheduler`, representing data forwarding for dependency resolution.

3. **In-order Retire (Right Block):**

* Contains a table labeled `ROB` (Reorder Buffer).

* The ROB table has the following columns (from left to right):

* `Inst Info`

* `Done`

* `Squash`

* `Auth` (This column is highlighted with an orange background).

* The table rows are labeled:

* `jop[0]`

* `jop[1]`

* `...`

* `jop[N]`

* **Critical Blockage:** An orange "X" symbol is placed on the arrow connecting the `Out-of-order Execution` block to the `In-order Retire` block. This visually indicates that the flow of completed instructions from the execution engine to the reorder buffer for retirement is currently blocked.

### Detailed Analysis

* **Instruction Flow:** Instructions are fetched and decoded in-order in the frontend. They are then dispatched to the out-of-order execution engine, where the `Scheduler` issues them to available functional units (`ALU`, `Load/Store Buffers`). Results can be forwarded internally to resolve data dependencies. Completed instructions wait in the `ROB` to be retired in their original program order.

* **ROB Structure:** The Reorder Buffer (`ROB`) is a circular buffer holding instruction metadata. The columns suggest tracking instruction completion (`Done`), the ability to squash/rollback the instruction (`Squash`), and an `Auth` (Authentication/Authorization) status, which is a non-standard field potentially indicating a security or validation feature.

* **Blockage Point:** The orange "X" is spatially located on the data path between the execution units and the ROB. This is the precise point where the pipeline is stalled. Instructions have been executed but cannot be written back to the ROB for retirement.

### Key Observations

1. **Non-Standard `Auth` Column:** The presence of an `Auth` column in the ROB is a distinctive feature not found in classic academic CPU models. It implies the architecture has hardware support for tracking the authentication or authorization state of each instruction or its data, possibly for security domains or trusted execution.

2. **Explicit Blockage Visualization:** The diagram explicitly models a failure or stall condition (the orange "X"), which is unusual for a generic pipeline diagram. This suggests the diagram's purpose is to illustrate a specific exception handling, security violation, or resource conflict scenario.

3. **Result Forwarding Loop:** The dedicated `Result Forwarding` path is clearly shown, emphasizing the importance of this optimization in out-of-order engines to reduce stalls from data hazards.

4. **Scalable ROB:** The `jop[0]` to `jop[N]` notation indicates a Reorder Buffer of configurable or scalable depth (`N` entries).

### Interpretation

This diagram represents a **secure or authenticated out-of-order processor pipeline**. The core narrative is not just the normal operation, but a specific **blocked state**.

* **What the Blockage Suggests:** The orange "X" indicates that while instructions have been processed out-of-order, they are prevented from retiring. This is a critical pipeline stall. Given the presence of the `Auth` column, the most plausible interpretation is that an **authentication or authorization check has failed** for one or more instructions in the ROB. The pipeline is frozen until this security violation is resolved (e.g., by squashing the offending instruction and all subsequent ones, as hinted by the `Squash` column).

* **Relationship Between Elements:** The `Auth` column is the likely cause of the blockage at the "X". The `Squash` column provides the mechanism to recover. The `Done` column shows which instructions are *logically* complete but cannot *architecturally* retire due to the blockage. The out-of-order engine may continue executing speculatively, but its results are trapped until the retirement blockage is cleared.

* **Anomaly and Purpose:** The primary anomaly is the blockage itself. This diagram is likely used to explain the microarchitectural handling of a security exception—such as a memory access violation, a compromised instruction, or a domain boundary crossing—within a high-performance CPU. It moves beyond pure performance modeling to illustrate **security-aware microarchitecture**. The `jop` labels might stand for "joint operation" or be a project-specific term for instruction entries in this secure context.