## Diagram: Model Checking Workflow for Fair Systems

### Overview

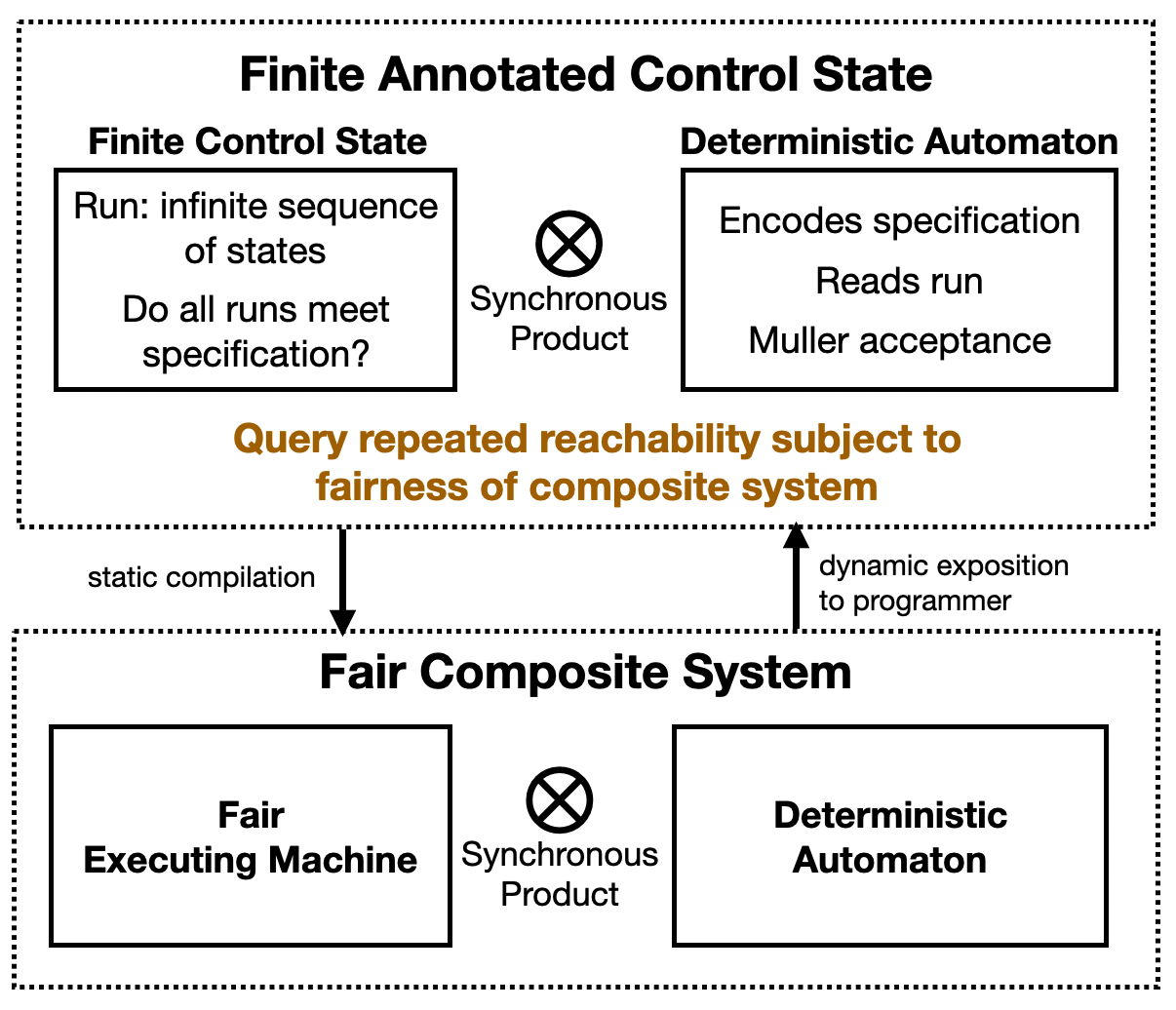

This block diagram illustrates a two-tiered architecture for formal verification, specifically focusing on how a high-level "Finite Annotated Control State" relates to a lower-level "Fair Composite System." The diagram outlines the components of each system, the mathematical operation used to combine them (Synchronous Product), and the bidirectional process of compilation and feedback between the two layers.

### Components/Axes

The diagram is divided into two primary regions enclosed in dashed rectangular borders, connected by vertical arrows.

**1. Top Region: Finite Annotated Control State**

* **Left Sub-component:** "Finite Control State" box.

* **Right Sub-component:** "Deterministic Automaton" box.

* **Central Operator:** A circle containing an 'X' ($\otimes$), labeled "Synchronous Product."

* **Bottom Annotation:** A line of text in brown/gold font.

**2. Middle Region: Transition Arrows**

* **Downward Arrow (Left):** Labeled "static compilation."

* **Upward Arrow (Right):** Labeled "dynamic exposition to programmer."

**3. Bottom Region: Fair Composite System**

* **Left Sub-component:** "Fair Executing Machine" box.

* **Right Sub-component:** "Deterministic Automaton" box.

* **Central Operator:** A circle containing an 'X' ($\otimes$), labeled "Synchronous Product."

---

### Content Details

#### Top Container: Finite Annotated Control State

* **Finite Control State (Left Box):**

* "Run: infinite sequence of states"

* "Do all runs meet specification?" (This is the core verification query).

* **Deterministic Automaton (Right Box):**

* "Encodes specification"

* "Reads run"

* "Muller acceptance" (Specifies the condition for accepting infinite sequences).

* **Operation:** The "Synchronous Product" ($\otimes$) combines the Finite Control State with the Deterministic Automaton.

* **Footer Text (Brown):** "Query repeated reachability subject to fairness of composite system"

#### Bottom Container: Fair Composite System

* **Fair Executing Machine (Left Box):** Represents the concrete implementation or a lower-level model that incorporates fairness constraints.

* **Deterministic Automaton (Right Box):** The same specification automaton used in the top layer.

* **Operation:** The "Synchronous Product" ($\otimes$) combines the Fair Executing Machine with the Deterministic Automaton.

#### Inter-layer Transitions

* **Static Compilation:** The process of transforming the abstract "Finite Annotated Control State" into the concrete "Fair Composite System."

* **Dynamic Exposition to Programmer:** The process of mapping results, counterexamples, or runtime data from the "Fair Composite System" back to the high-level "Finite Annotated Control State" for human interpretation.

---

### Key Observations

* **Symmetry of Specification:** The "Deterministic Automaton" appears in both the top and bottom containers, indicating that the formal specification remains constant while the system model is refined from an abstract control state to a fair executing machine.

* **Infinite Behavior:** The mention of "infinite sequence of states" and "Muller acceptance" confirms that this system is designed to verify liveness properties (things that must eventually happen) rather than just safety properties.

* **Fairness Integration:** The transition from the top to the bottom involves moving from a general query about runs to a specific query about "repeated reachability" under "fairness" constraints.

---

### Interpretation

This diagram describes a **Model Checking** framework.

1. **Abstraction and Specification:** At the top level, a programmer defines a high-level model (Finite Control State) and a property they want to check (Deterministic Automaton). The question is whether the system's infinite behaviors satisfy the property.

2. **The Product Construction:** The "Synchronous Product" is the standard way to combine a system model with a property automaton. The resulting product graph contains all possible behaviors of the system that are relevant to the property.

3. **Compilation to Fairness:** The "static compilation" step likely involves taking the high-level model and generating a more detailed, executable version that respects "fairness" (e.g., ensuring that if a process is ready to run, it will eventually be scheduled).

4. **Verification via Reachability:** The brown text indicates that the verification problem is solved by looking for "repeated reachability" (finding cycles in the product graph) that satisfy the Muller acceptance conditions and the fairness constraints of the machine.

5. **Closing the Loop:** The "dynamic exposition" is critical for usability. If the model checker finds a bug (a run that violates the spec), it must translate that low-level failure back into the high-level terms the programmer used to define the "Finite Annotated Control State."