## Architecture Diagram: Unified vs. Discrete Memory Architectures

### Overview

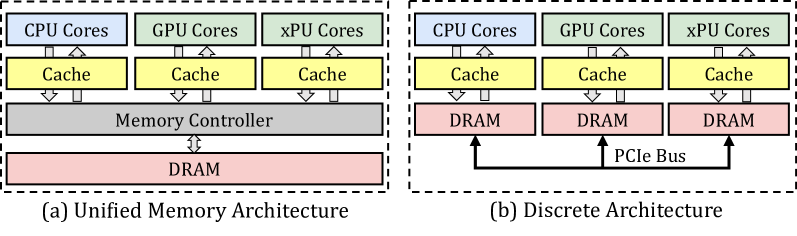

The image presents a comparative diagram of two memory architectures: Unified Memory Architecture (UMA) and Discrete Architecture. The diagrams illustrate the flow of data between CPU cores, GPU cores, xPU cores, cache, memory controller, DRAM, and PCIe bus.

### Components/Axes

* **Top Row (Both Architectures):**

* CPU Cores (light blue)

* GPU Cores (light green)

* xPU Cores (light green)

* **Second Row (Both Architectures):**

* Cache (yellow)

* **Unified Memory Architecture (Left):**

* Memory Controller (gray)

* DRAM (light red)

* **Discrete Architecture (Right):**

* DRAM (light red)

* PCIe Bus (black lines)

* **Labels:**

* (a) Unified Memory Architecture (bottom-left)

* (b) Discrete Architecture (bottom-right)

### Detailed Analysis

**Unified Memory Architecture (Left)**

* **CPU Cores, GPU Cores, xPU Cores:** The top row consists of three blocks: CPU Cores (light blue), GPU Cores (light green), and xPU Cores (light green).

* **Cache:** Below the cores is a row of three Cache blocks (yellow), each connected to the corresponding core above via bidirectional arrows.

* **Memory Controller:** Below the Cache blocks is a single Memory Controller block (gray). Bidirectional arrows connect each Cache block to the Memory Controller.

* **DRAM:** Below the Memory Controller is a single DRAM block (light red). A bidirectional arrow connects the Memory Controller to the DRAM.

**Discrete Architecture (Right)**

* **CPU Cores, GPU Cores, xPU Cores:** The top row consists of three blocks: CPU Cores (light blue), GPU Cores (light green), and xPU Cores (light green).

* **Cache:** Below the cores is a row of three Cache blocks (yellow), each connected to the corresponding core above via bidirectional arrows.

* **DRAM:** Below the Cache blocks is a row of three DRAM blocks (light red). Bidirectional arrows connect each Cache block to the corresponding DRAM block.

* **PCIe Bus:** Black lines representing the PCIe Bus connect each DRAM block to all three cores (CPU, GPU, and xPU).

### Key Observations

* **Unified Memory Architecture:** All cores share a single DRAM module via a memory controller.

* **Discrete Architecture:** Each core has dedicated DRAM modules, and communication between cores and DRAM occurs via the PCIe bus.

### Interpretation

The diagrams illustrate the fundamental difference between unified and discrete memory architectures. In a unified architecture, all processing units (CPU, GPU, xPU) share a single pool of memory (DRAM) managed by a memory controller. This simplifies memory management and allows for efficient data sharing between different processing units. However, it can also lead to bottlenecks if multiple processing units try to access the memory simultaneously.

In a discrete architecture, each processing unit has its own dedicated memory (DRAM). This eliminates the potential for memory bottlenecks but requires more complex memory management and data transfer mechanisms. The PCIe bus is used for communication between the processing units and their respective DRAM modules. This architecture is often used in high-performance systems where memory bandwidth is critical.