\n

## Diagram: Memory Architecture Comparison

### Overview

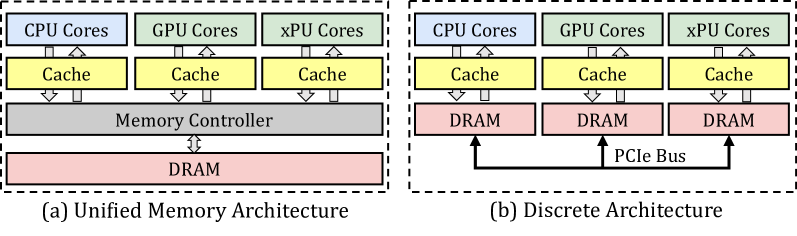

The image presents a comparison of two memory architectures: Unified Memory Architecture (a) and Discrete Architecture (b). Both diagrams illustrate the relationship between CPU Cores, GPU Cores, xPU Cores, Cache, Memory Controller, DRAM, and a PCIe Bus. The diagrams are presented side-by-side for direct comparison.

### Components/Axes

The components present in both diagrams are:

* **CPU Cores:** Represented by a light green rectangle.

* **GPU Cores:** Represented by a light green rectangle.

* **xPU Cores:** Represented by a light green rectangle.

* **Cache:** Represented by a yellow rectangle.

* **Memory Controller:** Represented by a grey rectangle.

* **DRAM:** Represented by a pink rectangle.

* **PCIe Bus:** Represented by a grey rectangle (only in diagram b).

The diagrams are labeled as follows:

* **(a) Unified Memory Architecture**

* **(b) Discrete Architecture**

Arrows indicate data flow between components.

### Detailed Analysis or Content Details

**Diagram (a): Unified Memory Architecture**

* CPU Cores, GPU Cores, and xPU Cores are positioned at the top of the diagram.

* Each core type has an associated Cache layer directly below it.

* The Cache layers are connected to a single Memory Controller via downward-pointing arrows.

* The Memory Controller is connected to a single DRAM module via bidirectional arrows.

* The overall structure suggests a shared memory space accessible by all core types.

**Diagram (b): Discrete Architecture**

* CPU Cores, GPU Cores, and xPU Cores are positioned at the top of the diagram, similar to diagram (a).

* Each core type has an associated Cache layer directly below it.

* Each Cache layer is connected to a separate DRAM module via downward-pointing arrows.

* The DRAM modules are connected via a PCIe Bus.

* The overall structure suggests separate memory spaces for each core type, connected through a PCIe bus.

### Key Observations

The primary difference between the two architectures is the memory access pattern. The Unified Memory Architecture (a) utilizes a single, shared memory pool (DRAM) accessed through a Memory Controller. The Discrete Architecture (b) employs separate DRAM modules for each core type, connected via a PCIe Bus. This implies that the Unified Architecture may offer lower latency and higher bandwidth for data sharing between core types, while the Discrete Architecture may provide greater memory isolation and scalability.

### Interpretation

The diagrams illustrate fundamental differences in how processing cores access memory. The Unified Memory Architecture aims to simplify memory management and improve data sharing, potentially at the cost of memory contention. The Discrete Architecture prioritizes memory isolation and scalability, potentially at the cost of increased latency and complexity due to the PCIe bus overhead. The choice between these architectures depends on the specific application requirements. For example, applications requiring frequent data exchange between CPU, GPU, and xPU cores might benefit from the Unified Architecture, while applications with independent memory access patterns might be better suited for the Discrete Architecture. The diagrams are conceptual and do not provide quantitative data on performance or capacity. They serve to visually represent the architectural differences and their potential implications.