## Flowchart: System Architecture for PowerPC 450 Simulation and Code Generation

### Overview

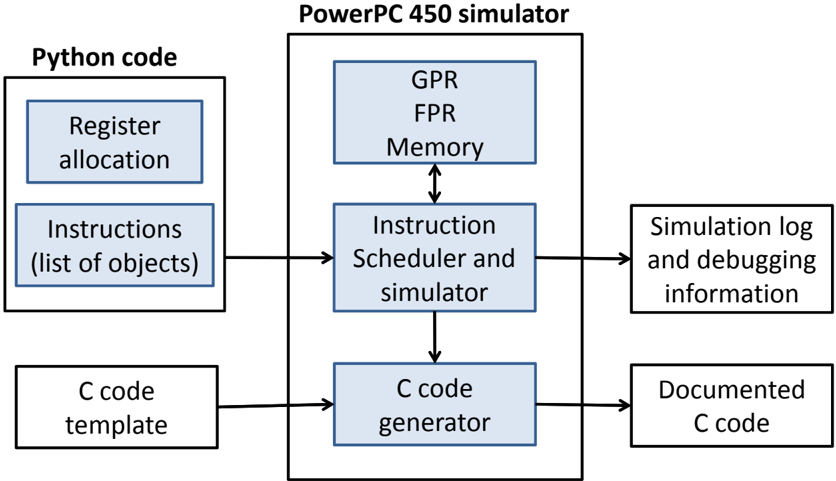

The diagram illustrates a workflow for simulating PowerPC 450 instructions using Python code and generating documented C code. The process involves register allocation, instruction scheduling, and memory management within a simulator, followed by C code generation.

### Components/Axes

1. **Python Code Block**:

- **Register allocation**: Light blue box with dark blue border.

- **Instructions (list of objects)**: Light blue box with dark blue border.

2. **PowerPC 450 Simulator Block**:

- **GPR/FPR/Memory**: Light blue box with dark blue border.

- **Instruction Scheduler and simulator**: Light blue box with dark blue border.

- **C code generator**: Light blue box with dark blue border.

3. **Outputs**:

- **Simulation log and debugging information**: Light gray box with dark gray border.

- **Documented C code**: Light gray box with dark gray border.

4. **Inputs**:

- **C code template**: Light gray box with dark gray border.

### Flow Direction

- Arrows indicate the following sequence:

1. Python code → PowerPC 450 simulator (GPR/FPR/Memory → Instruction Scheduler).

2. Simulator output → C code generator.

3. C code generator output → Documented C code and Simulation log.

### Key Observations

- The system bridges Python and C ecosystems via PowerPC simulation.

- The simulator acts as an intermediary, processing Python-defined instructions and register allocations.

- The C code generator produces both executable code and documentation, suggesting automated documentation generation.

### Interpretation

This architecture demonstrates a toolchain for:

1. **Simulation**: Translating Python-based PowerPC instructions into executable cycles via GPR/FPR/Memory management.

2. **Code Generation**: Converting simulated logic into optimized C code with embedded documentation.

3. **Debugging**: Providing simulation logs to trace execution paths and identify bottlenecks.

The bidirectional arrow between "Instruction Scheduler and simulator" and "C code generator" implies iterative refinement, where simulation results inform code optimization. The separation of "Simulation log and debugging information" suggests post-execution analysis capabilities, critical for low-level hardware emulation workflows.