\n

## Diagram: Memory Hierarchy Energy Consumption

### Overview

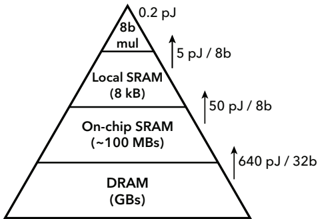

The image is a triangular diagram representing a memory hierarchy, illustrating the trade-off between memory size/distance from the processor and energy consumption per bit. The diagram shows four levels of memory: 8b multiplier, Local SRAM, On-chip SRAM, and DRAM, arranged from top to bottom, representing increasing size and distance from the processor. Energy consumption per bit increases as you move down the hierarchy.

### Components/Axes

The diagram consists of four horizontal layers, each representing a different memory type. Arrows indicate the energy consumption per bit for each level. The diagram does not have traditional axes, but the vertical position represents the distance from the processor (closer at the top, further at the bottom) and implicitly, the speed of access.

* **Top Layer:** 8b multiplier, labeled with "0.2 pJ"

* **Second Layer:** Local SRAM (8 kB), labeled with "5 pJ / 8b"

* **Third Layer:** On-chip SRAM (~100 MBs), labeled with "50 pJ / 8b"

* **Bottom Layer:** DRAM (GBs), labeled with "640 pJ / 32b"

### Detailed Analysis or Content Details

The diagram illustrates the energy cost associated with accessing different types of memory.

* **8b multiplier:** Consumes 0.2 picojoules (pJ).

* **Local SRAM (8 kB):** Consumes 5 pJ per 8 bits.

* **On-chip SRAM (~100 MBs):** Consumes 50 pJ per 8 bits.

* **DRAM (GBs):** Consumes 640 pJ per 32 bits.

The energy consumption increases significantly as you move down the memory hierarchy. The DRAM level has the highest energy consumption, while the 8b multiplier has the lowest. The units are not consistent across all levels (pJ vs. pJ/bit).

### Key Observations

* There is a clear trend of increasing energy consumption as memory size increases and distance from the processor grows.

* The energy consumption per bit is significantly higher for DRAM compared to the other memory levels.

* The diagram highlights the importance of using a memory hierarchy to optimize energy efficiency.

* The units are inconsistent, making direct comparison difficult. DRAM is measured in pJ/32b while the others are pJ/8b.

### Interpretation

This diagram demonstrates the fundamental principle behind memory hierarchies in computer architecture. Smaller, faster, and closer memory (like the 8b multiplier and Local SRAM) is more energy-efficient but also more expensive and limited in capacity. Larger, slower, and more distant memory (like DRAM) is cheaper and has higher capacity but consumes significantly more energy per access.

The diagram suggests that a well-designed memory hierarchy aims to keep frequently accessed data in the faster, more energy-efficient levels, minimizing the need to access the slower, more energy-intensive levels. The inconsistent units suggest a focus on illustrating the *relative* energy costs rather than precise absolute values. The use of approximate values (~100 MBs) for On-chip SRAM further reinforces this point.

The diagram is a simplified representation, but it effectively conveys the trade-offs involved in memory system design. It implies that optimizing energy consumption requires careful consideration of memory size, speed, and distance from the processor.