## Pyramid Diagram: Memory Hierarchy Energy Consumption

### Overview

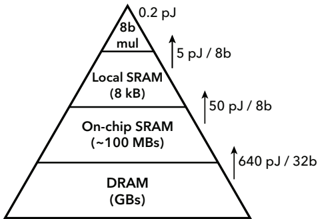

The image is a pyramid diagram illustrating the energy consumption associated with accessing different levels of a memory hierarchy. The pyramid is divided into layers representing different types of memory, with the top layer representing the fastest and most energy-efficient memory, and the bottom layer representing the slowest and least energy-efficient memory. Arrows indicate the energy cost per access as one moves up the memory hierarchy.

### Components/Axes

* **Layers (from top to bottom):**

* 8b mul (8-bit multiplier)

* Local SRAM (8 kB)

* On-chip SRAM (~100 MBs)

* DRAM (GBs)

* **Energy Consumption Labels:**

* 0.2 pJ (at the top layer)

* 5 pJ / 8b (arrow pointing from Local SRAM to 8b mul)

* 50 pJ / 8b (arrow pointing from On-chip SRAM to Local SRAM)

* 640 pJ / 32b (arrow pointing from DRAM to On-chip SRAM)

### Detailed Analysis

* **8b mul:** Located at the top of the pyramid, representing the smallest and fastest memory. Energy consumption is 0.2 pJ.

* **Local SRAM (8 kB):** The second layer from the top. Accessing data from this level to the 8b mul level costs 5 pJ / 8b.

* **On-chip SRAM (~100 MBs):** The third layer from the top. Accessing data from this level to the Local SRAM level costs 50 pJ / 8b.

* **DRAM (GBs):** The bottom layer of the pyramid, representing the largest and slowest memory. Accessing data from this level to the On-chip SRAM level costs 640 pJ / 32b.

### Key Observations

* Energy consumption increases significantly as one moves down the memory hierarchy from faster, smaller memory to slower, larger memory.

* The energy cost of accessing DRAM is significantly higher than accessing SRAM or the 8b multiplier.

### Interpretation

The diagram illustrates the trade-off between memory size, speed, and energy consumption. Faster memory (like the 8b multiplier and SRAM) is smaller and consumes less energy, while slower memory (like DRAM) is larger but consumes significantly more energy per access. This highlights the importance of memory hierarchy design in optimizing performance and energy efficiency in computing systems. The pyramid shape visually emphasizes the increasing cost of accessing lower levels of the memory hierarchy.