## Diagram: Memory Hierarchy and Compute Core Architecture

### Overview

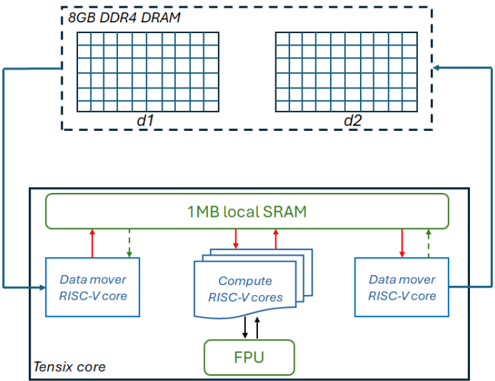

The diagram illustrates a memory hierarchy and compute core architecture, featuring DDR4 DRAM, local SRAM, RISC-V cores, and an FPU. It emphasizes data flow between memory layers and processing units, with spatial grounding of components.

### Components/Axes

- **Top Section**:

- **8GB DDR4 DRAM**: Divided into two regions labeled `d1` and `d2`, represented as grid structures.

- **Connections**: Blue lines link DDR4 DRAM to the lower section (SRAM and cores).

- **Middle Section**:

- **1MB Local SRAM**: Central horizontal green rectangle.

- **Data Mover RISC-V Cores**: Two blue rectangles on the left and right, labeled "Data mover RISC-V core."

- **Compute RISC-V Cores**: Stacked blue rectangles in the center, labeled "Compute RISC-V cores."

- **Bottom Section**:

- **FPU**: Green rectangle at the base, connected to the compute cores.

- **Tensix Core**: Blue rectangle on the far left, connected to the left data mover.

### Detailed Analysis

- **Memory Hierarchy**:

- **DDR4 DRAM (8GB)**: Topmost layer, split into `d1` and `d2` (no explicit size breakdown provided).

- **Local SRAM (1MB)**: Intermediate layer, acting as a cache between DDR4 and compute units.

- **Compute Units**:

- **Data Movers**: Facilitate data transfer between DDR4 and SRAM (left and right sides).

- **Compute RISC-V Cores**: Central processing units, stacked to indicate parallelism.

- **FPU**: Floating-point unit at the bottom, receiving processed data from compute cores.

- **Flow**:

- Data moves from DDR4 (`d1`/`d2`) to SRAM via data movers.

- SRAM supplies data to compute cores, which process it and send results to the FPU.

- The Tensix core orchestrates the system, connected to the left data mover.

### Key Observations

- **Spatial Grounding**:

- DDR4 DRAM is positioned at the top, SRAM in the middle, and FPU at the bottom, reflecting a vertical hierarchy.

- Data movers flank the compute cores, emphasizing their role in data transfer.

- **Color Coding**:

- Blue: DDR4 DRAM, data movers, Tensix core.

- Green: Local SRAM, FPU.

- Red: Arrows indicating data flow (not explicitly labeled in the diagram).

- **Component Relationships**:

- The Tensix core initiates operations, directing data to the left data mover.

- Compute cores are centrally located, suggesting their critical role in processing.

### Interpretation

The diagram represents a **memory-centric compute architecture** optimized for efficiency. The 8GB DDR4 DRAM serves as the primary memory, with 1MB local SRAM acting as a high-speed cache to reduce latency. The data movers (RISC-V cores) bridge DDR4 and SRAM, minimizing direct access to slower main memory. The compute cores and FPU form the processing layer, handling parallel tasks and floating-point operations. The Tensix core likely acts as the system controller, coordinating data flow and task scheduling. This architecture prioritizes minimizing data movement bottlenecks, a common challenge in high-performance computing. The absence of explicit clock speeds or latency metrics suggests the focus is on structural design rather than performance benchmarks.