\n

## System Architecture Diagram: Multiprocessor System with Centralized Controller

### Overview

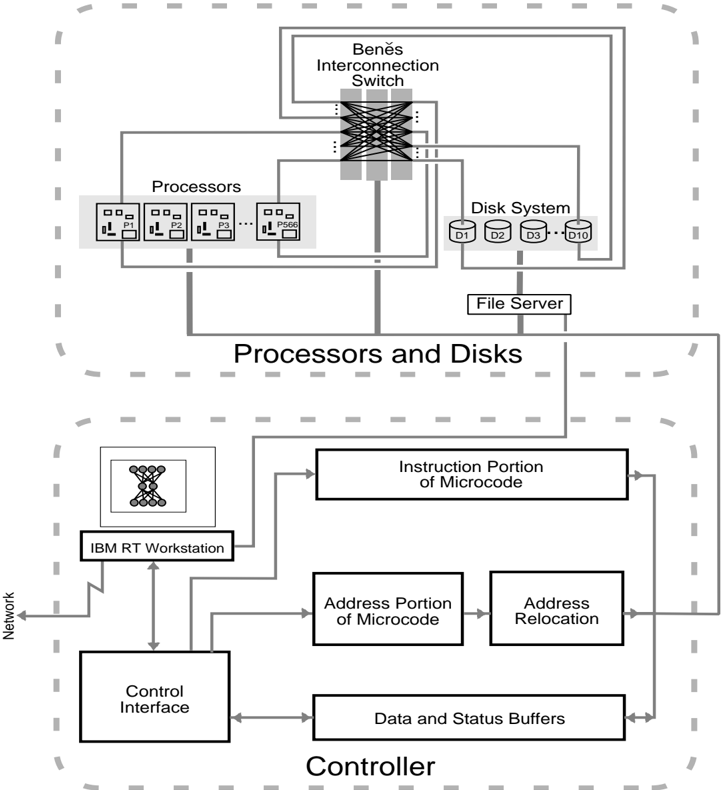

The image is a technical block diagram illustrating the architecture of a multiprocessor computing system. It is divided into two primary sections, each enclosed by a dashed gray border: an upper section labeled "Processors and Disks" and a lower section labeled "Controller." The diagram shows the interconnection of processing units, storage, and control logic, with data and control paths indicated by solid lines and arrows.

### Components/Axes

The diagram is not a chart with axes but a schematic of system components. The key labeled components and their spatial relationships are:

**Upper Section: "Processors and Disks" (Top half of the image)**

* **Beněs Interconnection Switch:** Located at the top-center. This is a crossbar-style switch depicted with a grid of intersecting lines, indicating a fully connected network.

* **Processors:** A block on the left side containing icons representing individual processors. They are labeled sequentially: **P1, P2, P3, ... P568**. This indicates a large-scale system with up to 568 processors.

* **Disk System:** A block on the right side containing icons representing disk drives. They are labeled sequentially: **D1, D2, D4, ... D10**. The jump from D2 to D4 suggests the list is not exhaustive, implying a variable number of disks (likely at least 10).

* **File Server:** A rectangular block positioned below the Disk System.

* **Connections:** Lines connect the Processors and the Disk System/File Server to the central Beněs Interconnection Switch. A thicker gray line connects the "Processors and Disks" section to the "Controller" section below.

**Lower Section: "Controller" (Bottom half of the image)**

* **IBM RT Workstation:** A component on the left side, depicted with a monitor icon showing a network symbol. It is connected to an external "Network" via a jagged line on its left.

* **Control Interface:** A large block below the IBM RT Workstation.

* **Microcode and Processing Blocks:** A series of rectangular blocks to the right of the Control Interface, connected by arrows indicating data/control flow:

* **Instruction Portion of Microcode** (Top block)

* **Address Portion of Microcode** (Middle-left block)

* **Address Relocation** (Middle-right block, receiving input from "Address Portion of Microcode")

* **Data and Status Buffers** (Bottom block)

* **Flow Arrows:** Arrows show the following pathways:

1. From the IBM RT Workstation to the "Instruction Portion of Microcode."

2. From the Control Interface to the "Address Portion of Microcode."

3. From "Address Portion of Microcode" to "Address Relocation."

4. From "Instruction Portion of Microcode" and "Address Relocation" to the "Data and Status Buffers."

5. Bidirectional arrows connect the "Data and Status Buffers" to the "Control Interface."

6. A line from the "Data and Status Buffers" extends upward to connect to the "Processors and Disks" section.

### Detailed Analysis

* **Text Transcription:** All text in the diagram is in English. The complete list of extracted labels is:

* Beněs Interconnection Switch

* Processors

* P1, P2, P3, ... P568

* Disk System

* D1, D2, D4, ... D10

* File Server

* Processors and Disks

* IBM RT Workstation

* Network

* Control Interface

* Instruction Portion of Microcode

* Address Portion of Microcode

* Address Relocation

* Data and Status Buffers

* Controller

* **Spatial Grounding:** The "Beněs Interconnection Switch" is the central hub in the upper section. The "Processors" are grouped to its left, and the "Disk System" to its right. The "Controller" section is physically separated below, with the "IBM RT Workstation" on its left edge acting as the user/network gateway. The "Data and Status Buffers" block is the central nexus within the controller, connecting to all other internal blocks and the external system.

* **Component Isolation:** The diagram is cleanly segmented into the two major subsystems (Processors/Disks and Controller), with a clear hierarchical and data-flow relationship between them.

### Key Observations

1. **Scale:** The system is designed for massive parallelism, explicitly labeling processors up to P568.

2. **Interconnection:** The use of a "Beněs Interconnection Switch" (a type of non-blocking crossbar network) is critical for enabling high-bandwidth, low-latency communication between a large number of processors and shared disks.

3. **Centralized Control:** All processing and disk activity appears to be managed by a single, complex "Controller" subsystem, which itself is driven by microcode split into instruction and address portions.

4. **Memory/Address Management:** The presence of an "Address Relocation" unit suggests the system uses virtual memory or some form of dynamic address translation.

5. **Historical Context:** The reference to an "IBM RT Workstation" (IBM RT PC, a workstation from the mid-1980s) dates this architecture to the late 1980s or early 1990s.

### Interpretation

This diagram represents a **high-performance, shared-memory multiprocessor system architecture from the late 1980s/early 1990s**. The data suggests the following:

* **Purpose:** The system is designed for computationally intensive tasks that can be parallelized across hundreds of processors (e.g., scientific simulation, large-scale data processing). The centralized disk system and file server indicate a need for shared, high-capacity storage accessible to all processors.

* **Relationships:** The "Controller" is the brain of the operation. It receives commands from the user/network via the IBM RT Workstation, translates them into microcode operations, manages memory addressing, and coordinates the flow of data and status information between itself and the vast array of processors and disks through the high-speed Beněs switch.

* **Notable Anomaly/Insight:** The split of microcode into separate "Instruction" and "Address" portions, which then feed into a dedicated "Address Relocation" unit, highlights the complexity of memory management in such a large system. This separation was likely a hardware optimization to speed up the critical path of instruction execution and memory access. The entire controller acts as a sophisticated, custom-designed front-end processor, offloading all management overhead from the main processor farm. This architecture is a precursor to modern concepts like NUMA (Non-Uniform Memory Access) and the use of dedicated management controllers in large-scale systems.