## Diagram: WriteEnSel and WriteData Control Flow

### Overview

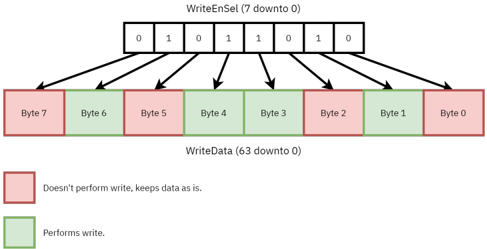

The diagram illustrates a control mechanism for writing data to a memory or storage system. It shows how an 8-bit enable signal (`WriteEnSel`) determines which of 8 bytes in a 64-bit data bus (`WriteData`) are written. The system uses color-coded indicators (red/green) to represent write activity.

### Components/Axes

1. **Top Section**:

- **Label**: `WriteEnSel (7 downto 0)`

- **Content**: 8-bit binary values: `0 1 0 1 1 0 1 0`

- **Purpose**: Control signal determining write enable for each byte.

2. **Bottom Section**:

- **Label**: `WriteData (63 downto 0)`

- **Content**: 8 bytes (Byte 7 to Byte 0), each represented as a colored box.

- **Color Legend**:

- **Red**: "Doesn't perform write, keeps data as is."

- **Green**: "Performs write."

3. **Arrows**:

- Connect each bit in `WriteEnSel` to its corresponding byte in `WriteData`.

- Spatial grounding: Arrows originate from the top section and point downward to the bottom section.

### Detailed Analysis

- **WriteEnSel Bits**:

- Bit 7: `0` → Byte 7 (red, no write).

- Bit 6: `1` → Byte 6 (green, write).

- Bit 5: `0` → Byte 5 (red, no write).

- Bit 4: `1` → Byte 4 (green, write).

- Bit 3: `1` → Byte 3 (green, write).

- Bit 2: `0` → Byte 2 (red, no write).

- Bit 1: `1` → Byte 1 (green, write).

- Bit 0: `0` → Byte 0 (red, no write).

- **WriteData Bytes**:

- Bytes are labeled from left (Byte 7) to right (Byte 0).

- Colors match the `WriteEnSel` bits:

- Green bytes (6, 4, 3, 1) correspond to `WriteEnSel` bits set to `1`.

- Red bytes (7, 5, 2, 0) correspond to `WriteEnSel` bits set to `0`.

### Key Observations

1. **Direct Mapping**: Each bit in `WriteEnSel` controls exactly one byte in `WriteData`.

2. **Write Pattern**:

- Alternating writes with exceptions: Bytes 3 and 4 are both written (bits 3 and 4 are `1`).

- Total writes: 4 bytes (Bytes 6, 4, 3, 1).

3. **Spatial Logic**:

- Legend is positioned at the bottom, clearly associating colors with write states.

- Arrows ensure unambiguous mapping between control bits and data bytes.

### Interpretation

This diagram represents a **byte-select write enable mechanism** commonly used in memory interfaces (e.g., DDR SDRAM, storage controllers). The `WriteEnSel` signal acts as a mask, enabling writes to specific bytes in the `WriteData` bus. For example:

- When `WriteEnSel` is `01011010`, Bytes 6, 4, 3, and 1 are updated, while others retain their previous values.

- The use of color coding simplifies visual debugging of write operations.

**Notable Insight**: The consecutive `1`s in `WriteEnSel` (bits 3 and 4) indicate that adjacent bytes (Byte 3 and 4) are written simultaneously, which may reflect alignment requirements or burst-write operations in the underlying hardware.