## Logic Circuit Diagram: AND-OR Gate Network

### Overview

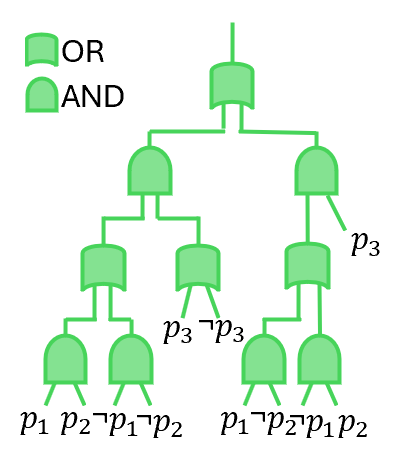

The image displays a hierarchical digital logic circuit diagram composed of interconnected AND and OR gates. The circuit is structured as a tree, with inputs at the bottom and a single output at the top. The diagram uses a consistent green color for all gate symbols. A legend in the top-left corner defines the gate symbols.

### Components/Axes

* **Legend (Top-Left):**

* **OR Gate:** Represented by a green rectangle with a curved top edge. Label: "OR".

* **AND Gate:** Represented by a green rectangle with a flat top edge. Label: "AND".

* **Circuit Structure:** The diagram is organized into four distinct horizontal levels or layers of gates.

* **Input Labels (Bottom Row):** A series of logical variables and their negations are labeled beneath the bottom-most gates. From left to right, they are: `p1`, `p2`, `¬p1`, `¬p2`, `p3`, `¬p3`, `p1`, `¬p2`, `p1`, `p2`.

* **Intermediate Label:** The variable `p3` is also labeled as a direct input to a gate on the right side of the second level from the top.

### Detailed Analysis

**Component Isolation & Flow:**

The circuit processes signals from the bottom (inputs) to the top (output). The flow can be segmented into left and right main branches originating from the top gate.

1. **Top Level (Output):** A single **OR gate**. Its output is the final circuit output.

2. **Second Level:** Two **AND gates** feed into the top OR gate.

* The **left AND gate** receives inputs from two OR gates on the third level.

* The **right AND gate** receives one input from an OR gate on the third level and one direct input labeled `p3`.

3. **Third Level:** Three **OR gates**.

* The **leftmost OR gate** receives inputs from two AND gates on the bottom level.

* The **middle OR gate** receives inputs from two AND gates on the bottom level.

* The **rightmost OR gate** receives inputs from two AND gates on the bottom level.

4. **Bottom Level (Inputs):** Six **AND gates**. Each AND gate has two input lines. The labels beneath these gates indicate the logical variables applied to those input lines. The grouping is as follows:

* Gate 1 (Leftmost): Inputs `p1` and `p2`.

* Gate 2: Inputs `¬p1` and `¬p2`.

* Gate 3: Inputs `p3` and `¬p3`.

* Gate 4: Inputs `p1` and `¬p2`.

* Gate 5: Inputs `p1` and `p2`.

* Gate 6 (Rightmost): This gate's inputs are not explicitly labeled with new variables; it appears to be a duplicate or continuation of the pattern.

**Transcription of Embedded Text:**

* Legend: `OR`, `AND`

* Input Labels (Bottom, left to right): `p1`, `p2`, `¬p1`, `¬p2`, `p3`, `¬p3`, `p1`, `¬p2`, `p1`, `p2`

* Intermediate Label: `p3` (connected to the right AND gate on the second level).

### Key Observations

* **Structural Symmetry:** The left and right main branches of the circuit are not perfectly symmetrical. The right branch has a direct `p3` input at the second level, while the left branch does not.

* **Input Repetition:** The variables `p1` and `p2` (and their negations) are used multiple times across different bottom-level gates. The variable `p3` and its negation appear only once as a paired input to a single bottom-level gate.

* **Gate Type Pattern:** The circuit alternates between layers of AND gates and OR gates, characteristic of a two-level logic implementation (like Sum-of-Products), though this specific structure is deeper.

* **Logical Completeness:** The bottom-level AND gates generate all four possible minterms for variables `p1` and `p2`: `(p1·p2)`, `(¬p1·¬p2)`, `(p1·¬p2)`, and a second instance of `(p1·p2)`. The minterm `(¬p1·p2)` is not explicitly generated.

### Interpretation

This diagram represents a specific Boolean logic function implemented with discrete AND and OR gates. The structure suggests it is computing a complex logical expression.

* **Function Derivation:** By tracing the signals upward, the circuit's output can be expressed as a Boolean equation. The top OR gate combines the results from the two main branches. Each branch is an AND of sub-expressions from the level below. This ultimately results in a **Product-of-Sums (POS)** or a more complex multi-level expression, rather than a simple Sum-of-Products.

* **Purpose of Structure:** The hierarchical, tree-like organization is typical for visualizing the evaluation order of a logical formula. It breaks down a complex expression into simpler, nested operations.

* **Notable Anomaly:** The absence of the minterm `(¬p1·p2)` in the bottom layer indicates that the function being implemented does not require this specific combination of `p1` and `p2` to be true for its evaluation, or that this condition is covered by another part of the circuit's logic. The duplicate `(p1·p2)` gate is unusual and may be a diagrammatic error or represent a specific design choice for signal loading or fan-in.

* **Overall Meaning:** The circuit is a physical or logical realization of a Boolean function involving three variables (`p1`, `p2`, `p3`). Its exact function would require writing out the full equation by tracing all paths from inputs to the final output gate. The diagram serves as a technical blueprint for constructing this logic network.