## Hardware Implementations of Probabilistic Bits and Hybrid Computer Architecture

### Overview

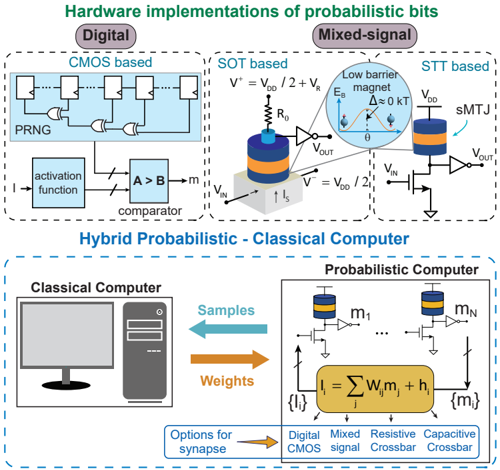

The image presents a diagram illustrating hardware implementations of probabilistic bits using digital and mixed-signal approaches, along with a hybrid probabilistic-classical computer architecture. It details CMOS-based, SOT-based, and STT-based implementations, and shows how a classical computer can interface with a probabilistic computer.

### Components/Axes

**Header:**

* Title: "Hardware implementations of probabilistic bits"

* Categories: "Digital" and "Mixed-signal" are distinguished by rounded boxes.

**Digital Implementation (Left):**

* CMOS based:

* PRNG (Pseudo-Random Number Generator): A series of flip-flops connected with XOR gates.

* Activation function: A block labeled "activation function" takes an input "I".

* Comparator: A comparator block labeled "A > B" with inputs from the activation function and PRNG, and output "m".

**Mixed-Signal Implementations (Right):**

* SOT based:

* Equation: V+ = VDD / 2 + VR

* Resistor: Labeled R0.

* MTJ (Magnetic Tunnel Junction): A cylinder with alternating blue and orange layers.

* Input: VIN

* Output: VOUT

* Current: Is

* Equation: V- = VDD / 2

* Low barrier magnet: A circular inset showing a potential energy landscape with two minima, labeled Eb and Δ ≈ 0 kT, and angle θ.

* STT based:

* sMTJ (spintransfer-torque Magnetic Tunnel Junction): A cylinder with alternating blue and orange layers.

* Voltage: VDD

* Input: VIN

* Output: VOUT

**Hybrid Probabilistic - Classical Computer (Bottom):**

* Title: "Hybrid Probabilistic - Classical Computer"

* Classical Computer: A representation of a computer monitor and tower.

* Probabilistic Computer:

* Multiple MTJ-based probabilistic bit implementations (m1 to mN).

* Equation: Ii = Σj Wijmj + hi

* Inputs: {li}

* Outputs: {mi}

* Arrows:

* "Samples" (blue arrow) flows from the Probabilistic Computer to the Classical Computer.

* "Weights" (orange arrow) flows from the Classical Computer to the Probabilistic Computer.

* Options for synapse: An arrow pointing to a table with the following categories: Digital CMOS, Mixed signal, Resistive Crossbar, Capacitive Crossbar.

### Detailed Analysis or ### Content Details

**Digital Implementation:**

* The CMOS-based implementation uses a PRNG to generate random bits.

* An activation function processes an input signal "I".

* A comparator compares the output of the activation function with the PRNG output to generate a probabilistic bit "m".

**Mixed-Signal Implementations:**

* The SOT-based implementation uses a Spin-Orbit Torque (SOT) device. The voltage V+ is defined as VDD/2 + VR.

* The STT-based implementation uses a Spin-Transfer Torque (STT) device.

* Both SOT and STT implementations use MTJs to represent probabilistic bits.

**Hybrid Computer Architecture:**

* The Classical Computer and Probabilistic Computer exchange information.

* The Classical Computer sends "Weights" to the Probabilistic Computer.

* The Probabilistic Computer sends "Samples" to the Classical Computer.

* The probabilistic computer calculates Ii as the sum of Wijmj + hi, where Wij are weights, mj are probabilistic bits, and hi are biases.

* Synapse options include Digital CMOS, Mixed signal, Resistive Crossbar, and Capacitive Crossbar.

### Key Observations

* The diagram illustrates different hardware approaches to implement probabilistic bits.

* The hybrid architecture combines classical and probabilistic computing paradigms.

* The mixed-signal implementations leverage spintronic devices (SOT and STT) and MTJs.

### Interpretation

The diagram presents a vision for integrating probabilistic computing with classical computing. The different hardware implementations of probabilistic bits (CMOS, SOT, STT) offer various trade-offs in terms of speed, power consumption, and area. The hybrid architecture allows leveraging the strengths of both classical and probabilistic computing, potentially enabling new applications in areas such as machine learning, optimization, and cryptography. The "Options for synapse" suggest different ways to implement the connections between probabilistic bits, each with its own advantages and disadvantages.