## Code Snippet with Annotations: Configurable Systolic Array Design

### Overview

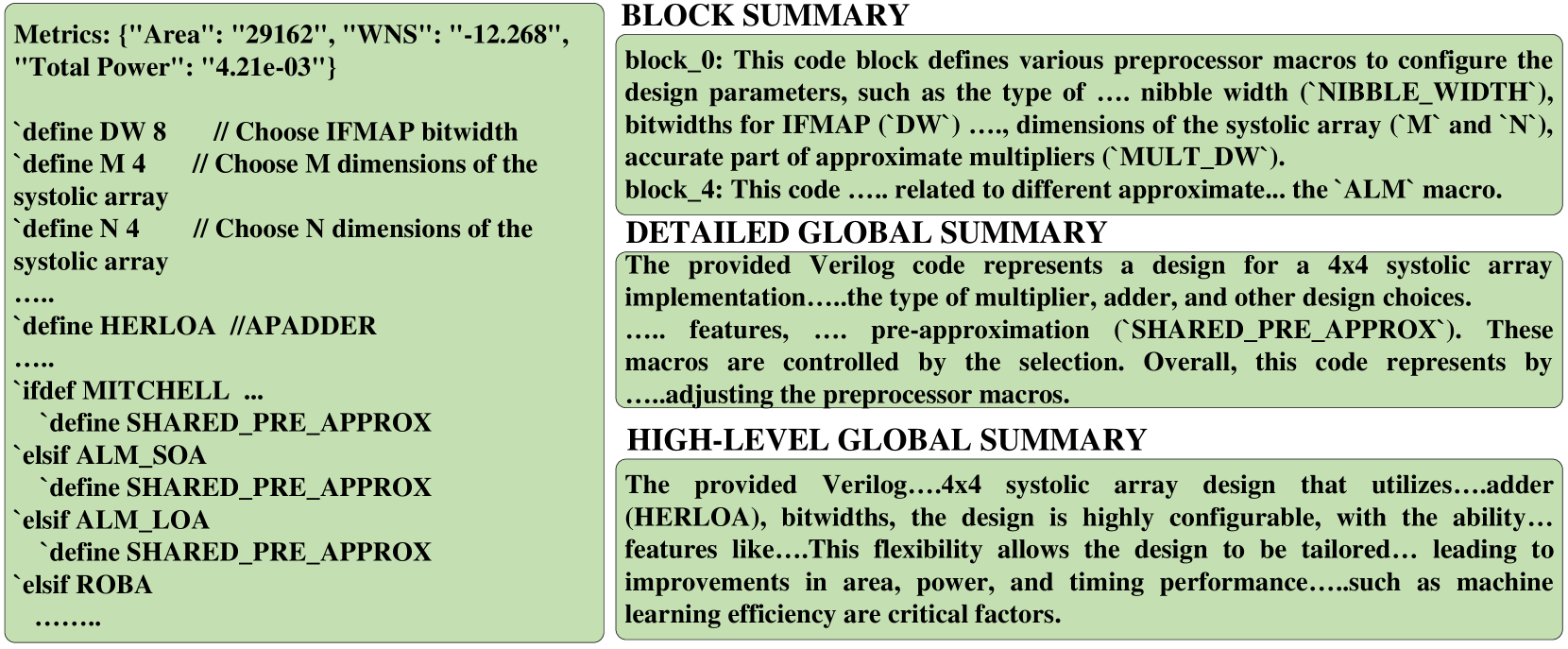

The image displays a two-panel technical document. The left panel contains a block of Verilog preprocessor code and associated design metrics. The right panel provides three levels of textual summary (Block, Detailed Global, and High-Level Global) that describe the purpose and functionality of the code. The document appears to be an annotated output from a hardware design or analysis tool.

### Components/Axes

The image is segmented into two primary regions:

1. **Left Panel (Code & Metrics):**

* **Header Line:** A JSON-formatted string containing design metrics.

* **Code Block:** A series of Verilog preprocessor `` `define `` and conditional compilation directives (`` `ifdef ``, `` `elsif ``). Comments are denoted by `//`.

* **Ellipses (`......`):** Indicate omitted or truncated code sections.

2. **Right Panel (Summaries):**

* **Three distinct summary boxes** with bold headers:

* `BLOCK SUMMARY`

* `DETAILED GLOBAL SUMMARY`

* `HIGH-LEVEL GLOBAL SUMMARY`

* Each summary contains descriptive text with ellipses (`.....`) indicating where content has been truncated or summarized.

### Detailed Analysis

#### Left Panel: Code and Metrics

* **Metrics Line:**

`Metrics: {"Area": "29162", "WNS": "-12.268", "Total Power": "4.21e-03"}`

* **Area:** 29162 (unit unspecified, likely square micrometers or gate equivalents).

* **WNS (Worst Negative Slack):** -12.268 (unit unspecified, likely nanoseconds). A negative value indicates a timing violation.

* **Total Power:** 4.21e-03 (4.21 milliwatts, assuming standard units).

* **Code Definitions:**

* `` `define DW 8 `` // Choose IFMAP bitwidth

* `` `define M 4 `` // Choose M dimensions of the systolic array

* `` `define N 4 `` // Choose N dimensions of the systolic array

* ``......`` (Omitted code)

* `` `define HERLOA //APADDER ``

* ``......`` (Omitted code)

* Conditional Compilation Block:

* `` `ifdef MITCHELL ... ``

* `` `define SHARED_PRE_APPROX ``

* `` `elsif ALM_SOA ``

* `` `define SHARED_PRE_APPROX ``

* `` `elsif ALM_LOA ``

* `` `define SHARED_PRE_APPROX ``

* `` `elsif ROBA ``

* ``.......`` (Omitted code)

#### Right Panel: Summaries

* **BLOCK SUMMARY:**

* `block_0`: Describes preprocessor macros for design parameters: nibble width (`NIBBLE_WIDTH`), IFMAP bitwidth (`DW`), systolic array dimensions (`M` and `N`), and accurate part of approximate multipliers (`MULT_DW`).

* `block_4`: Mentions code related to different approximate... and the `ALM` macro.

* **DETAILED GLOBAL SUMMARY:**

States the Verilog code represents a design for a **4x4 systolic array implementation**. It mentions choices for multiplier type, adder, and other design features, including a pre-approximation feature (`SHARED_PRE_APPROX`). These macros are controlled by selection. The overall design is adjusted via preprocessor macros.

* **HIGH-LEVEL GLOBAL SUMMARY:**

Describes the code as a **4x4 systolic array design** that utilizes an adder (HERLOA). It emphasizes the design is **highly configurable** via bitwidths and other features. This flexibility allows tailoring for improvements in **area, power, and timing performance**, which are critical for factors like machine learning efficiency.

### Key Observations

1. **Configurability:** The core theme is a highly parameterizable hardware design. Key parameters (bitwidth `DW`, array dimensions `M`x`N`) are defined as macros, allowing easy reconfiguration without rewriting core logic.

2. **Approximate Computing Focus:** The code and summaries repeatedly reference "approximate" multipliers and pre-approximation (`SHARED_PRE_APPROX`). The conditional compilation block (`MITCHELL`, `ALM_SOA`, `ALM_LOA`, `ROBA`) suggests support for multiple approximate arithmetic algorithms.

3. **Performance Metrics:** The provided metrics (Area, WNS, Power) are the direct outputs of synthesizing or implementing this configurable design with a specific set of macro definitions.

4. **Hierarchical Summarization:** The right panel demonstrates an automated or tool-generated summarization process, moving from specific block-level details to a high-level overview of the design's purpose and value.

### Interpretation

This image captures a snapshot of a **design-space exploration** for a hardware accelerator, likely for neural network inference. The systolic array is a common architecture for matrix multiplication, a core operation in machine learning.

* **The "Why":** The configurable macros allow designers to rapidly evaluate trade-offs. For example, changing `DW` from 8 to 4 bits would reduce area and power but potentially increase error due to lower precision. Selecting different approximate multipliers (`MITCHELL` vs. `ALM_SOA`) trades off computational accuracy for gains in power and area.

* **The Data's Story:** The negative Worst Negative Slack (`WNS: -12.268`) is a critical observation. It indicates that for the current configuration, the design **fails to meet its timing constraints** at the target clock frequency. This is a major red flag in hardware design, meaning the circuit would not function correctly at the desired speed. The designer must now use the configurability—perhaps by reducing bitwidths, simplifying the approximate multiplier, or pipelining—to improve timing (make WNS less negative or positive) while balancing the impact on Area and Power.

* **Underlying Goal:** The summaries explicitly link this configurability to "machine learning efficiency." The ultimate objective is to find a "sweet spot" in the design space where the hardware accelerator provides sufficient computational accuracy for a given ML model while minimizing resource consumption (area, power) and meeting performance (timing) targets. This image shows one data point in that extensive search process.