## Screenshot: Verilog Code with Design Summaries

### Overview

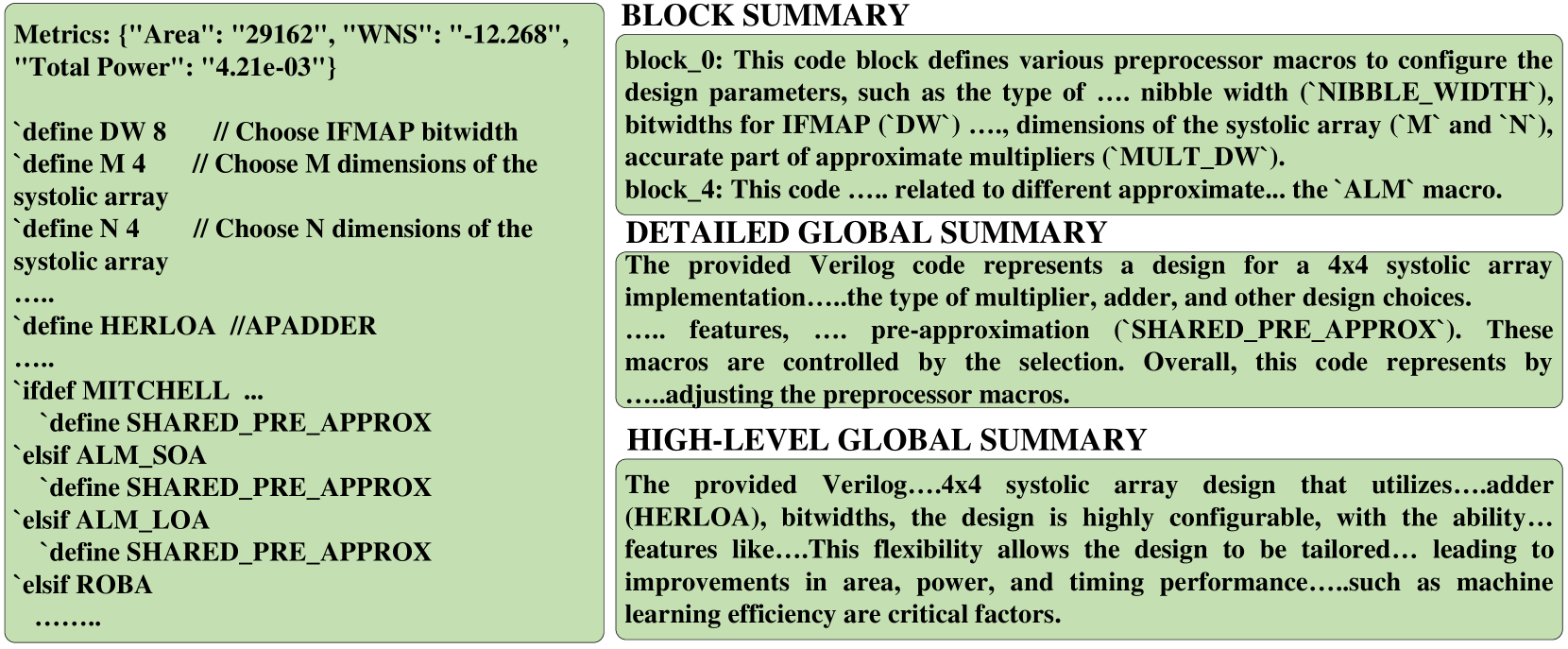

The image shows a Verilog code snippet with embedded comments and three global summaries. The left side contains metrics, design parameters, and conditional macros, while the right side provides block-level and high-level design explanations.

### Components/Axes

- **Left Panel (Code/Metrics):**

- **Metrics:**

- `"Area": "29162"`

- `"WNS": "-12.268"`

- `"Total Power": "4.21e-03"`

- **Design Parameters:**

- `\`define DW 8` (IFMAP bitwidth)

- `\`define M 4` (Systolic array M-dimension)

- `\`define N 4` (Systolic array N-dimension)

- `\`define HERLOA //APADDER` (Multiplier type)

- Conditional macros:

- `\`ifdef MITCHELL`

- `\`define SHARED_PRE_APPROX`

- `\`elseif ALM_SOA`

- `\`define SHARED_PRE_APPROX`

- `\`elseif ALM_LOA`

- `\`define SHARED_PRE_APPROX`

- `\`elseif ROBA`

- **Right Panel (Summaries):**

1. **Block Summary:**

- Describes preprocessor macros for design parameters (e.g., `NIBBLE_WIDTH`, systolic array dimensions `M`/`N`, approximate multipliers `MULT_DW`).

- Mentions the `ALM` macro for approximate multipliers.

2. **Detailed Global Summary:**

- Explains the 4x4 systolic array implementation, including multiplier type (`HERLOA`), adder, and pre-approximation (`SHARED_PRE_APPROX`).

- Notes that macros are controlled by selections (e.g., `MITCHELL`, `ALM_SOA`).

3. **High-Level Global Summary:**

- Highlights the configurable 4x4 systolic array design with adjustable features (adder, HERLOA, bitwidths).

- Emphasizes trade-offs between area, power, and timing for machine learning efficiency.

### Detailed Analysis

- **Metrics:**

- Area: 29,162 (exact value, no uncertainty).

- WNS: -12.268 (likely timing slack, negative indicates violation).

- Total Power: 0.00421 (scientific notation, ~4.21 mW).

- **Code Structure:**

- Conditional compilation (`\`ifdef`, `\`elseif`) allows selecting design variants (e.g., `MITCHELL`, `ALM_SOA`).

- `SHARED_PRE_APPROX` is defined across all branches, suggesting a shared approximation strategy.

- **Design Choices:**

- Systolic array dimensions: 4x4 (fixed via `\`define M 4` and `\`define N 4`).

- Multiplier type: `HERLOA` (APADDER) with optional pre-approximation.

### Key Observations

1. **Configurable Design:** The code prioritizes flexibility via preprocessor macros, enabling trade-offs between area, power, and performance.

2. **Approximation Focus:** `SHARED_PRE_APPROX` is consistently defined, indicating its importance in optimizing resource usage.

3. **Timing Constraints:** Negative WNS (-12.268) suggests timing violations, requiring optimization.

### Interpretation

The Verilog code represents a highly configurable systolic array design for machine learning acceleration. By adjusting parameters like multiplier type (`HERLOA`), bitwidths (`DW`), and pre-approximation strategies (`SHARED_PRE_APPROX`), the design balances area, power, and timing. The negative WNS highlights a critical timing issue that must be resolved to meet performance targets. The 4x4 systolic array structure and conditional macros suggest a focus on scalability and adaptability for different computational workloads.