## System Architecture Diagram: Virtualization and Hardware Interaction

### Overview

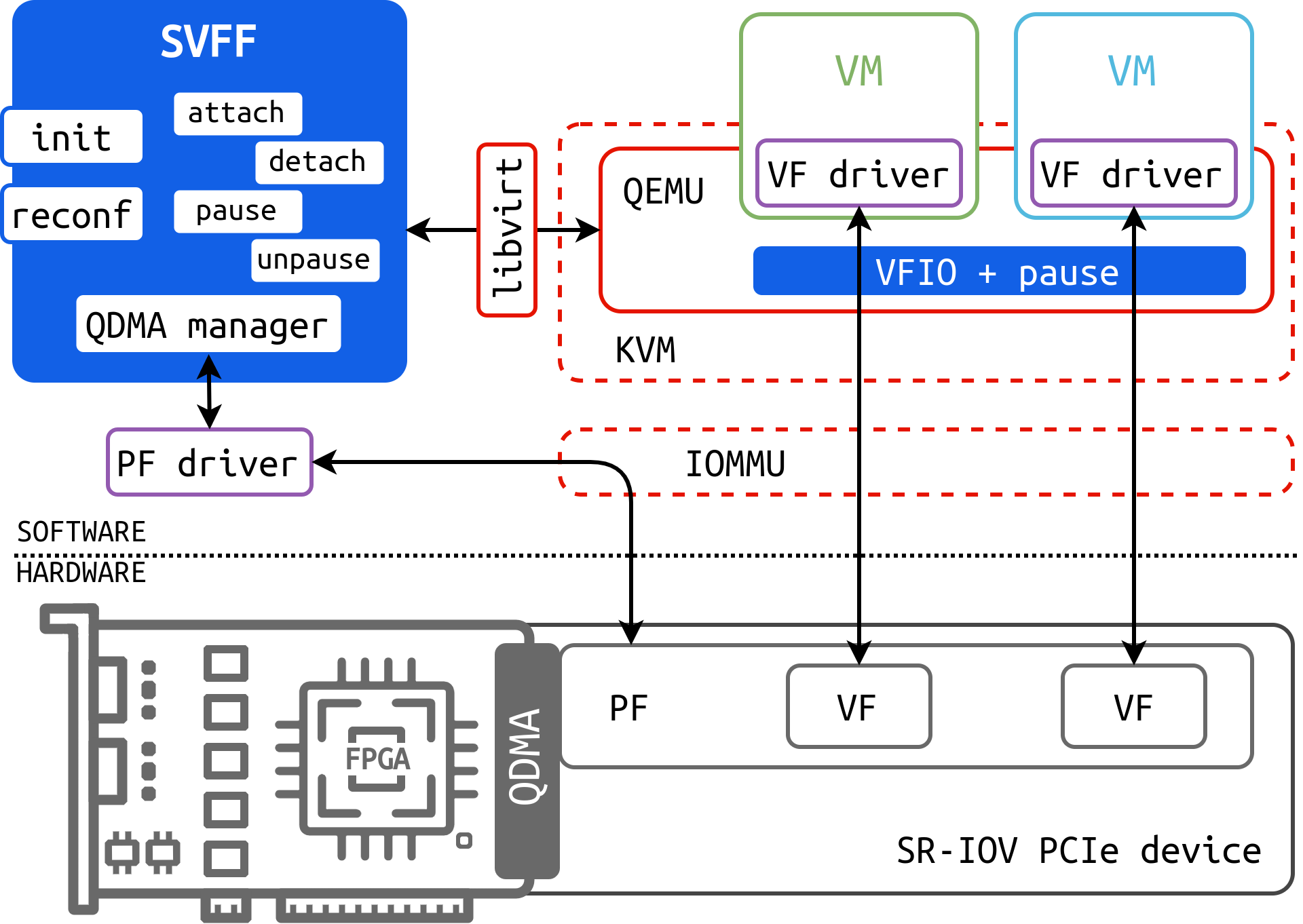

The diagram illustrates a layered system architecture integrating software virtualization components (SVFF, QEMU, VMs) with hardware elements (FPGA, QDMA, PCIe devices). It depicts workflows for managing virtual functions (VFs) and physical functions (PFs) across software-hardware boundaries.

### Components/Axes

1. **Software Layer (Top Section)**:

- **SVFF (Blue Box)**: Contains commands: `init`, `attach`, `detach`, `reconf`, `pause`, `unpause`, `QDMA manager`.

- **libvirt**: Connects SVFF to QEMU/KVM.

- **QEMU**: Linked to two VMs (green and blue boxes) with VF drivers.

- **VF Drivers**: Two instances labeled "VF driver" (purple boxes) connected to "VFIO + pause".

2. **Hardware Layer (Bottom Section)**:

- **FPGA**: Central hardware component with "QDMA" labeling.

- **PF/VF**: Physical Function (PF) and Virtual Function (VF) blocks connected to SR-IOV PCIe device.

- **IOVMU**: Positioned between QEMU and hardware layer.

3. **Color Coding**:

- Blue: SVFF

- Red: QEMU/VMs

- Purple: PF driver

- Gray: Hardware components

### Detailed Analysis

- **Software Flow**:

- SVFF initiates operations (`init`, `attach`, etc.) managed by `QDMA manager`.

- `libvirt` acts as an intermediary between SVFF and QEMU.

- QEMU manages two VMs, each with a VF driver. One VM includes "VFIO + pause" functionality.

- **Hardware Flow**:

- PF driver (purple) connects to FPGA's QDMA.

- PF (hardware) links to two VFs, which interface with the SR-IOV PCIe device.

### Key Observations

1. **Layered Architecture**: Clear separation between software (virtualization stack) and hardware (FPGA/PCIe).

2. **VF Management**: VF drivers in VMs interact with hardware VFs via VFIO, suggesting passthrough or emulation.

3. **Pause/Unpause Mechanism**: Explicitly shown in both software (SVFF) and hardware (VFIO + pause) layers.

4. **QDMA Integration**: QDMA manager in SVFF connects to FPGA's QDMA, implying high-speed data movement.

### Interpretation

This architecture enables efficient virtualization of hardware resources (e.g., FPGA, PCIe devices) for VMs. The SVFF orchestrates operations, while libvirt and QEMU abstract hardware details. The PF/VF hierarchy allows direct hardware access for VMs via SR-IOV, with the FPGA likely accelerating data transfers (QDMA). The pause/unpause functionality suggests dynamic resource management. The diagram emphasizes integration between virtualization software (KVM/QEMU) and specialized hardware (FPGA) for optimized performance.