## Diagram: Layered Architecture

### Overview

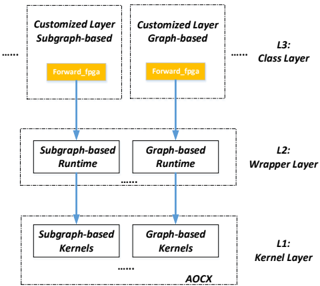

The image depicts a layered architecture diagram, showing the flow of data and processes through three distinct layers: Kernel Layer (L1), Wrapper Layer (L2), and Class Layer (L3). Each layer contains "Subgraph-based" and "Graph-based" components. The diagram illustrates how customized layers are built upon lower-level kernels and runtime environments.

### Components/Axes

* **Layers:**

* L1: Kernel Layer

* L2: Wrapper Layer

* L3: Class Layer

* **Components within each layer:**

* Subgraph-based

* Graph-based

* **Additional Elements:**

* "Forward_fpga" (appears in Class Layer)

* "AOCX" (appears in Kernel Layer)

* **Arrows:** Blue arrows indicate the flow of data/processes from the Class Layer to the Wrapper Layer and then to the Kernel Layer.

### Detailed Analysis

* **L1: Kernel Layer:**

* Contains "Subgraph-based Kernels" and "Graph-based Kernels."

* Labeled as "AOCX" at the bottom.

* **L2: Wrapper Layer:**

* Contains "Subgraph-based Runtime" and "Graph-based Runtime."

* **L3: Class Layer:**

* Contains "Customized Layer Subgraph-based" and "Customized Layer Graph-based."

* Each of these components has a yellow box labeled "Forward_fpga."

* **Flow:**

* The flow is top-down, from L3 to L1, indicated by blue arrows.

### Key Observations

* The architecture is structured in a layered fashion, with each layer building upon the previous one.

* Both "Subgraph-based" and "Graph-based" components are present in each layer, suggesting parallel processing or different approaches to the same task.

* The "Forward_fpga" component in the Class Layer likely represents a forward pass operation on an FPGA.

* "AOCX" at the Kernel Layer might indicate a specific hardware or software platform.

### Interpretation

The diagram illustrates a hierarchical system where high-level customized layers (L3) rely on lower-level runtime environments (L2) and fundamental kernels (L1). The presence of both "Subgraph-based" and "Graph-based" components suggests a hybrid approach to processing, possibly leveraging the strengths of both methods. The "Forward_fpga" component indicates hardware acceleration using FPGAs. The "AOCX" label at the Kernel Layer likely refers to a specific hardware or software platform upon which the entire architecture is built. The diagram suggests a modular and flexible design, allowing for customization and optimization at different levels of the system.