## Pie Chart: Average time distribution for each part of our BoT

### Overview

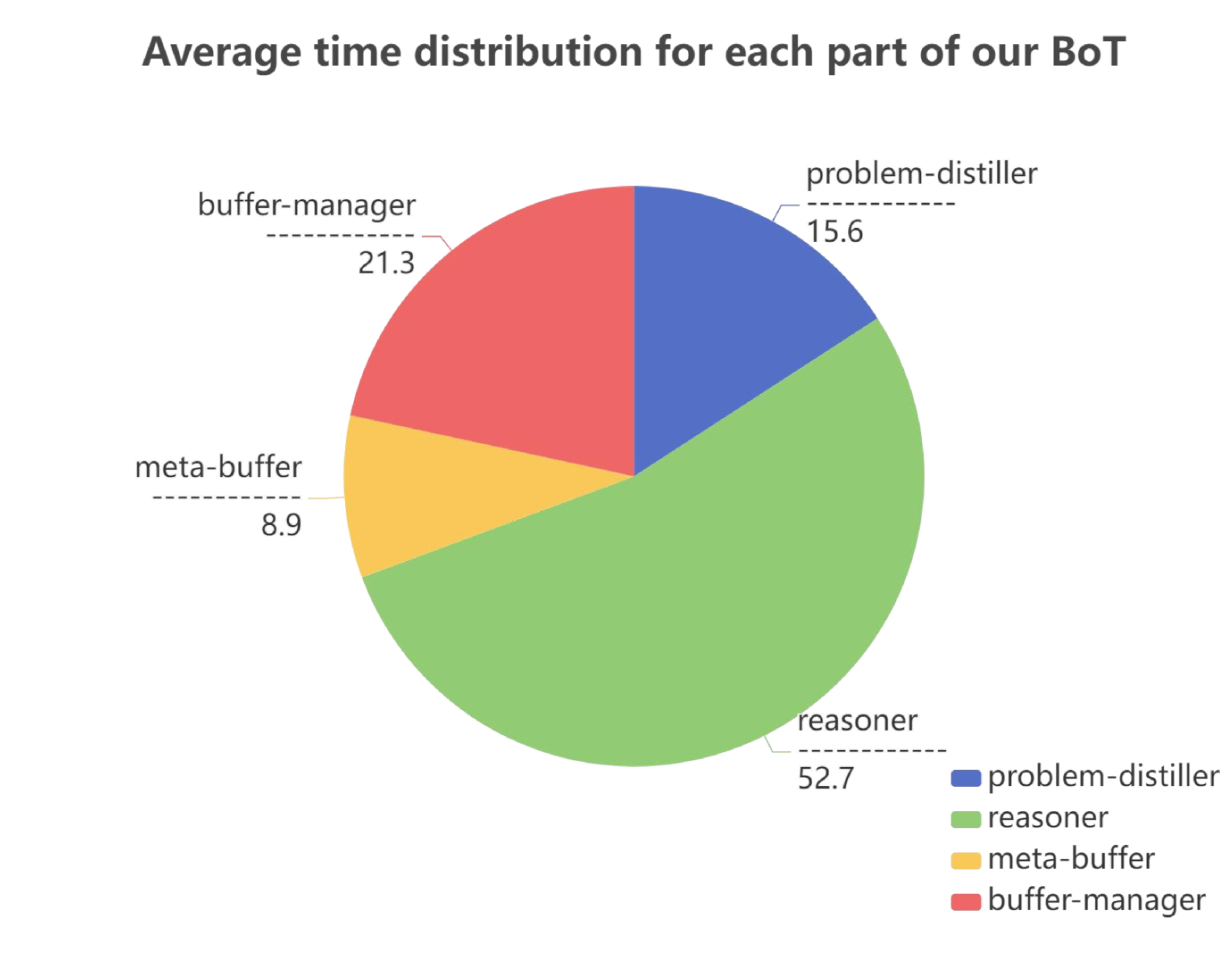

The image displays a pie chart titled "Average time distribution for each part of our BoT," illustrating the proportional time allocation across four components of a system: problem-distiller, reasoner, meta-buffer, and buffer-manager. The chart uses distinct colors for each component, with numerical percentages labeled directly on the segments.

### Components/Axes

- **Legend**: Located on the right side of the chart, mapping colors to components:

- Blue: problem-distiller

- Green: reasoner

- Yellow: meta-buffer

- Red: buffer-manager

- **Segments**: Four labeled sections with percentages:

- problem-distiller (blue): 15.6%

- reasoner (green): 52.7%

- meta-buffer (yellow): 8.9%

- buffer-manager (red): 21.3%

### Detailed Analysis

- **problem-distiller** (blue): Occupies 15.6% of the chart, positioned between the reasoner and buffer-manager segments.

- **reasoner** (green): Dominates the chart at 52.7%, forming the largest segment.

- **meta-buffer** (yellow): Smallest segment at 8.9%, located between the buffer-manager and problem-distiller.

- **buffer-manager** (red): Second-largest segment at 21.3%, adjacent to the problem-distiller.

### Key Observations

1. The **reasoner** consumes over half of the total time (52.7%), indicating it is the most time-intensive component.

2. The **buffer-manager** (21.3%) and **problem-distiller** (15.6%) together account for ~37% of the time, significantly less than the reasoner.

3. The **meta-buffer** (8.9%) is the least time-consuming component, occupying less than 10% of the distribution.

### Interpretation

The data suggests a system architecture where the **reasoner** is the primary computational bottleneck, requiring optimization for efficiency. The **buffer-manager** and **problem-distiller** play secondary roles, while the **meta-buffer** has minimal time allocation. This distribution could reflect a design prioritizing reasoning capabilities over other components, potentially at the cost of scalability or latency in other subsystems. The stark disparity between the reasoner and other components highlights a possible trade-off in system design, where increased reasoning capacity may come with reduced flexibility or responsiveness in auxiliary processes.