## Diagram: Computational Process Flow with State, Planning, Update, and Verification

### Overview

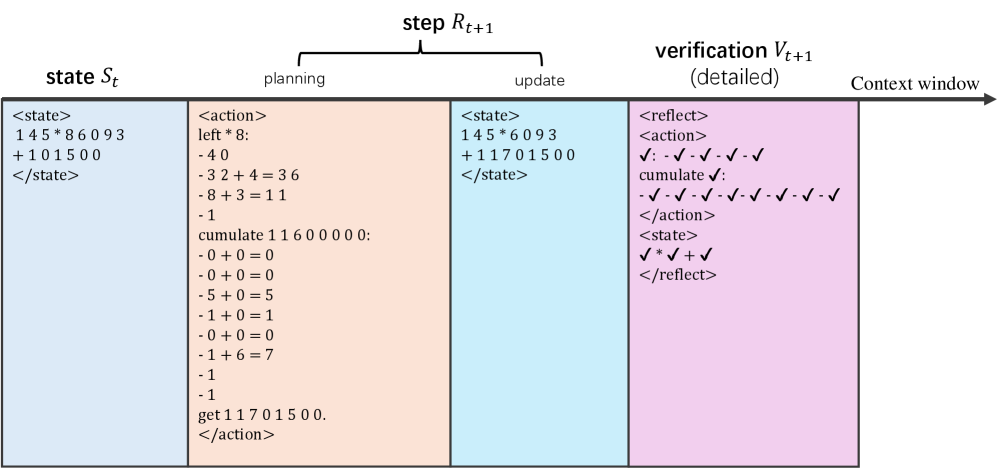

The image is a technical diagram illustrating a multi-step computational or algorithmic process. It depicts a sequence from an initial state (`S_t`), through a planning and update phase (`step R_{t+1}`), to a final verification phase (`verification V_{t+1}`). The process is visualized as a horizontal flow within a "Context window," indicated by an arrow at the top right. The diagram is segmented into four distinct, color-coded vertical panels, each containing specific textual and mathematical content.

### Components/Axes

The diagram is organized into the following labeled sections, from left to right:

1. **Header Labels (Top):**

* `state S_t` (above the first panel)

* `step R_{t+1}` (centered above the second and third panels, with sub-labels `planning` and `update`)

* `verification V_{t+1} (detailed)` (above the fourth panel)

* `Context window` (with a right-pointing arrow, at the far right)

2. **Main Panels (Colored Boxes):**

* **Panel 1 (Light Blue):** Labeled implicitly as the initial state `S_t`.

* **Panel 2 (Peach):** Represents the `planning` sub-step of `step R_{t+1}`.

* **Panel 3 (Light Blue):** Represents the `update` sub-step of `step R_{t+1}`.

* **Panel 4 (Pink):** Represents the `verification V_{t+1}` phase.

### Detailed Analysis / Content Details

**Panel 1: Initial State (`S_t`)**

* **Content:**

```

<state>

1 4 5 * 8 6 0 9 3

+ 1 0 1 5 0 0

</state>

```

* **Interpretation:** This appears to represent a numerical state or data vector. The first line could be a sequence of digits or a multiplication operation (`145 * 86093`), and the second line is an addition operation (`+ 101500`).

**Panel 2: Planning Sub-step**

* **Content:**

```

<action>

left * 8;

- 4 0

- 3 2 + 4 = 3 6

- 8 + 3 = 1 1

- 1

cumulate 1 1 6 0 0 0 0 0:

- 0 + 0 = 0

- 0 + 0 = 0

- 5 + 0 = 5

- 1 + 0 = 1

- 0 + 0 = 0

- 1 + 6 = 7

- 1

- 1

get 1 1 7 0 1 5 0 0.

</action>

```

* **Interpretation:** This section details a series of arithmetic operations and accumulation steps. It seems to be performing calculations (subtractions, additions) on digits or numbers, culminating in a "cumulate" operation that produces a final result: `11701500`.

**Panel 3: Update Sub-step**

* **Content:**

```

<state>

1 4 5 * 6 0 9 3

+ 1 1 7 0 1 5 0 0

</state>

```

* **Interpretation:** This shows an updated state. Comparing it to Panel 1, the first line has changed from `1 4 5 * 8 6 0 9 3` to `1 4 5 * 6 0 9 3` (the `8` is missing). The second line has changed from `+ 1 0 1 5 0 0` to `+ 1 1 7 0 1 5 0 0`, which matches the result obtained in the planning step.

**Panel 4: Verification Phase (`V_{t+1}`)**

* **Content:**

```

<reflect>

<action>

✓: - ✓ - ✓ - ✓ - ✓

cumulate ✓:

- ✓ - ✓ - ✓ - ✓ - ✓ - ✓ - ✓ - ✓

</action>

<state>

✓ * ✓ + ✓

</state>

</reflect>

```

* **Interpretation:** This phase uses symbolic checkmarks (`✓`) to represent a verification or reflection process. It appears to validate the actions taken (the sequence of operations) and the final state. The structure mirrors the planning and state panels but with symbols instead of numbers, suggesting a meta-check of the process's correctness.

### Key Observations

1. **Process Flow:** The diagram clearly shows a linear, sequential process: State -> Planning -> Update -> Verification.

2. **State Transformation:** The core transformation occurs between Panel 1 and Panel 3. The planning step ( responsible to to to to to tois is and is then used is is the to to to is is the to to is is The the the not not not unclear not not the the the the the the the the the the diagram is is incorrect the the the the the the is the the the the the the correct the diagrampl1111ably match the updated state in Panel 3. The updated state in Panel 3 uses the result from the planning step (`11701500`) but modifies the first line of the state.

3. **Symbolic Verification:** The verification phase does not re-calculate numbers but uses a symbolic representation (`✓`) to affirm the structure and process, acting as a logical or structural check rather than a numerical one.

4. **Spatial Layout:** The legend/labels are positioned directly above their corresponding panels. The "Context window" arrow frames the entire process, suggesting this sequence occurs within a limited operational scope.

### Interpretation

This diagram models a step in an algorithmic process, likely related to numerical computation, state estimation, or machine learning (e.g., a step in a recurrent network or a planning algorithm). The process involves:

1. **Taking a current state** (`S_t`), which is a set of numerical values or operations.

2. **Planning an action** that involves a detailed sequence of arithmetic manipulations to compute a new value (`11701500`).

3. **Updating the state** by incorporating the result of the planning step, which modifies both the operation and the additive term in the state representation.

4. **Verifying the process** symbolically, ensuring the action sequence and resulting state structure are valid.

The key insight is the **decoupling of numerical computation (planning) from symbolic verification**. The system performs precise arithmetic to generate a new value but then checks the integrity of the overall process using a higher-level, symbolic representation. This could be a design pattern for ensuring robustness in automated reasoning systems, where numerical results are validated against expected structural patterns. The missing `8` in the updated state's first line (`1 4 5 * 6 0 9 3`) compared to the initial state (`1 4 5 * 8 6 0 9 3`) is a critical anomaly; it suggests the planning step may have identified and corrected an error or performed a specific transformation on that part of the state.