\n

## Diagram: Gibbs Sampling Approaches

### Overview

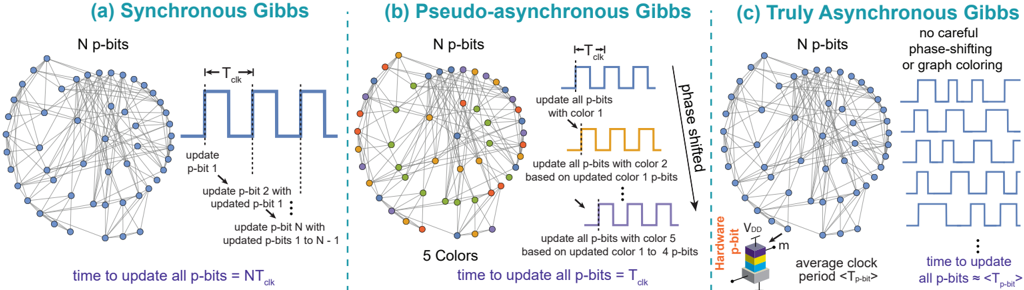

The image presents a comparative diagram illustrating three different approaches to Gibbs sampling: Synchronous, Pseudo-asynchronous, and Truly Asynchronous. Each approach is visualized with a network of nodes ("N p-bits") and a corresponding timing diagram showing how the nodes are updated. The diagram aims to demonstrate the differences in update mechanisms and timing characteristics of each method.

### Components/Axes

Each of the three sections (a, b, c) shares the following components:

* **Network of Nodes:** A circular arrangement of nodes representing "N p-bits". Nodes are colored differently to indicate their state or update order.

* **Timing Diagram:** A series of rectangular pulses representing the timing of updates to the nodes.

* **Textual Labels:** Descriptions of the update process and timing parameters.

Specific to each section:

* **(a) Synchronous Gibbs:** Label "N p-bits", "T<sub>clk</sub>", "update p-bit 1", "update p-bit 2 with updated p-bit 1", "update p-bit N with updated p-bits 1 to N-1", "time to update all p-bits = NT<sub>clk</sub>".

* **(b) Pseudo-asynchronous Gibbs:** Label "N p-bits", "T<sub>clk</sub>", "5 Colors", "update all p-bits with color 1", "update all p-bits with color 2 based on updated color 1 p-bits", "update all p-bits with color 5 based on updated color 1 to 4 p-bits", "time to update all p-bits = T<sub>clk</sub>", "phase shifted". Also includes a vertical bar labeled "Hardware doable".

* **(c) Truly Asynchronous Gibbs:** Label "N p-bits", "no careful phase-shifting or graph coloring", "average clock period <T<sub>clk</sub>>", "time to update all p-bits = <T<sub>p-bit</sub>>".

### Detailed Analysis or Content Details

**(a) Synchronous Gibbs:**

* The network consists of approximately 50 nodes arranged in a circle.

* The timing diagram shows a single clock pulse (T<sub>clk</sub>) followed by a sequence of updates.

* The updates are sequential: p-bit 1 is updated first, then p-bit 2 using the updated value of p-bit 1, and so on, until p-bit N is updated.

* The total time to update all p-bits is stated as NT<sub>clk</sub>, where N is the number of p-bits.

**(b) Pseudo-asynchronous Gibbs:**

* The network has approximately 50 nodes, colored with 5 distinct colors (yellow, green, orange, red, and blue).

* The timing diagram shows a series of pulses, each corresponding to an update with a specific color.

* The updates are performed in color order: all p-bits are updated with color 1, then with color 2 based on the updated color 1 p-bits, and so on, up to color 5.

* The diagram indicates a "phase shifted" aspect to the updates.

* The total time to update all p-bits is stated as T<sub>clk</sub>.

* A vertical bar labeled "Hardware doable" is present.

**(c) Truly Asynchronous Gibbs:**

* The network has approximately 50 nodes, colored with a mix of blue and teal.

* The timing diagram shows a series of irregular pulses, indicating asynchronous updates.

* There is "no careful phase-shifting or graph coloring" involved.

* The average clock period is stated as less than T<sub>clk</sub>.

* The time to update all p-bits is stated as <T<sub>p-bit</sub>>, representing the average time per p-bit.

### Key Observations

* Synchronous Gibbs has a deterministic, sequential update order and a total update time proportional to the number of p-bits (NT<sub>clk</sub>).

* Pseudo-asynchronous Gibbs introduces color-based updates and a phase shift, with a total update time of T<sub>clk</sub>.

* Truly Asynchronous Gibbs has a completely irregular update order and an average update time per p-bit (<T<sub>p-bit</sub>>).

* The diagram highlights the increasing complexity and asynchronicity of the Gibbs sampling approaches from (a) to (c).

### Interpretation

The diagram illustrates the trade-offs between different Gibbs sampling approaches. Synchronous Gibbs is simple to implement but can be slow for large N. Pseudo-asynchronous Gibbs attempts to improve performance by introducing parallelism through color-based updates, but still relies on a global clock. Truly Asynchronous Gibbs offers the highest potential for parallelism and speed but is more complex to implement and may require careful consideration of synchronization issues. The "Hardware doable" label in the Pseudo-asynchronous section suggests a practical implementation constraint. The diagram suggests that the choice of Gibbs sampling approach depends on the specific application and the available hardware resources. The use of color in the Pseudo-asynchronous approach likely represents different states or variables being updated, and the phase shift indicates a deliberate offset in the update timing. The irregular timing in the Truly Asynchronous approach reflects the inherent randomness of the process.