## Comparative Diagram: Synchronous, Pseudo-asynchronous, and Truly Asynchronous Gibbs Sampling Methods

### Overview

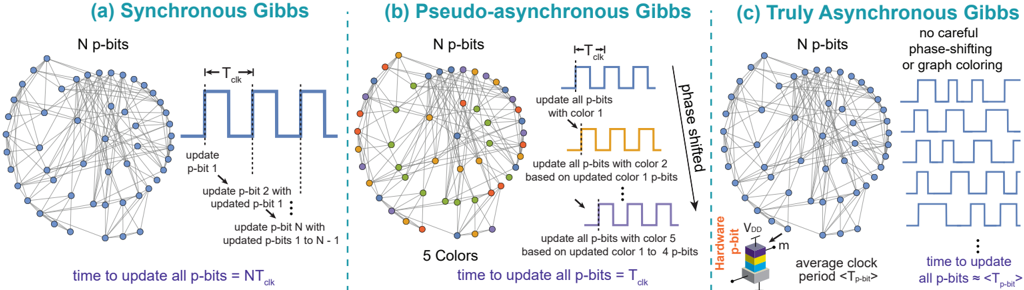

The image is a technical diagram comparing three different methods for updating a network of probabilistic bits (p-bits) using Gibbs sampling. It is divided into three vertical panels labeled (a), (b), and (c), each illustrating a distinct synchronization strategy. The diagram uses network graphs, timing diagrams, and annotations to explain the update process and its efficiency.

### Components/Axes

The diagram is structured into three main panels:

* **Panel (a):** Titled "(a) Synchronous Gibbs". Contains a network graph and a timing diagram.

* **Panel (b):** Titled "(b) Pseudo-asynchronous Gibbs". Contains a colored network graph and a multi-phase timing diagram.

* **Panel (c):** Titled "(c) Truly Asynchronous Gibbs". Contains a network graph, an asynchronous timing diagram, and a hardware component illustration.

**Common Elements:**

* **Network Graphs:** Each panel shows a circular network of nodes labeled "N p-bits". Nodes are connected by lines representing interactions.

* **Timing Diagrams:** Each panel includes a diagram showing clock signals (square waves) over time, with annotations explaining the update sequence.

* **Key Text Annotations:** Each panel concludes with a statement about the total "time to update all p-bits".

### Detailed Analysis

#### Panel (a): Synchronous Gibbs

* **Network Graph:** All `N` p-bit nodes are colored blue. The network is densely connected.

* **Timing Diagram & Process:**

* A single, periodic clock signal with period `T_clk` is shown.

* The update process is sequential: "update p-bit 1", then "update p-bit 2 with updated p-bit 1", continuing until "update p-bit N with updated p-bits 1 to N-1".

* This indicates a strict, sequential update order where each p-bit update depends on the most recent state of all previous p-bits in the sequence.

* **Performance Metric:** The text at the bottom states: "time to update all p-bits = N T_clk". This is the slowest method, scaling linearly with the number of p-bits.

#### Panel (b): Pseudo-asynchronous Gibbs

* **Network Graph:** The `N` p-bit nodes are divided into 5 distinct color groups (blue, orange, green, red, purple). A label "5 Colors" is placed below the graph.

* **Timing Diagram & Process:**

* The diagram shows five distinct clock signals, each phase-shifted relative to the others.

* The update is parallel within color groups but sequential across groups: "update all p-bits with color 1", then "update all p-bits with color 2 based on updated color 1 p-bits", and so on through color 5.

* This method uses graph coloring to identify independent sets of p-bits that can be updated in parallel without conflict.

* **Performance Metric:** The text states: "time to update all p-bits = T_clk". This is a significant improvement over the synchronous method, as the update time is now independent of `N` (for a fixed number of colors).

#### Panel (c): Truly Asynchronous Gibbs

* **Network Graph:** All `N` p-bit nodes are blue again, similar to panel (a).

* **Timing Diagram & Process:**

* The diagram shows multiple, independent clock signals with varying phases and potentially different frequencies. There is no global synchronization.

* The annotation states: "no careful phase-shifting or graph coloring". Each p-bit updates based on its own local clock.

* A hardware component labeled "Hardware p-bit" is illustrated, showing a device with terminals `V_dd` and `m`, representing a physical implementation of a p-bit.

* **Performance Metric:** The text states: "time to update all p-bits < T_p-bit". The symbol `<` indicates the total update time is less than the average clock period of a single p-bit (`<T_p-bit>`), implying the updates happen concurrently and the system throughput is very high.

### Key Observations

1. **Evolution of Parallelism:** The diagram clearly shows a progression from fully sequential (a), to structured parallelism via graph coloring (b), to fully unstructured, hardware-level parallelism (c).

2. **Time Complexity:** The stated update times show a dramatic reduction: from `O(N)` in (a), to `O(1)` (constant time) in (b), to effectively `O(1)` with a much smaller constant in (c).

3. **Hardware Integration:** Panel (c) introduces a physical "Hardware p-bit" component, suggesting that the "Truly Asynchronous" method is closely tied to a specific hardware implementation where p-bits operate independently.

4. **Color Coding Purpose:** The use of 5 colors in panel (b) is a visual representation of the graph coloring algorithm used to partition the network into independent sets for parallel updates.

### Interpretation

This diagram serves as a conceptual and technical comparison of synchronization strategies for probabilistic computing systems, likely in the context of Ising machines or Boltzmann machines implemented with p-bits.

* **What it demonstrates:** It illustrates the trade-off between synchronization overhead and computational throughput. Synchronous systems (a) are simple to design but slow. Pseudo-asynchronous systems (b) introduce coordination (graph coloring) to achieve parallelism, balancing complexity and speed. Truly asynchronous systems (c) remove global coordination entirely, relying on hardware where updates are inherently concurrent, offering the highest potential performance.

* **Relationship between elements:** The network graphs show the *problem structure* (interconnected p-bits), while the timing diagrams show the *solution strategy* (how to schedule updates). The hardware illustration in (c) grounds the abstract concept in a potential physical realization.

* **Underlying Message:** The progression argues for the advantages of asynchronous, hardware-native designs for sampling from complex probability distributions. It suggests that moving away from global clocking and careful scheduling (as in (a) and (b)) towards truly asynchronous operation (c) is key to achieving high-speed probabilistic computation. The final panel implies that the "Truly Asynchronous Gibbs" method is not just a theoretical model but is implementable in hardware.