## Bar Chart: Performance Comparison of Instruction Sets on IvyBridge-EP and KNC Architectures

### Overview

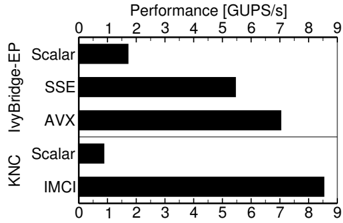

The image is a horizontal bar chart comparing the performance, measured in Giga Updates Per Second (GUPS/s), of different computational instruction sets on two distinct processor architectures: Intel IvyBridge-EP and Intel Xeon Phi Knights Corner (KNC). The chart demonstrates the performance scaling achieved by moving from scalar code to vectorized instruction sets.

### Components/Axes

* **Chart Type:** Horizontal bar chart.

* **X-Axis (Bottom):** Labeled "Performance [GUPS/s]". It has a linear scale with major tick marks at every integer from 0 to 9.

* **Y-Axis (Left):** Lists the processor architectures and their respective instruction sets. The architectures are grouped with a label and a horizontal dividing line.

* **Top Group:** Labeled "IvyBridge-EP". Contains three bars for: "Scalar", "SSE", and "AVX".

* **Bottom Group:** Labeled "KNC". Contains two bars for: "Scalar" and "IMCI".

* **Legend:** There is no separate legend box. The instruction set labels are placed directly to the left of their corresponding bars on the y-axis.

* **Bar Color:** All bars are solid black.

### Detailed Analysis

**IvyBridge-EP Architecture (Top Section):**

1. **Scalar:** The bar extends from 0 to approximately **1.8 GUPS/s**. This is the baseline performance.

2. **SSE (Streaming SIMD Extensions):** The bar extends from 0 to approximately **5.5 GUPS/s**. This represents a significant performance increase over the scalar version.

3. **AVX (Advanced Vector Extensions):** The bar extends from 0 to approximately **7.2 GUPS/s**. This is the highest performance within the IvyBridge-EP group.

**KNC Architecture (Bottom Section):**

1. **Scalar:** The bar extends from 0 to approximately **1.0 GUPS/s**. This is the lowest performance value on the entire chart.

2. **IMCI (Intel Many Core Instruction Set):** The bar extends from 0 to approximately **8.5 GUPS/s**. This is the highest performance value shown in the chart.

### Key Observations

* **Performance Hierarchy:** For both architectures, the vectorized instruction sets (SSE/AVX for IvyBridge-EP, IMCI for KNC) dramatically outperform their respective scalar implementations.

* **Architecture Comparison:** The KNC's specialized IMCI instruction set achieves the highest absolute performance (~8.5 GUPS/s), surpassing the best performance from the general-purpose IvyBridge-EP (~7.2 GUPS/s for AVX).

* **Scalar Performance:** The scalar performance on KNC (~1.0 GUPS/s) is notably lower than the scalar performance on IvyBridge-EP (~1.8 GUPS/s).

* **Scaling Factor:** The performance scaling from Scalar to the best vector set is more pronounced on KNC (an increase of ~7.5x) compared to IvyBridge-EP (an increase of ~4x from Scalar to AVX).

### Interpretation

This chart visually argues for the critical importance of utilizing vectorized instruction sets to achieve high performance on modern processor architectures. The data suggests that:

1. **Vectorization is Essential:** Writing code to leverage SIMD (Single Instruction, Multiple Data) extensions is not optional for high-throughput computing; it provides a multi-fold performance increase.

2. **Architecture-Specific Optimization Yields Best Results:** The KNC's IMCI, designed specifically for its many-core architecture, delivers superior peak performance compared to the more general AVX instructions on a standard CPU core. This highlights the performance advantage of specialized hardware and instruction sets.

3. **The Cost of Generality:** The lower scalar performance on KNC may indicate that its individual cores are less optimized for traditional scalar code, reinforcing that its strength lies in massively parallel, vectorized workloads.

4. **Practical Implication:** For developers working on high-performance computing (HPC) or numerical simulation tasks (where GUPS is a relevant metric), the chart provides clear evidence that targeting AVX on CPUs or IMCI on Xeon Phi coprocessors is necessary to unlock the hardware's potential. The significant gap between scalar and vector performance underscores the performance penalty of failing to optimize code for vectorization.