## Memristors - from In-memory computing, Deep Learning Acceleration, Spiking Neural Networks, to the Future of Neuromorphic and Bio-inspired Computing

Adnan Mehonic * , Abu Sebastian, Bipin Rajendran, Osvaldo Simeone, Eleni Vasilaki, Anthony J. Kenyon

Dr. Adnan Mehonic, Prof Anthony J. Kenyon

Department of Electronic & Electrical Engineering, UCL, Torrington Place, London WC1E 7JE, United Kingdom

E-mail: adnan.mehonic.09@ucl.ac.uk

Dr. Abu Sebastian

IBM Research - Zurich, 8803 Rüschlikon, Switzerland

Dr. Bipin Rajendran, Prof Osvaldo Simeone

Centre for Telecommunications Research, Department of Engineering, King's College London, WC2R 2LS, United Kingdom

Prof. Eleni Vasilaki

Department of Computer Science, University of Sheffield, Sheffield, South Yorkshire, United Kingdom

Keywords: memristor, neuromorphic, AI, deep learning, spiking neural networks, in-memory computing

## Abstract

Machine learning, particularly in the form of deep learning, has driven most of the recent fundamental developments in artificial intelligence. Deep learning is based on computational models that are, to a certain extent, bio-inspired, as they rely on networks of connected simple computing units operating in parallel. Deep learning has been successfully applied in areas such as object/pattern recognition, speech and natural language processing, self-driving vehicles, intelligent self-diagnostics tools, autonomous robots, knowledgeable personal assistants, and monitoring. These successes have been mostly supported by three factors: availability of vast amounts of data, continuous growth in computing power, and algorithmic innovations. The approaching demise of Moore's law, and the consequent expected modest improvements in computing power that can be achieved by scaling, raise the question of whether the described progress will be slowed or halted due to hardware limitations. This paper reviews the case for a novel beyond-CMOS hardware technology - memristors - as a potential solution for the implementation of power-efficient in-memory computing, deep learning accelerators, and spiking neural networks. Central themes are the reliance on nonvon-Neumann computing architectures and the need for developing tailored learning and inference algorithms. To argue that lessons from biology can be useful in providing directions for further progress in artificial intelligence, we briefly discuss an example based reservoir computing. We conclude the review by speculating on the 'big picture' view of future neuromorphic and brain-inspired computing systems.

## 1. Introduction

The three factors are currently driving the main developments in artificial intelligence (AI): availability of vast amounts of data, continuous growth in computing power, and algorithmic innovations. Graphics processing units (GPUs) have been demonstrated as effective coprocessors for the implementation of machine learning (ML) algorithms based on deep learning (DL). Solutions based on deep learning and GPU implementations have led to massive improvements in many AI tasks, but have also caused an exponential increase in demand for computing power. Recent analyses show that the demand for computing power has increased by a factor of 300,000 since 2012, and the estimate is that this demand will double every 3.4 months - at a much faster rate than improvements made historically through Moore's scaling (a 7-fold improvement over the same period of time) [1] . At the same time, Moore's law has been slowing down significantly for the last few years [2] , as there are strong indications that we will not be able to continue scaling down CMOS transistors. This calls for the exploration of alternative technology roadmaps for the development of scalable and efficient AI solutions.

Transistor scaling is not the only way to improve computing performance. Architectural innovations such as GPUs, field-programmable arrays (FPGAs), and application-specific integrated circuits (ASICs), have all significantly advanced the ML field 3 . A common aspect of modern computing architectures for ML is a move away from the classical von Neumann architecture that physically separates memory and computing. This approach yields a performance bottleneck that is often the main reason for both energy and speed inefficiency of ML implementations on conventional hardware platforms due to costly data movements. However, architectural developments alone are not likely to be sufficient. In fact, standard digital CMOS components are inherently not well suited for the implementation of a massive number of continuous weights/synapses in artificial neural networks (ANNs).

1.1. The promise of memristors. There is a strong case to be made for the exploration of alternative technologies. Although the memristor technology is currently still in development, it is a strong candidate for future non-CMOS and beyond von-Neumann computing solutions [4] . Since its early development in 2008 [5] , or even earlier under different names [6] , memristor technology expanded remarkably to include many different materials solutions, physical mechanisms, and novel computing approaches [4] . A single progress report cannot cover all different approaches and fast-growing developments in the field. The evaluation of state of the art in memristor-based electronics can be found elsewhere [7] . Instead, in this paper, we present and discuss a few representative case studies, showcasing the potential role of memristors in the expanding field of AI hardware. We present examples of how memristors are used for in-memory computing systems, deep learning accelerators, and spike-based computing. Finally, we discuss and speculate on the future of neuromorphic and bio-inspired computing paradigms and provide reservoir computing as an example.

For the last 15 years, memristors have been a focal point for many different research communities - mathematicians, solid-state physicists, experimental material scientists, electrical engineers and, more recently, computer scientists and computational neuroscientists. The concept of memristor was introduced almost 50 years ago, back in 1971 [8] , was nearly forgotten for almost four decades. It is now experiencing a rebirth with a vibrant and very active research community. There are many different flavours of memristive technologies. Still, in their most popular implementation, memristors are simple two-terminal devices with the extraordinary property that their resistance depends on their history of electrical stimuli. In other words, memristors are resistors with memory. They promise high levels of integration, stable non-volatile resistance states, fast resistance switching, excellent energy efficiency - all very desirable properties for next generation of memory technologies.

The physical implementations of memristors are broad and arguably include many different technologies such as redox-based resistive random-access memory (ReRAM), phase change memories (PCM), magnetoresistive random-access memory (MRAM). Further differentiations within larger classes can be made, depending on physical mechanisms that govern the resistance change. Many excellent reviews cover the principles and switching mechanisms of memristor devices. Here, we will briefly mention two extensively studied types of memristive devices, namely redox-based random access memory (ReRAM) and phase-change memory (PCM).

Resistance switching is one of the most explored properties of memristive devices. A thin insulating film reversibly changes its electrical resistance - between an insulating state and a conducting state - under the application of an external electrical stimulus. For binary memory devices, two stable states are sought, typically called the high resistance state (HRS), and the low resistance state (LRS). The transition from the HRS to the LRS is called a SET process, while a RESET process describes the transition from the LRS to the HRS.

Basic memory cells of both types, in their most straightforward implementation, have three layers - two conductive electrodes and a thin switching layer sandwiched in-between. Local redox processes govern resistance switching in ReRAM devices. A broad classification can be made based on a distinction between the switching that happens as a result of intrinsic properties of the switching material (typically oxides), and switching that is the result of indiffusion of metal ions (typically from one of the metallic electrodes). The former type is called intrinsic switching, and the latter is called extrinsic switching [9] . Alternatively, a classification can be made depending on the main driving force for the redox process (thermal or electrical), or the type of ions that move. The main three classes are electrochemical metallization cells (or conductive bridge) ReRAMs (ECM), valence change ReRAMs (VCM) and thermochemical ReRAMs (TCM) [4] .

Many ReRAM devices require an electroforming step prior to resistance switching. This can be considered a soft breakdown of the insulating material. A conductive filament is produced inside the insulating film as a result of the applied electrical bias. Modification of conductive filaments, led by a local redox process, leads to the change of resistance. The diameter of the conductive filament is typically of the order of a few nanometers to a few tens of nanometers, and it does not depend on the size of the electrodes. Another, less common type is interfacetype switching, which does not depend on creation and modification of conductive filaments, but can be driven by the formation of a tunnel or Schottky barrier across the whole interface between electrode and switching layer.

In the case of PCMs, the change of resistance due to the crystallisation and amorphisation processes of phase change materials. Amplitude and duration of applied voltage pulses control the phase transitions - the SET process changes the amorphous to a crystalline phase (HRS to LRS transition), and the RESET process changes the crystalline to an amorphous phase (LRS to HRS transition).

For many computing tasks, more than two states are required, and for most memristive devices, including ReRAMs and PCMs, many resistance states can be achieved. However, benchmarking of memristive devices for different applications, beyond pure digital memory, can be challenging and relies on many different parameters other than the number of different resistance states. We will discuss the main device properties in the context of different applications.

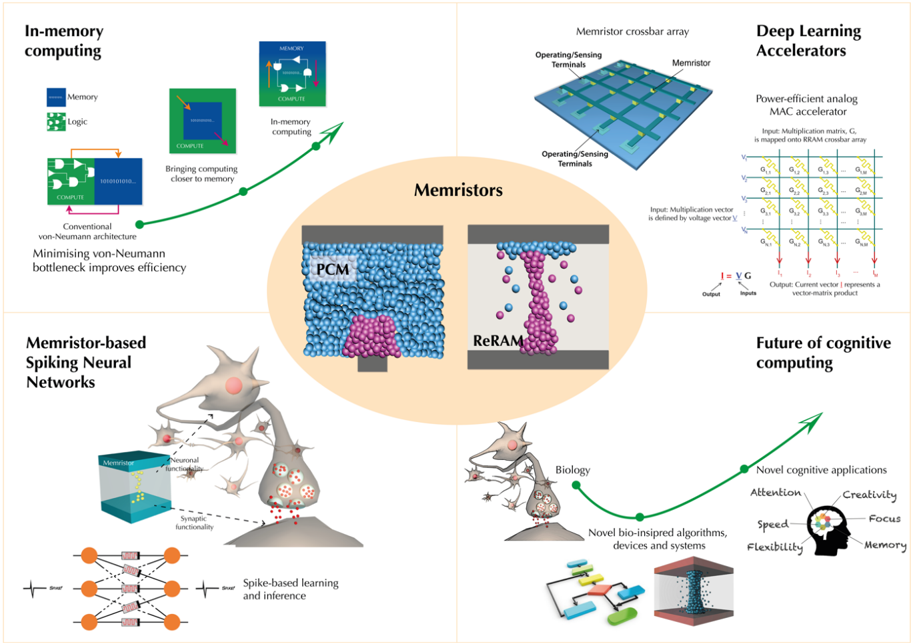

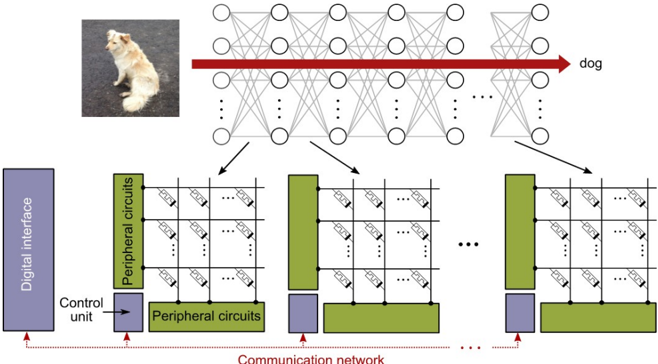

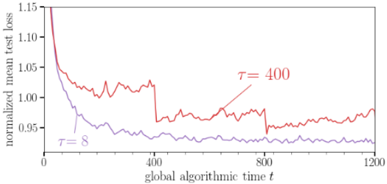

1.2 The landscape of different approaches and applications. In the context of this paper, memristors can be used in applications beyond simple memory devices [10] . A 'big picture' landscape of memristor-based approaches for AI is shown in Figure 1. There is more than one way that memristors can perform computing. A unique feature of memristor devices is the ability to co-locate memory and computing and to break the von Neumann bottleneck at the lowest, nanometre-scale level. One such approach is the concept of in-memory computing, which uses memory not only to store the data but also to perform computation at the same physical location. Furthermore, memristors have long been considered for deep learning acceleration. Specifically, memristive crossbar arrays physically represent weights in artificial neural networks as conductances at each crosspoint. When voltages are applied at one side of the crossbar and current sensed on the orthogonal terminals, the array provides vector-matrix multiplication in constant time step using Kirchhoff's and Ohm's laws. Vector-matrix multiplications dominate most DL algorithms - hundreds of thousands are often needed during training and inference. When weights are implemented as memristor conductances, there is no need for the extensive power-hungry data movement required by conventional digital systems based on the von Neumann architecture.

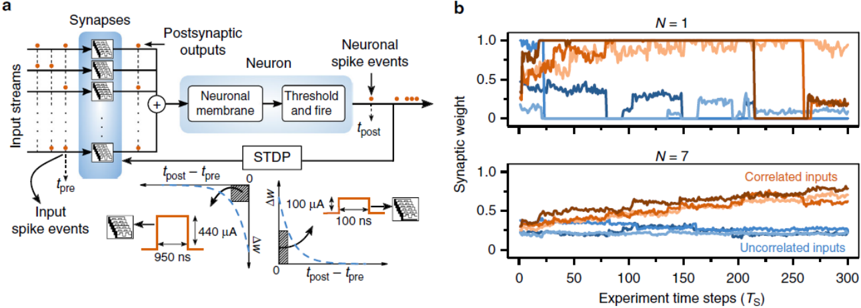

Other more bio-realistic concepts are also being explored. These include schemes relying on spike-based communication. The central premise of this approach can be summarised with the motto 'computing with time, not in time'. It has been shown that memristors can directly implement some functions of biological neurons and synapses, most importantly, synapse-like plasticity, and neuron-like integration and spiking. In these solutions, the information is encoded and transferred in the form of voltage or current spikes. Memristor resistances are used as proxies for synaptic strengths. More importantly, adjustment of the resistances is controlled according to local learning rules. One popular local learning rule is spike-timingdependent plasticity (STDP), which adjust a local state variable such as conductance dynamically based on the relative timing of spikes. In a simple example, the conductance of a memristive 'synapse' can be increased or decreased depending on the degree of overlap between pre- and post-synaptic voltage pulses. There also exist implementations that do not require overlapping pulses, instead utilising the volatile internal dynamics of memristive devices. Spike-based computing promises further improvements in power-efficiency, taking the inspiration from the remarkable efficiency of the human brain.

Finally, we speculate that, for future developments in AI, new knowledge and computational models from the fields of computational neuroscience could play a crucial role. Virtually all recent developments in ML and DL are driven by the field of computer science. At the same time, the algorithmic inspiration from neuroscience is mostly based on old models established as early as the 1950s. Although we are still at the infancy of understanding the full working principles of the biological brain, novel brain-inspired architectural principles, beyond simple probabilistic deep learning approaches, could lead to higher-level cognitive functionalities. One such example is the concept of reservoir computing, which we discuss briefly in the paper. It is unlikely that current digital CMOS transistor technology can be optimized for the implementation of much more dynamic and adaptive systems in an efficient way. In contrast, memristor-based systems, with their rich switching dynamics and many state variables, may provide a perfect substrate to build a new class of intelligent and efficient neuromorphic systems.

Figure 1. The landscape of memristor-based systems for Artificial Intelligence. In-memory computing aims to eliminate the von-Neumann bottleneck by implementing compute directly within the memory. Deep learning accelerators based on memristive crossbars are used to implement vector-matrix multiplication directly using Ohm's and Kirchhoff's laws. Spiking neural networks, a type of artificial neural networks, are biologically more plausible and do not operate with continuous signals, but use spikes to process and transfer data. Memristor systems could provide a hardware platform to implement spike-based learning and inference. More complex functionalities (neuromorphic), beyond simple digital switching CMOS paradigm, directly implemented in memristive hardware primitives, might fuel the next wave of higher cognitive systems.

<details>

<summary>Image 1 Details</summary>

### Visual Description

## Diagram: Memristor Applications

### Overview

The image presents a diagram showcasing various applications of memristors in computing, including in-memory computing, deep learning accelerators, spiking neural networks, and future cognitive computing. It illustrates the evolution from conventional von-Neumann architecture to memristor-based systems, highlighting their potential to improve efficiency and enable novel computing paradigms.

### Components/Axes

* **Central Theme:** Memristors

* **Applications:**

* In-memory computing

* Memristor crossbar array

* Deep Learning Accelerators

* Memristor-based Spiking Neural Networks

* Future of cognitive computing

* **Key Concepts:**

* Conventional von-Neumann architecture

* Spike-based learning and inference

* Novel bio-inspired algorithms, devices, and systems

* Novel cognitive applications

### Detailed Analysis

**1. In-memory computing (Top-Left)**

* Diagram shows a transition from separate memory and compute units to integrated in-memory computing.

* **Legend:**

* Blue: Memory

* Green: Logic

* **Text:**

* "Bringing computing closer to memory"

* "Conventional von-Neumann architecture"

* "Minimising von-Neumann bottleneck improves efficiency"

* A green arrow indicates the progression towards in-memory computing.

**2. Memristors (Center)**

* Illustrations of two types of memristors: PCM (Phase Change Memory) and ReRAM (Resistive Random-Access Memory).

* **PCM:** Shows a structure with a blue region and a pink region.

* **ReRAM:** Shows a structure with blue and pink particles moving within a channel.

**3. Memristor crossbar array (Top-Center)**

* Diagram of a memristor crossbar array with operating/sensing terminals.

* **Labels:**

* "Memristor crossbar array"

* "Operating/Sensing Terminals"

* "Memristor"

**4. Deep Learning Accelerators (Top-Right)**

* Diagram of a power-efficient analog MAC (Multiply-Accumulate) accelerator using an RRAM crossbar array.

* **Labels:**

* "Deep Learning Accelerators"

* "Power-efficient analog MAC accelerator"

* "Input: Multiplication matrix, G, is mapped onto RRAM crossbar array"

* "Input: Multiplication vector is defined by voltage vector V"

* "Output: Current vector I represents a vector-matrix product"

* "I = VG"

* "Output"

* "Inputs"

* The diagram shows a matrix representation of the multiplication process.

**5. Memristor-based Spiking Neural Networks (Bottom-Left)**

* Diagram illustrating the use of memristors in spiking neural networks.

* **Labels:**

* "Memristor-based Spiking Neural Networks"

* "Memristor"

* "Neuronal functionality"

* "Synaptic functionality"

* "Spike-based learning and inference"

* The diagram shows a neuron with synaptic connections and a simplified representation of a spiking neural network.

**6. Future of cognitive computing (Bottom-Right)**

* Diagram representing the future of cognitive computing enabled by memristors.

* **Labels:**

* "Future of cognitive computing"

* "Biology"

* "Novel bio-inspired algorithms, devices and systems"

* "Novel cognitive applications"

* A mind map shows key cognitive attributes: Attention, Creativity, Focus, Memory, Speed, Flexibility.

### Key Observations

* The diagram emphasizes the shift from traditional computing architectures to memristor-based systems.

* Memristors are presented as a key enabler for advanced computing paradigms like in-memory computing, deep learning, and cognitive computing.

* The diagram highlights the bio-inspired nature of memristor-based systems, particularly in spiking neural networks and cognitive computing.

### Interpretation

The diagram illustrates the potential of memristors to revolutionize computing by overcoming the limitations of conventional von-Neumann architectures. By integrating memory and processing, memristors offer significant advantages in terms of speed, energy efficiency, and scalability. The applications showcased in the diagram demonstrate the versatility of memristors and their potential to enable advanced computing paradigms such as artificial intelligence, cognitive computing, and neuromorphic computing. The emphasis on bio-inspired approaches suggests a trend towards developing computing systems that mimic the structure and function of the human brain.

</details>

## 2. In-memory computing

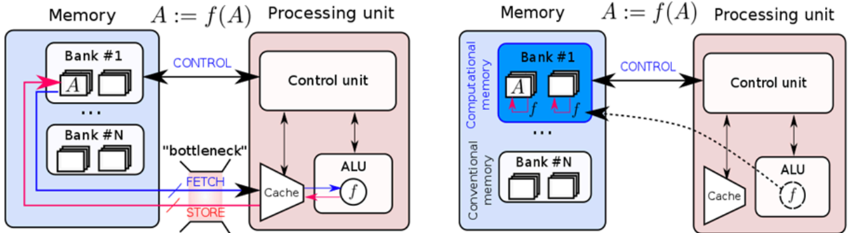

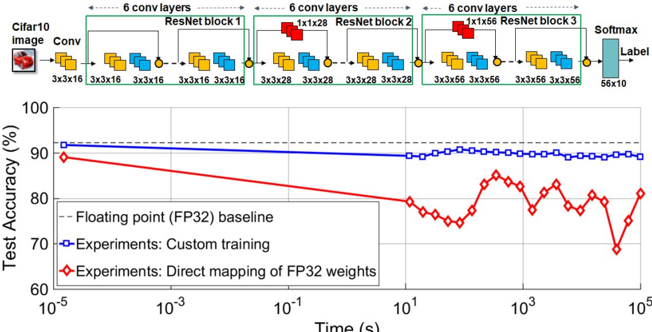

In the von Neumann architecture, which dates back to the 1940s, memory and processing units are physically separated and large amounts of data need to be shuttled back and forth between them during the execution of various computational tasks. The latency and energy associated with accessing data from the memory units are key performance bottlenecks for a range of applications, in particular for the increasingly prominent artificial intelligence related workloads [11] . The energy cost associated with moving data is a key challenge for both severely energy constrained mobile and edge computing as well as high performance computing in a cloud environment due to cooling constraints. The current approaches, such as using hundreds of processors in parallel [12] or application-specific processors [13] , are not likely to fully overcome the challenge of data movement. It is getting increasingly clear that novel architectures need to be explored where memory and processing are better collocated. In-memory computing is one such non-von Neumann approach where certain computational tasks are performed in place in the memory itself organized as a computational memory unit [14,15 ,16, 17]. As schematically illustrated in Figure 2, in-memory computing obviates the need to move data into a processing unit. Computing is performed by exploiting the physical attributes of the memory devices, their array-level organization, the peripheral circuitry as well as the control logic. In this paradigm, the memory is an active participant in the computational task. Besides reducing latency and energy cost associated with data movement, in-memory computing also has the potential to improve the computational time complexity associated with certain tasks due to the massive parallelism afforded by a dense array of millions of nanoscale memory devices serving as compute units. By introducing physical coupling between the memory devices, there is also a potential for further reduction in computational time complexity [18, 19]. Memristive devices such as PCM, ReRAM and MRAM [20, 21] are particularly well suited for in-memory computing.

## Processing unit & Conventional memory Processing unit & Computational memory

Figure 2. In-memory computing. In a conventional computing system, when an operation f is performed on data D, D has to be moved into a processing unit. This incurs significant latency and energy cost and creates the well-known von Neumann bottleneck. With in-memory computing, f(D) is performed within a computational memory unit by exploiting the physical attributes of the memory devices. This obviates the need to move D to the processing unit. (Adapted and reproduced with permission [14] , Copyright 2017, Nature Research)

<details>

<summary>Image 2 Details</summary>

### Visual Description

## System Architecture Diagram: Memory and Processing Unit Interaction

### Overview

The image presents two diagrams illustrating the interaction between memory and a processing unit. The left diagram depicts a conventional memory architecture, while the right diagram shows a computational memory architecture. Both diagrams highlight the flow of data and control signals between the memory banks and the processing unit components.

### Components/Axes

**Left Diagram (Conventional Memory):**

* **Memory:** Labeled "Memory" at the top. Contains two memory banks: "Bank #1" and "Bank #N". Each bank contains multiple memory locations represented by small rectangles.

* The memory banks are enclosed in a light blue rounded rectangle.

* **Processing Unit:** Labeled "Processing unit" at the top. Contains a "Control unit", "ALU" (Arithmetic Logic Unit), and "Cache".

* The processing unit is enclosed in a light red rounded rectangle.

* **Data Flow:**

* **FETCH:** Data is fetched from memory to the cache via a "bottleneck". The "FETCH" label is associated with a red arrow pointing from the memory to the cache.

* **STORE:** Data is stored from the cache to memory. The "STORE" label is associated with a pink arrow pointing from the cache to the memory.

* **Control:** Control signals are sent from the control unit to the memory. The "CONTROL" label is associated with a blue arrow pointing from the control unit to Bank #1.

* Data flows between Bank #1 and Bank #N via pink and blue arrows.

* **Equation:** "A := f(A)" is displayed above the processing unit, indicating that the processing unit applies a function 'f' to data 'A'.

**Right Diagram (Computational Memory):**

* **Memory:** Labeled "Memory" at the top. Contains two memory banks: "Bank #1" and "Bank #N". Each bank contains multiple memory locations represented by small rectangles.

* Bank #1 is labeled as "Computational memory" and is enclosed in a blue rounded rectangle.

* Bank #N is labeled as "Conventional memory" and is enclosed in a white rounded rectangle.

* **Processing Unit:** Labeled "Processing unit" at the top. Contains a "Control unit", "ALU" (Arithmetic Logic Unit), and "Cache".

* The processing unit is enclosed in a light red rounded rectangle.

* **Data Flow:**

* The function 'f' is applied directly within the computational memory bank (Bank #1), indicated by small pink arrows and 'f' labels within the bank.

* **Control:** Control signals are sent from the control unit to the memory. The "CONTROL" label is associated with a blue arrow pointing from the control unit to Bank #1.

* A dashed black arrow indicates a potential data flow path from the computational memory to the cache.

* **Equation:** "A := f(A)" is displayed above the processing unit, indicating that the processing unit applies a function 'f' to data 'A'.

### Detailed Analysis or ### Content Details

**Left Diagram (Conventional Memory):**

* Data 'A' is stored in Bank #1.

* The "bottleneck" suggests a limitation in the data transfer rate between memory and cache.

* The ALU performs the function 'f' on data fetched from memory.

* The control unit manages the data flow and operations.

**Right Diagram (Computational Memory):**

* Data 'A' is stored in Bank #1 (Computational Memory).

* The function 'f' is applied directly within the memory bank, reducing the need to transfer data to the ALU for processing.

* The dashed arrow suggests that the processed data can be sent to the cache if needed.

* Bank #N (Conventional Memory) operates similarly to the memory banks in the left diagram.

### Key Observations

* The primary difference between the two diagrams is the location where the function 'f' is applied. In the conventional memory architecture, 'f' is applied in the ALU within the processing unit. In the computational memory architecture, 'f' is applied directly within the memory bank.

* The "bottleneck" label in the conventional memory diagram highlights a potential performance limitation.

* The computational memory architecture aims to improve performance by reducing data transfer between memory and the processing unit.

### Interpretation

The diagrams illustrate the evolution from a conventional memory architecture to a computational memory architecture. The conventional architecture requires data to be transferred to the processing unit for computation, which can be a bottleneck. The computational memory architecture aims to overcome this bottleneck by performing computations directly within the memory bank. This reduces data transfer, potentially leading to improved performance and energy efficiency. The dashed arrow in the computational memory diagram suggests that the processed data can still be accessed by the processing unit if needed, providing flexibility in the system design.

</details>

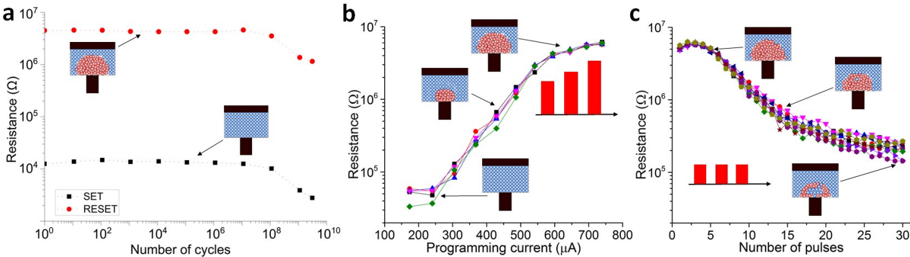

Figure 3. The key physical attributes of memristive devices that facilitate in- memory computing . a) Binary storage capability whereby the devices can be switched between high and low resistance values in a repeatable manner (Adapted and reproduced with permission [22] . Copyright 2019, IOP Publishing). b) Multi- level storage capability whereby the devices can be programmed to a continuum of resistance values by the application of appropriate programming pulses (Adapted and reproduced with permission [23] . Copyright 2018, American Institute of Physics) c) The accumulative behavior whereby the resistance of a device can be progressively decreased by the successive application of identical programming pulses (Adapted and reproduced with permission [23] . Copyright 2018, American Institute of Physics).

<details>

<summary>Image 3 Details</summary>

### Visual Description

## Chart/Diagram Type: Multiple Line Graphs and Schematics

### Overview

The image presents three line graphs (a, b, c) showing the resistance of a device under different conditions. Each graph is accompanied by schematic diagrams illustrating the device's state.

### Components/Axes

**Graph a:**

* **X-axis:** Number of cycles (logarithmic scale from 10^0 to 10^10)

* **Y-axis:** Resistance (Ω) (logarithmic scale from 10^4 to 10^7)

* **Legend:**

* SET (black squares)

* RESET (red circles)

* **Schematics:** Two schematics are present, one showing a high-resistance state (RESET) and the other showing a low-resistance state (SET).

**Graph b:**

* **X-axis:** Programming current (µA) (linear scale from 100 to 800)

* **Y-axis:** Resistance (Ω) (logarithmic scale from 10^4 to 10^7)

* **Data Series:** Multiple overlapping lines, distinguished by color and marker shape (green diamonds, blue circles, black squares, pink triangles, purple inverted triangles).

* **Schematics:** Three schematics are present, showing the device's state at different programming currents. A bar graph is also present, showing increasing resistance with increasing current.

**Graph c:**

* **X-axis:** Number of pulses (linear scale from 0 to 30)

* **Y-axis:** Resistance (Ω) (logarithmic scale from 10^5 to 10^7)

* **Data Series:** Multiple overlapping lines, distinguished by color and marker shape (green diamonds, blue circles, black squares, pink triangles, purple inverted triangles).

* **Schematics:** Two schematics are present, showing the device's state after different numbers of pulses. A pulse diagram is also present, showing three pulses.

### Detailed Analysis or ### Content Details

**Graph a:**

* **SET (black squares):** The resistance remains relatively constant around 10^4 Ω across the entire range of cycles.

* **RESET (red circles):** The resistance remains relatively constant around 10^7 Ω across the entire range of cycles.

**Graph b:**

* All data series show a similar trend: a sharp increase in resistance as the programming current increases from 200 µA to 800 µA.

* At 200 µA, the resistance is approximately 2 * 10^4 Ω to 5 * 10^4 Ω.

* At 800 µA, the resistance is approximately 5 * 10^6 Ω to 8 * 10^6 Ω.

**Graph c:**

* All data series show a similar trend: a decrease in resistance as the number of pulses increases from 0 to 30.

* At 0 pulses, the resistance is approximately 5 * 10^6 Ω to 8 * 10^6 Ω.

* At 30 pulses, the resistance is approximately 1 * 10^5 Ω to 3 * 10^5 Ω.

### Key Observations

* **Graph a:** The device exhibits stable SET and RESET resistance values over a large number of cycles.

* **Graph b:** The programming current significantly affects the resistance of the device.

* **Graph c:** The number of pulses significantly affects the resistance of the device.

### Interpretation

The data suggests that the device is a resistive switching memory element. Graph a demonstrates the endurance of the device, showing that it can maintain its SET and RESET states over many cycles. Graph b shows that the resistance can be modulated by applying different programming currents. Graph c shows that the resistance can be modulated by applying different numbers of pulses. The schematics provide a visual representation of the device's state during these processes. The bar graph in (b) and the pulse diagram in (c) visually reinforce the trends observed in the line graphs.

</details>

There are several key physical attributes that enable in-memory computing using memristive devices. First of all, the ability to store two levels of resistance/conductance values in a nonvolatile manner and to reversibly switch from one level to the other (binary storage capability) can be exploited for computing. Figure 3 a shows the resistance values achieved upon repeated switching of a representative PCM device between low resistance SET states and high resistance RESET states. Due to the SET and RESET states, resistance could serve as an additional logic state variable. In conventional CMOS, voltage serves as the single logic state variable. The input signals are processed as voltage signals and are output as voltage signals. By combining CMOS circuitry with memristive devices, it is possible to exploit the additional resistance state variable. For example, the RESET state could indicate logic '0' and the SET state could denote logic '1'. This enables logical operations that rely on the interaction between the voltage and resistance state variables and could enable the seamless integration of processing and storage. This is the essential idea behind memristive logic, which is an active area of research [24, 25, 26] . Memristive logic has the potential to impact application areas such as image processing [27] , encryption and database query [28] . Brain-inspired hyperdimensional computing that involves the manipulation of large binary vectors has recently emerged as another promising application area for in-memory logic [29, 30] . Going beyond binary storage, certain memristive devices can also be programmed to a continuum of resistance or conductance values (analog storage capability). For example, Figure 3 b shows a continuum of resistance levels in a PCM device achieved by the application of programming pulses with varying amplitude. The device is first programmed to the fully crystalline state, after which RESET pulses are applied with progressively increasing amplitude. The device resistance is measured after the application of each RESET pulse. Due to this property, it is possible to program a memristive device to a certain desired resistance value through iterative programming by applying several pulses in a closed-loop manner [31] . Yet another physical attribute that enables in-memory computing is the accumulative behavior exhibited by certain memristive devices. In these devices, it is possible to progressively reduce the device resistance by the successive application of SET pulses with the same amplitude. And in certain cases, it is possible to progressively increase the resistance by the successive application of RESET pulses. Experimental measurement of this accumulative behavior in a

PCM device is shown in Figure 3 c . This accumulative behavior is central to applications such as training deep neural networks which is described later. The intrinsic stochasticity associated with the switching behavior in memristive devices can also be exploited for inmemory computing [32] . Applications include stochastic computing [33] and physically unclonable functions [34] .

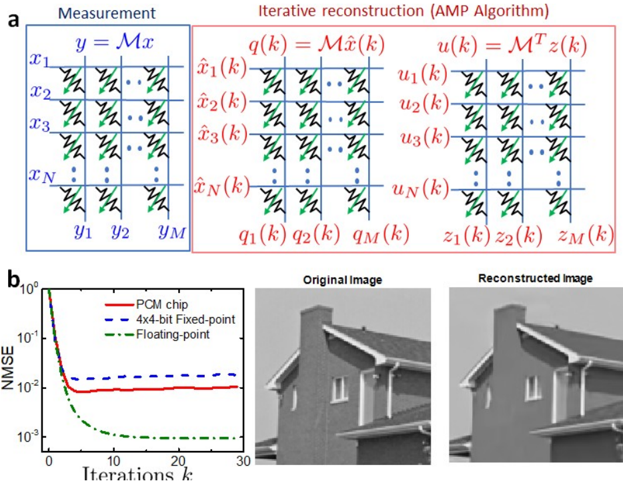

× Figure 4. a) Compressed sensing involves one matrix-vector multiplication. Data recovery is performed via an iterative scheme, using several matrix-vector multiplications on the very same measurement matrix and its transpose. b) An experimental illustration of compressed sensing recovery in the context of image compression is presented, showing 50% compression of a 128x128 pixel image. The normalized mean square error (NMSE) associated with the reconstructed signal is plotted against the number of iterations. Adapted and reproduced with permission [35] , Copyright 2018, IEEE.

<details>

<summary>Image 4 Details</summary>

### Visual Description

## Chart/Diagram Type: Composite Figure - System Diagram, Line Plot, and Image Comparison

### Overview

The image presents a composite figure consisting of three parts: (a) a system diagram illustrating a measurement and iterative reconstruction process using the AMP algorithm, (b) a line plot comparing the NMSE (Normalized Mean Squared Error) performance of three different methods (PCM chip, 4x4-bit Fixed-point, and Floating-point) over iterations, and (c) a visual comparison of an original image and its reconstructed version.

### Components/Axes

**Part (a): System Diagram**

* **Title:** Measurement (left, blue box) and Iterative reconstruction (AMP Algorithm) (right, red box)

* **Measurement Block:**

* Equation: y = Mx (blue)

* Input variables: x1, x2, x3, ..., xN (left side)

* Output variables: y1, y2, ..., yM (bottom)

* Diagram: A grid structure with arrows indicating the flow from x_i to y_j.

* **Iterative Reconstruction Block:**

* Equations: q(k) = M x̂(k) and u(k) = M^T z(k) (red)

* Variables: x̂1(k), x̂2(k), x̂3(k), ..., x̂N(k) (left side of first equation)

* Variables: q1(k), q2(k), ..., qM(k) (bottom of first equation)

* Variables: u1(k), u2(k), u3(k), ..., uN(k) (top of second equation)

* Variables: z1(k), z2(k), ..., zM(k) (bottom of second equation)

* Diagram: Similar grid structure with arrows indicating flow.

**Part (b): Line Plot**

* **Title:** None explicitly given, but it's implied to be a comparison of NMSE vs. Iterations for different methods.

* **Y-axis:** NMSE (Normalized Mean Squared Error), logarithmic scale from 10^-3 to 10^0.

* **X-axis:** Iterations k, linear scale from 0 to 30.

* **Legend:** (top-right)

* Red solid line: PCM chip

* Blue dashed line: 4x4-bit Fixed-point

* Green dash-dotted line: Floating-point

**Part (c): Image Comparison**

* **Titles:** Original Image (left) and Reconstructed Image (right)

* Images: Grayscale images of a house.

### Detailed Analysis or ### Content Details

**Part (a): System Diagram**

* The diagram illustrates a measurement process where the input vector 'x' is transformed into the output vector 'y' using a matrix 'M'.

* The iterative reconstruction process uses the AMP (Approximate Message Passing) algorithm to estimate 'x' from 'y'.

* The variables x̂(k), q(k), u(k), and z(k) represent intermediate values in the iterative process at iteration 'k'.

**Part (b): Line Plot**

* **PCM chip (Red solid line):** Starts at approximately 0.2 NMSE, quickly decreases to around 0.01 NMSE within the first 5 iterations, and then plateaus around 0.01 NMSE for the remaining iterations.

* **4x4-bit Fixed-point (Blue dashed line):** Starts at approximately 0.8 NMSE, decreases to around 0.02 NMSE within the first 5 iterations, and then plateaus around 0.02 NMSE for the remaining iterations.

* **Floating-point (Green dash-dotted line):** Starts at approximately 1 NMSE, rapidly decreases to below 0.001 NMSE within the first 10 iterations, and continues to decrease slightly for the remaining iterations.

**Part (c): Image Comparison**

* The original image shows a clear, detailed view of a house.

* The reconstructed image shows a slightly blurred version of the same house, indicating some loss of detail during the reconstruction process.

### Key Observations

* The Floating-point method achieves the lowest NMSE and converges the fastest.

* The PCM chip method performs better than the 4x4-bit Fixed-point method in terms of NMSE.

* The iterative reconstruction process reduces the NMSE over iterations for all three methods.

* The reconstructed image is visually similar to the original image, but with some loss of detail.

### Interpretation

The composite figure demonstrates the performance of different methods for reconstructing an image using an iterative algorithm. The line plot shows that the Floating-point method is the most accurate and efficient, while the PCM chip and 4x4-bit Fixed-point methods have higher NMSE values. The image comparison visually confirms that the reconstruction process introduces some level of distortion, but the overall structure of the image is preserved. The system diagram provides a high-level overview of the measurement and reconstruction process, highlighting the key variables and equations involved. The data suggests that the choice of method significantly impacts the accuracy and efficiency of the image reconstruction process.

</details>

× × A very useful in-memory computing primitive enabled by the binary and analog nonvolatile storage capability is matrix-vector multiplication (MVM) [36, 37] . The physical laws that are exploited to perform this operation are Ohm's law and Kirchhoff's current summation laws. For example, to perform the operation Ax = b , the elements of A are mapped linearly to the conductance values of memristive devices organized in a crossbar configuration. The x values are mapped linearly to the amplitudes of read voltages and are applied to the crossbar along the rows. The result of the computation, b , will be proportional to the resulting current measured along the columns of the array. Compressed sensing and recovery are one of the applications that could benefit from an in-memory computing unit that performs matrix-vector multiplications. The objective behind compressed sensing is to acquire a large signal at subNyquist sampling rate and to subsequently reconstruct that signal accurately. Unlike most other compression schemes, sampling and compression are done simultaneously, with the signal getting compressed as it is sampled. Such techniques have widespread applications in the domain of medical imaging, security systems, and camera sensors. The compressed measurements can be thought of as a mapping of a signal x of length N to a measurement vector y of length M < N. If this process is linear, then it can be modeled by an M N measurement matrix M. The idea is to store this measurement matrix in the in-memory computing unit, with memristive devices organized in a cross-bar configuration (see Figure 4(a)). In this manner the compression operation can be performed in O(1) time complexity.

To recover the original signal from the compressed measurements, an approximate message passing algorithm (AMP) can be used, using an iterative algorithm that involves several matrix-vector multiplications on the very same measurement matrix and its transpose. In this way the same matrix that was coded in the in-memory computing unit can also be used for the reconstruction, reducing reconstruction complexity from O( MN) to O( N ). An experimental illustration of compressed sensing recovery in the context of image compression is shown in Figure 4(b). A 128x128-pixel image was compressed by 50% and recovered using the measurement matrix elements encoded in a PCM array. The normalized mean square error associated with the recovered signal is plotted as a function of the number of iterations. A remarkable property of AMP is that its convergence rate is independent of the precision of the matrix-vector multiplications. The lack of precision only results in a higher error floor, which may be considered acceptable for many applications. Note that, in this application, the measurement matrix remains fixed and hence the property of PCM that is exploited is the multi-level storage capability.

## 3. Deep learning accelerators

<details>

<summary>Image 5 Details</summary>

### Visual Description

## Diagram: Neural Network and Memristor Crossbar Array

### Overview

The image depicts a neural network architecture and its implementation using a memristor crossbar array. The diagram illustrates the flow of information from an input image (a dog) through the neural network layers to an output classification ("dog"). The neural network's connections are then mapped onto a physical memristor crossbar array for hardware implementation.

### Components/Axes

* **Input:** Image of a dog (top-left)

* **Neural Network:** A multi-layered neural network with interconnected nodes (circles). The connections between layers are represented by lines.

* **Output:** "dog" (top-right), indicating the classification result.

* **Memristor Crossbar Array:** A grid-like structure composed of horizontal and vertical lines, with memristors (represented by resistor symbols) at the intersections.

* **Digital Interface:** A blue block labeled "Digital interface" on the left.

* **Control Unit:** A blue block labeled "Control unit" below the digital interface.

* **Peripheral Circuits:** Green blocks labeled "Peripheral circuits" surrounding the memristor arrays.

* **Communication Network:** A dotted red line labeled "Communication network" at the bottom.

* **Arrows:** Arrows indicate the flow of information from the neural network layers to the memristor arrays.

### Detailed Analysis

* **Neural Network Structure:** The neural network consists of multiple layers of interconnected nodes. The connections between nodes represent the weights of the neural network. A red arrow highlights a specific path through the network, leading to the "dog" output.

* **Memristor Array Mapping:** The connections of the neural network are mapped onto the memristor crossbar array. Each memristor represents a synaptic weight in the neural network. The peripheral circuits provide the necessary control and read/write operations for the memristor array.

* **Digital Interface and Control Unit:** The digital interface provides the input to the neural network and receives the output. The control unit manages the operation of the memristor array.

* **Communication Network:** The communication network facilitates data transfer between the different components of the system.

* **Array Structure:** Each memristor array is connected to peripheral circuits on the top and right sides. A control unit is connected to the bottom of the peripheral circuits. The digital interface is connected to the control unit.

### Key Observations

* The diagram illustrates the concept of implementing a neural network using memristor technology.

* The memristor crossbar array provides a compact and energy-efficient way to implement the synaptic weights of the neural network.

* The peripheral circuits and control unit are essential for managing the operation of the memristor array.

### Interpretation

The diagram demonstrates how a neural network can be physically realized using a memristor crossbar array. This approach offers potential advantages in terms of power consumption, speed, and scalability compared to traditional software-based implementations. The memristor array acts as a hardware accelerator for the neural network, enabling faster and more efficient processing of data. The diagram highlights the key components and their interactions in this type of system, showcasing the integration of neural network algorithms with emerging hardware technologies. The use of memristors to represent synaptic weights allows for a dense and energy-efficient implementation of neural networks, which is particularly relevant for applications in edge computing and artificial intelligence.

</details>

Communicationnetwork

Figure 5. Deep learning based on in-memory computing. The various layers of a neural network are mapped to a computational memory unit where memristive devices are organized in a crossbar configuration. The synaptic weights are stored in the conductance state of the memristive devices. A global communication network is used to send data from one array to another. Adapted and reproduced with permission [17] , Copyright 2020, Nature Research.

Deep neural networks (DNNs), loosely inspired by biological neural networks, consist of parallel processing units called neurons interconnected by plastic synapses. By tuning the weights of these interconnections using millions of labelled examples, these networks are able to perform certain supervised learning tasks remarkably well. These networks are typically trained via a supervised learning algorithm based on gradient descent. During the training phase, the input data is forward propagated through the neuron layers with the synaptic networks performing multiply-accumulate operations. The final layer responses are compared with input data labels and the errors are back-propagated. Both steps involve sequences of matrix-vector multiplications. Subsequently, the synaptic weights are updated to reduce the error. This optimization approach can take multiple days or weeks to train state-of-the-art networks on conventional computers. Hence, there is a significant effort towards the design of custom ASICs based on reduced precision arithmetic and highly optimized dataflow [13, 38] . However, the need to shuttle millions of synaptic weight values between the memory and processing unit remains a key performance bottleneck and hence in-memory computing is being explored as an alternative approach for both inference and training of DNNs [39, 40] . The essential idea is to map the various layers of a neural network to an in-memory computing unit where memristive devices are organized in a crossbar configuration (see Figure 5). The synaptic weights are stored in the conductance state of the memristive devices and the propagation of data through each layer is performed in a single step by inputting the data to the crossbar rows and deciphering the results at the columns.

<details>

<summary>Image 6 Details</summary>

### Visual Description

## Neural Network Architecture and Performance Chart

### Overview

The image presents a diagram of a convolutional neural network (CNN) architecture, followed by a chart comparing the test accuracy of different training methods over time. The CNN architecture consists of convolutional layers and ResNet blocks, while the chart compares the performance of a floating-point baseline, custom training, and direct mapping of FP32 weights.

### Components/Axes

**Top: CNN Architecture Diagram**

* **Header:** "6 conv layers" is repeated above each ResNet block.

* **Input:** "Cifar10 image" followed by "Conv" block.

* The input image is represented by a small image of a red car.

* The "Conv" block has dimensions "3x3x16".

* **ResNet Blocks:** There are three ResNet blocks labeled "ResNet block 1", "ResNet block 2", and "ResNet block 3".

* ResNet block 1: Contains convolutional layers with dimensions "3x3x16".

* ResNet block 2: Contains convolutional layers with dimensions "3x3x28" and a "1x1x28" layer.

* ResNet block 3: Contains convolutional layers with dimensions "3x3x56" and a "1x1x56" layer.

* **Output:** "Softmax" layer with dimensions "56x10" leading to "Label".

* **Connections:** Blocks are connected by arrows indicating the flow of data. Small yellow circles are present at the end of each block.

**Bottom: Test Accuracy Chart**

* **Y-axis:** "Test Accuracy (%)", ranging from 60 to 100. Markers at 70, 80, 90, and 100.

* **X-axis:** "Time (s)" on a logarithmic scale, ranging from 10<sup>-5</sup> to 10<sup>5</sup>. Markers at 10<sup>-5</sup>, 10<sup>-3</sup>, 10<sup>-1</sup>, 10<sup>1</sup>, 10<sup>3</sup>, and 10<sup>5</sup>.

* **Legend (bottom-left):**

* "-- Floating point (FP32) baseline" (dashed black line)

* "Experiments: Custom training" (solid blue line with square markers)

* "Experiments: Direct mapping of FP32 weights" (solid red line with diamond markers)

### Detailed Analysis

**CNN Architecture:**

* The network processes a Cifar10 image through an initial convolutional layer.

* The image then passes through three ResNet blocks, each containing multiple convolutional layers.

* The dimensions of the convolutional layers increase through the network (16 -> 28 -> 56).

* The output of the final ResNet block is fed into a Softmax layer to produce a label.

**Test Accuracy Chart:**

* **Floating point (FP32) baseline (dashed black line):** The baseline accuracy is approximately constant at 92%.

* **Experiments: Custom training (solid blue line with square markers):** The accuracy starts at approximately 90% at 10<sup>-5</sup> seconds, decreases slightly to approximately 89% at 10<sup>1</sup> seconds, and then remains relatively stable around 89-90% until 10<sup>5</sup> seconds.

* **Experiments: Direct mapping of FP32 weights (solid red line with diamond markers):** The accuracy starts at approximately 89% at 10<sup>-5</sup> seconds, decreases to approximately 75% at 10<sup>1</sup> seconds, and then fluctuates between 75% and 85% from 10<sup>1</sup> to 10<sup>5</sup> seconds.

### Key Observations

* The custom training method (blue line) maintains a relatively stable accuracy over time, close to the FP32 baseline.

* The direct mapping of FP32 weights (red line) initially performs similarly to the custom training, but its accuracy degrades significantly over time and exhibits more fluctuation.

* The x-axis is logarithmic, indicating that the performance is being evaluated over a wide range of time scales.

### Interpretation

The data suggests that custom training is a more effective approach than direct mapping of FP32 weights for maintaining accuracy over time. The direct mapping method may suffer from issues related to weight quantization or adaptation, leading to the observed performance degradation and fluctuations. The FP32 baseline provides a benchmark for the maximum achievable accuracy, and the custom training method comes close to achieving this level of performance. The chart highlights the importance of proper training techniques when dealing with different weight representations or hardware constraints.

</details>

Time (s)

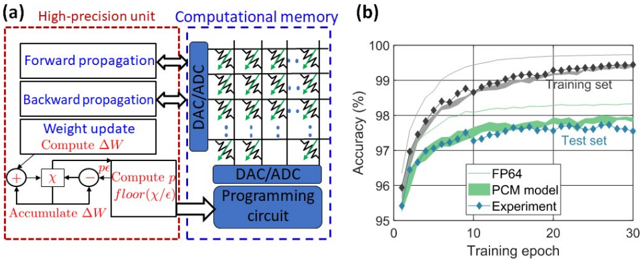

Figure 6. Deep learning inference. Experimental results on ResNet-32 using the CIFAR-10 dataset. The classification accuracies obtained via the direct mapping and custom training approaches are compared to the floating-point baseline. Adapted and reproduced with permission [40] , Copyright 2019, IEEE.

Deep learning inference refers to just the forward propagation in a DNN once the weights have been learned. Both binary and analogue storage capability of memristive devices can be exploited for the MVM operations associated with the inference operation. The key challenges are the inaccuracies associated with programming the devices to a specified synaptic weight as well as drift, noise etc. associated with the conductance values [41] . Due to these reasons, the synaptic weights that are obtained by training in high precision arithmetic (e.g. 32-bit floating point) cannot be mapped directly to computational memory. However, it can be shown that by customizing the training procedure to make it aware of these devicelevel nonidealities, it is possible to obtain synaptic weights that are suitable for being mapped to an in-memory computing unit [42,40] . A more recent approach is to use the committee machines of multiple smaller neural networks. The approach shows the promise of increasing inference accuracy without increasing the number of devices by using a committee of smaller neural networks [43] . Figure 6 shows mixed hardware/software experimental results using a prototype multi-level PCM chip. The synaptic weights are mapped to PCM devices organized in a 2-PCM differential configuration (723,444 PCM devices in total). It can be seen that the custom training scheme approaches the floating-point base-line, whereas the direct mapping approach fails to deliver sufficient accuracy. The slight temporal decline in accuracy is attributed to the conductance drift exhibited by PCM devices [44] . However, in spite of the drift, a classification accuracy of close to 90% is maintained over a significant duration of time.

Figure 7. Deep learning training. a) Schematic illustration of the mixed-precision architecture for training DNNs. b) The synaptic weight distributions and classification accuracies are compared between the experiments and floating point baseline [45] .

<details>

<summary>Image 7 Details</summary>

### Visual Description

## Diagram and Chart: High-Precision Unit and Accuracy vs. Training Epoch

### Overview

The image consists of two parts: (a) a diagram illustrating the architecture of a high-precision unit connected to computational memory, and (b) a chart showing the accuracy of different models (FP64, PCM model, and Experiment) over training epochs.

### Components/Axes

#### Part (a): Diagram of High-Precision Unit and Computational Memory

* **Title:** (a) High-precision unit Computational memory

* **Regions:**

* **High-precision unit:** Enclosed in a red dashed rectangle. Contains the following components:

* Forward propagation (blue text)

* Backward propagation (blue text)

* Weight update (red text): Compute ΔW

* Mathematical operations: A series of interconnected symbols representing addition (+), multiplication (X), and subtraction (-). The operations are labeled as "Compute p floor(χ/ε)" (red text) and "Accumulate ΔW" (red text).

* **Computational memory:** Enclosed in a blue dashed rectangle. Contains the following components:

* DAC/ADC (Digital-to-Analog Converter/Analog-to-Digital Converter) (blue text)

* Memory array: A grid-like structure with symbols resembling resistors or memory cells.

* DAC/ADC (Digital-to-Analog Converter/Analog-to-Digital Converter) (blue text)

* Programming circuit (blue text)

* **Flow:** Arrows indicate the flow of data and control signals between the high-precision unit and the computational memory.

#### Part (b): Accuracy vs. Training Epoch Chart

* **Title:** (b)

* **Axes:**

* X-axis: Training epoch (labeled from 0 to 30 in increments of 10)

* Y-axis: Accuracy (%) (labeled from 95 to 100 in increments of 1)

* **Legend:** Located in the bottom-right corner of the chart.

* FP64 (light gray line)

* PCM model (green shaded region)

* Experiment (blue line with diamond markers)

* **Data Series:**

* Training set (black line with diamond markers): Located near the top of the chart.

* Test set (blue text): Located near the middle of the chart.

### Detailed Analysis

#### Part (a): Diagram

The diagram illustrates a system where a high-precision unit interacts with computational memory. The high-precision unit performs forward and backward propagation, updates weights, and performs mathematical operations. The computational memory stores data and is controlled by a programming circuit. DAC/ADC converters facilitate communication between the analog memory and the digital processing unit.

#### Part (b): Chart

* **FP64 (light gray line):** The accuracy starts at approximately 95.8% at epoch 0 and increases rapidly, reaching approximately 99.5% by epoch 10. It then plateaus and remains relatively constant until epoch 30.

* **PCM model (green shaded region):** The accuracy starts at approximately 95.5% at epoch 0 and increases, reaching approximately 97.8% by epoch 15. It then fluctuates slightly around this value until epoch 30. The shaded region indicates the variability or uncertainty in the PCM model's accuracy.

* **Experiment (blue line with diamond markers):** The accuracy starts at approximately 95.3% at epoch 0 and increases, reaching approximately 97.3% by epoch 15. It then fluctuates slightly around this value until epoch 30.

* **Training set (black line with diamond markers):** The accuracy starts at approximately 95.8% at epoch 0 and increases rapidly, reaching approximately 98.5% by epoch 10. It then increases slowly, reaching approximately 99.5% by epoch 30.

### Key Observations

* The FP64 model achieves the highest accuracy, followed by the training set.

* The PCM model and the Experiment data have similar accuracy trends, with the Experiment data showing slightly lower accuracy.

* All models show a rapid increase in accuracy during the initial training epochs, followed by a plateau or slower increase.

### Interpretation

The diagram in part (a) illustrates the hardware architecture used for the experiment. The chart in part (b) demonstrates the performance of different models in terms of accuracy over training epochs. The FP64 model serves as a benchmark, achieving the highest accuracy. The PCM model and the Experiment data represent alternative approaches, with the Experiment data likely representing the actual hardware implementation. The results suggest that the PCM model and the Experiment data achieve comparable accuracy, but are lower than the FP64 model. The initial rapid increase in accuracy indicates that the models are learning effectively during the early stages of training. The subsequent plateau suggests that the models are approaching their maximum performance or that further training is needed to improve accuracy.

</details>

In-memory computing can also be used in the context of supervised training of DNNs with backpropagation. When performing training of a DNN encoded in crossbar arrays, forward propagation is performed in the same way as inference described above. Next, backward propagation is performed by inputting the error gradient from the subsequent layer onto the columns of the current layer and deciphering the result from the rows. Subsequently the error gradient is computed. Finally, the weight update is performed based on the outer product of activations and error gradients of each layer. This weight update relies on the accumulative behaviour of memristive devices. Recent deep learning research shows that when training DNNs, it is possible to perform the forward and backward propagations rather imprecisely while the gradients need to be accumulated in high precision [ 46 ] . This observation makes the DL training problem amenable to the mixed-precision in-memory computing approach that was recently proposed [ 47 ] . The in-memory compute unit is used to store the synaptic weights and to perform the forward and backward passes, while the weight changes are accumulated in high precision (Figure 7(a)) [ 48 , 49 ] . When the accumulated weight exceeds a certain threshold, pulses are applied to the corresponding memory devices to alter the synaptic weights. This approach was tested using the handwritten digit classification problem based on the MNIST data set. A two-layered neural network was employed with 2-PCM devices in differential configuration (approx. 400,000 devices) representing the synaptic weights. Resulting test accuracy after 20 epochs of training was approx. 98% (Figure 7(b)). After training, inference on this network was performed for over a year with marginal reduction in the test accuracy. The crossbar topology also facilitates the estimation of the gradient and the in-place update of the resulting synaptic weight all in O(1) time complexity [ 50 , 39] . By obviating the need to perform gradient accumulation externally, this approach could yield better performance than the mixed-precision approach. However, significant improvements to the memristive technology, in particular the accumulative behavior, is needed to apply this to a wide range of DNNs [ 51 , 52 ] .

Compared to the charge-based memory devices that are also used for in-memory computing [53, 54, 55] , a key advantage of memristive devices is the potential to be scaled to dimensions of a few nanometers [56, 57, 58, 59,60] . Most of the memristive devices are also suitable for back end of line integration, thus enabling their integration with a wide range of front-end CMOS technologies. Another key advantage is the non-volatility of these devices that would obviate the need for computing systems to be constantly connected to a power supply. However, there are also challenges that need to be overcome. The significant intra-device and intra-device variability associated with the SET and RESET states is a key challenge for applications where memristive devices are used for logical operations. For applications that rely on analogue storage capability, a significant challenge is programming variability that captures the inaccuracies associated with programming an array of devices to desired conductance values. In ReRAM, this variability is attributed mostly to the stochastic nature of filamentary switching and one prominent approach to counter this is that of establishing preferential paths for CF formation [ 61 , 62 ] . Representing single computational elements by using multiple memory devices is another promising approach [ 63 ] . Yet another challenge is the temporal and temperature-induced variations of the programmed conductance values. The resistance 'drift' in PCM devices, which is attributed to the intrinsic structural relaxation of the amorphous phase, is an example. The concept of projected phase change memory is a promising approach towards tackling 'drift' [ 64 , 65 ] . The requirements that the memristive devices need to fulfil when employed for computational memory are heavily application dependant. For memristive logic, high cycling endurance ( > 10 12 cycles) and low device-to-device variability of the SET/RESET resistance values are critical. For computational tasks involving read-only operations, such as matrix-vector multiplication, it is required that the conductance states remain relatively unchanged during their execution. It is also desirable to have a gradual analogue-type switching characteristic for programming a continuum of resistance values in a single device. A linear and symmetric accumulative behaviour is also required in applications where the device conductance needs to be incrementally updated such as in deep learning training [ 66 ] . For stochastic computing applications, random device variability is not problematic, but graceful device degradation is highly desirable, as described in [ 67 ].

## 4. Spiking Neural Networks and Memristors

As opposed to the deep learning networks discussed above, spiking neural networks (SNNs) can more naturally incorporate the notion of time in signal encoding and processing. SNNs are typically modelled on the integrate-and-fire behaviour of neurons in the brain. In this framework, neurons communicate with each other using binary signals or spikes. The arrival of a spike at a synapse triggers a current flow into the downstream neuron, with the magnitude of the current weighted by the effective conductance of the synapse. The incoming currents are integrated by the neuron to determine its membrane potential and a spike is issued when the potential exceeds a threshold. This spiking behaviour can be triggered in a deterministic or probabilistic manner. Once a spike is issued, the membrane potential is reset to a resting potential or decreased according to some predetermined rule. The integration is limited to a specific time window, or else a leak factor is incorporated in the integration, endowing the neuron model with a finite memory of past spiking events.

Compared to the realization of second-generation deep neural networks (DNNs discussed in the previous section), SNNs can potentially have significant improvements in efficiency. The first reason for this comes from the underlying signal encoding mechanism. The calculation of the output of a neuron involves the determination of the weighted sum of synaptic weights with real-valued neuronal outputs of the previous layer. For a fully connected second generation DNN with 𝑁 neurons in each layer, this requires 𝑁 ! multiplications of real valued numbers, typically stored in low precision representations. In contrast, the forward propagation operation in an SNN only requires addition operations, as the input neuronal signals are binary spike signals. To elaborate, assume that the input signal is encoded as a spike train with duration 𝑇 , with a minimum inter-spike interval of ∆𝑡 . If the probability of a spike at any instant of time is 𝑝 , then on an average 𝑁𝑝𝑇/∆𝑡 spikes have to be propagated through the synapses, and this requires 𝑁 ! 𝑝𝑇/∆𝑡 addition operations. In most modern processors, the cost of multiplication, 𝐶 " , is 3-4 times higher than that of addition, 𝐶 # . Hence, provided the neuronal and synaptic variables required for computation are available in the processor, SNNs offer a path to more efficient computation if the inequality

$$C _ { a } p \left ( \frac { T } { \Delta t } \right ) < C _ { m }$$

holds. Hence, it is important to develop algorithms for SNNs that minimize 𝑝 and (𝑇/∆𝑡) to improve computational efficiency. This requires the use of sparse binary signal encoding schemes that go beyond rate coding that is typically used in SNNs today. The following section will discuss strategies to develop general-purpose learning rules for SNNs that satisfy such constraints.

The second potential for efficiency improvement of SNNs as compared to second-generation networks arises thanks to novel memory-processor architectures based on memristive devices. While SNNs can be implemented using Si CMOS SRAM or DRAM technologies, the advent of novel nanoscale memristive devices provides opportunities for significant improvements in overall computational efficiency.

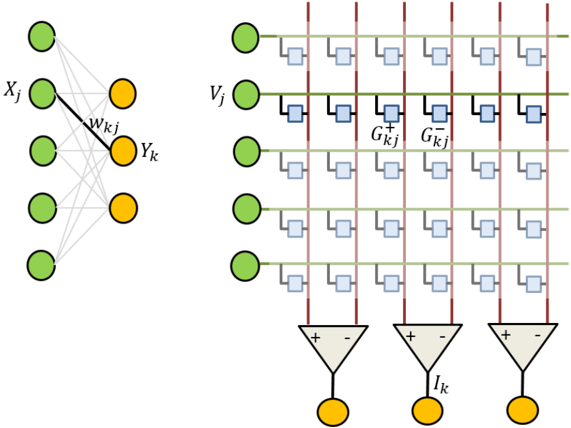

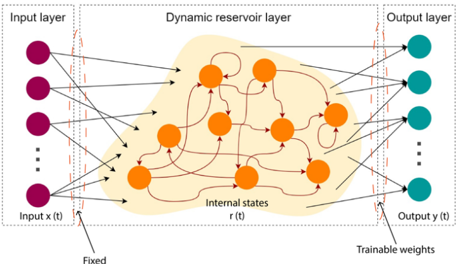

Figure 8. A cross-bar array based representation of an SNN. Each synaptic weight is represented by the differential conductance of two nanoscale devices in the crossbar.

<details>

<summary>Image 8 Details</summary>

### Visual Description

## Neural Network Diagram: Conceptual Model and Hardware Implementation

### Overview

The image presents a conceptual diagram of a neural network and a corresponding hardware implementation. The left side illustrates the weighted connections between input and output neurons, while the right side depicts a potential hardware architecture using memristors to represent synaptic weights.

### Components/Axes

**Left Side (Conceptual Model):**

* **Nodes:** Green circles represent input neurons (labeled Xj), and orange circles represent output neurons (labeled Yk).

* **Connections:** Gray lines represent connections between input and output neurons. A thicker black line represents a specific connection with weight wkj.

**Right Side (Hardware Implementation):**

* **Input Neurons:** Green circles represent input neurons (labeled Vj).

* **Output Neurons:** Orange circles represent output neurons (labeled Ik).

* **Memristor Array:** A grid of light blue squares represents memristors, which store the synaptic weights.

* **Horizontal Lines:** Green lines represent the input lines.

* **Vertical Lines:** Red lines represent the output lines.

* **Differential Amplifiers:** Gray triangles represent differential amplifiers.

* **Conductances:** G+kj and G-kj represent positive and negative conductances, respectively.

### Detailed Analysis

**Left Side (Conceptual Model):**

* There are four input neurons (Xj) and two output neurons (Yk).

* Each input neuron is connected to each output neuron.

* The weight of the connection between input neuron j and output neuron k is denoted as wkj.

**Right Side (Hardware Implementation):**

* There are five input neurons (Vj) and three output neurons (Ik).

* Each input neuron is connected to each output neuron through a memristor.

* Each memristor is connected to a differential amplifier.

* The differential amplifier sums the currents from the memristors and produces an output current Ik.

* The memristors are arranged in a grid, with each row corresponding to an input neuron and each column corresponding to an output neuron.

* The memristors are connected to the input and output lines through switches.

* The switches are used to program the memristor conductances.

* The positive and negative conductances (G+kj and G-kj) are used to represent both positive and negative synaptic weights.

### Key Observations

* The left side of the image shows a simplified neural network with weighted connections.

* The right side of the image shows a potential hardware implementation of the neural network using memristors.

* The memristors are used to store the synaptic weights.

* The differential amplifiers are used to sum the currents from the memristors and produce an output current.

### Interpretation

The image illustrates the mapping of a conceptual neural network model onto a physical hardware architecture. The left side represents the abstract mathematical relationships between neurons and their connections, while the right side demonstrates how these relationships can be implemented using memristors and differential amplifiers. This type of hardware implementation offers potential advantages in terms of power consumption, speed, and scalability compared to traditional software-based neural networks. The use of memristors allows for the efficient storage and processing of synaptic weights, while the differential amplifiers enable the summation of currents to produce the output signals. The diagram highlights the potential for building energy-efficient and high-performance neural networks using emerging memristor technology.

</details>

Memristive devices can be integrated at the junctions of crossbar arrays to represent the weights of synapses, and CMOS circuits at the periphery can be designed to implement the neuronal integration and learning logic. As mentioned above, this architecture enables the computation of spike propagation operation in an efficient manner based on Kirchhoff's law as:

$$I _ { k } = \sum _ { j } \left ( G _ { k j } ^ { + } - G _ { k j } ^ { - } \right ) V _ { j }$$

In this formula, 𝑉 % denotes the applied voltage pulses that are triggered when an input neuron spikes and are applied to the line connected to the 𝑗 th input neuron, 𝐺 $% & and 𝐺 $% ' are the conductances of the devices configured in a differential configuration to represent the synaptic weight, and 𝐼 $ is the total incoming current into the 𝑘 th output neuron. The small form factor of the devices, coupled with the scalability of operating voltages and currents beyond what is possible with conventional CMOS, suggests that these architectures can have several orders of magnitude efficiency improvement over Silicon based implementations [68,69] .

However, apart from the already mentioned non-idealities of memritive devices, crossbar arrays with more than 2048x2048 devices cannot be fabricated and operated reliably due to the resistance drop on the wires and the sneak-paths that corrupt the measurement and programming of synaptic states. One approach to mitigate these issues is to design neurosynaptic cores with smaller crossbars and associated neuron circuits, tile these cores on a 2D array, and provide communication fabrics between the cores [70] . Such tiled neurosynaptic core-based designs are particularly amenable for realizing SNNs, as only binary spikes corresponding to intermittently active spiking neurons need to be transported between cores, as opposed to real-valued neuronal variables that are active for all the neurons in the core in the case of deep learning networks. This is the second inherent advantage that SNNs have over DNNs for computational efficiency improvement.

Overcoming the reliability challenges mentioned above is essential for building reliable systems, and would require the co-optimization of algorithms and architectures that are designed to mitigate or leverage these non-ideal behaviours for computation. Two kinds of systems can be visualized based on the application mode. Inference engines, which do not support on-chip learning, can be designed based on memristive devices integrated on crossbars, where the devices are programmed to the desired conductance states based on the weights obtained from software training. However, as memristive devices support incremental conductance changes by the application of suitable electrical programming pulses, it is also possible to design learning systems where network weight updates are implemented on-chip in an event-driven manner [82] . There are also many recent examples where these devices have been engineered to mimic the integration and fire characteristics of biological neurons [71, 72,73], potentially enabling the realization of all-memristor implementations of spiking neural networks [74] . The field is still in its infancy, and so far, has only witnessed small proof-ofconcept demonstrations. We now discuss some of the approaches that have been explored towards realizing memristive based inference-only spiking networks as well as learning networks with SNNs.

4.1. Memristive SNNs for inference . A common approach to develop SNNs is to start with a second-generation ANN trained using traditional backpropagation-based methods, and then convert the resulting network to a spiking network in software. These solutions are based on weight-normalization schemes so that the spike rates of the neurons in the SNN are proportional to the activations of the neurons in the ANN [75, 76] . While this should in principle result in SNNs with comparable accuracies as their second-generation counterparts, some device-aware re-training would typically be necessary when the network is implemented in hardware due to the non-linearity and limited dynamic ranges of nanoscale devices.

One of the differentiating features of inference engines is that the nanoscale devices storing state variables are programmed only rarely, compared to the number of reads (potentially at every inference cycle). Since higher-energy programming cycles have a stronger effect in degrading device lifetimes compared to the lower-energy read cycles, this mode of operation can have better overall system reliability compared to that of learning systems.

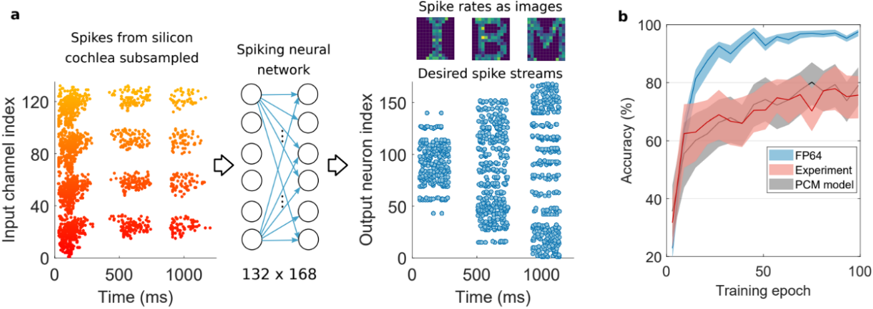

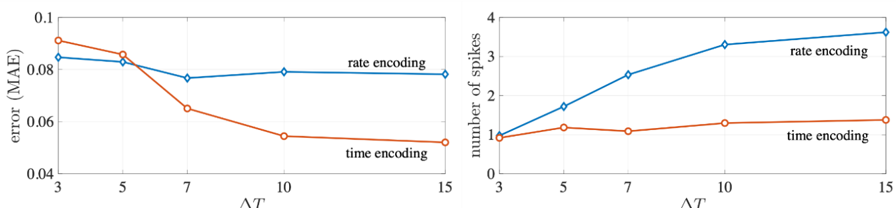

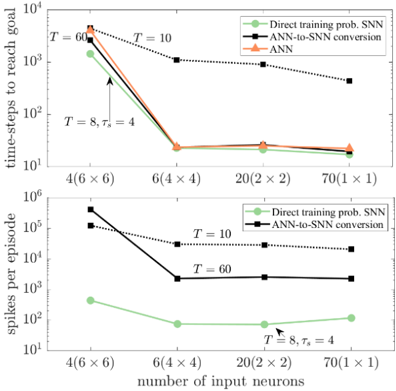

In a preliminary hardware demonstration leveraging this approach, R. Midya et al. used memristors based on SiOxNy:Ag to implement compact oscillatory neurons whose output voltage oscillation frequency is proportional to the input current [77] . In this proof-of-concept demonstration of a 3-layer network, ANN to SNN conversion was limited to the last layer alone, but the approach could be extended to hidden layers as well.