# All-in-One Analog AI Hardware: On-Chip Training and Inference with Conductive-Metal-Oxide/HfOx ReRAM Devices

**Authors**: VictoriaClerico, WooseokChoi, TommasoStecconi, FolkertHorst, LauraBégon-Lours, MatteoGaletta, AntonioLa Porta, NikhilGarg, FabienAlibart, Bert JanOffrein, ValeriaBragaglia

[1] Donato Francesco Falcone

1] IBM Research - Europe, Rüschlikon, 8803, Zürich, Switzerland

2] Institut Interdisciplinaire d’Innovation Technologique (3IT), Université de Sherbrooke, Sherbrooke, QC J1K 0A5, Quebec, Canada

3] Institute of Electronics, Microelectronics and Nanotechnology (IEMN), Université de Lille, Villeneuve d’Ascq, 59650, France

## Abstract

Analog in-memory computing is an emerging paradigm designed to efficiently accelerate deep neural network workloads. Recent advancements have focused on either inference or training acceleration. However, a unified analog in-memory technology platform—capable of on-chip training, weight retention, and long-term inference acceleration—has yet to be reported. This work presents an all-in-one analog AI accelerator, combining these capabilities to enable energy-efficient, continuously adaptable AI systems. The platform leverages an array of analog filamentary conductive-metal-oxide (CMO)/HfO x resistive switching memory cells (ReRAM) integrated into the back-end-of-line (BEOL). The array demonstrates reliable resistive switching with voltage amplitudes below 1.5 V, compatible with advanced technology nodes. The array’s multi-bit capability (over 32 stable states) and low programming noise (down to 10 nS) enable a nearly ideal weight transfer process, more than an order of magnitude better than other memristive technologies. Inference performance is validated through matrix-vector multiplication simulations on a 64×64 array, achieving a root-mean-square error improvement by a factor of 20 at 1 second and 3 at 10 years after programming, compared to state-of-the-art. Training accuracy closely matching the software equivalent is achieved across different datasets. The CMO/HfO x ReRAM technology lays the foundation for efficient analog systems accelerating both inference and training in deep neural networks.

keywords: In-memory computing, Analog ReRAM, Deep Neural Networks, Training, Inference

## 1 Introduction

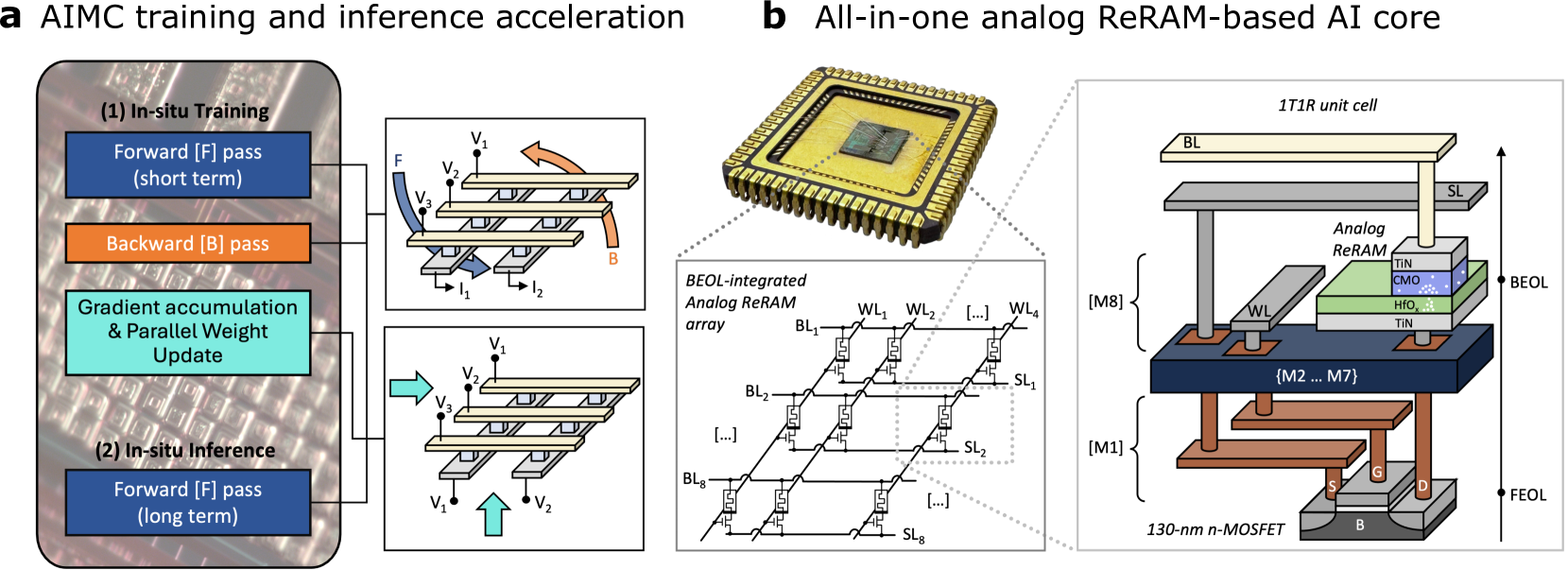

Modern computing systems rely on von Neumann architectures, where instructions and data must be transferred between memory and the processing unit to perform computational tasks. This data transfer, particularly recurrent and massive in prominent artificial intelligence (AI)-related workloads, results in significant latency and energy overhead [1]. Digital AI accelerators address this challenge through computational parallelism, bringing memory closer to the processing units, and exploiting application-specific processors [2, 3]. This approach has demonstrated to bring significant improvements in throughput and efficiency for running deep neural networks (DNNs) [4], but the physical separation between memory and compute units persists. Analog in-memory computing (AIMC) [5] is a promising approach to eliminate this separation and so achieve further power and efficiency improvements in deep-learning workloads [6], by enabling some arithmetic and logic operations to be performed directly at the location where the data is stored. By mapping the weights of DNNs onto crossbar arrays of resistive devices and by leveraging Ohm’s and Kirchhoff’s physical laws, matrix-vector multiplications (MVMs)—the most recurrent operation in AI-workloads [7] —are performed in memory with $O(1)$ time complexity [5, 8, 4]. Recent demonstrations of the AIMC paradigm have primarily focused on accelerating the inference step of digitally trained DNNs [9, 10, 11, 12]. However, the increasing computing demands of modern AI models make the training phase orders of magnitude more costly in time and expenses than inference, highlighting the need for efficient hardware acceleration based on the AIMC paradigm. For instance, Gemini 1.0 Ultra required over $5\cdot 10^{25}$ floating-point operations (FLOPs), approximately 100 days, $\mathrm{24\,MW}$ of power, and an estimated cost of 30 million dollars for training [13]. Analog training acceleration imposes even more stringent requirements on resistive devices. In addition to inference (i.e., the forward pass), the back-propagation of errors, gradient computation, and weight update steps must be performed during the learning phase. However, in the digital domain updating the weights of a matrix of size NxN requires $O(N^{2})$ digital operations, leading to a significant drop in efficiency and speed. Beyond the forward pass, the AIMC approach enables acceleration of (1) backward pass through MVMs transposing the inputs and outputs, (2) gradient computation, and (3) the weight update through gradual bidirectional conductance changes upon external stimuli, all with $O(1)$ time complexity. To achieve this, the ideal analog resistive device should exhibit bidirectional, linear, and symmetric conductance updates in response to an open-loop programming pulse scheme (i.e., without the need for verification following each pulse) [4, 14]. Promising technologies include redox-based resistive switching memory (ReRAM) [15, 16], electro-chemical random access memory (ECRAM) [17], and capacitive weight elements [18]. Addressing the various non-idealities of these technologies [19] requires the co-optimization of technology and designated training algorithms. Gokmen et al. [20] proposed an efficient, fully parallel approach that leverages the coincidence of stochastic voltage pulse trains to carry out outer-product calculations and weight updates entirely within memory, in $O(1)$ time complexity. To relax the device symmetry requirements, a novel training algorithm, known as Tiki-Taka, was designed based on this parallel scheme [21]. The primary advantage of the Tiki-Taka approach lies in reduced device symmetry constraints across the entire conductance (G) range, focusing instead on a localized symmetry point where increases and decreases in G are balanced [21]. More recently, the Tiki-Taka version 2 (TTv2) algorithm was demonstrated in hardware [22] on small-scale tasks using optimized analog ReRAM technology in a 6-Transistor-1ReRAM unit cell crossbar array configuration. However, TTv2 faces some convergence issues when the reference conductance is not programmed with high precision [23]. Analog gradient accumulation with dynamic reference (AGAD) learning algorithm (i.e., TTv4) was proposed to overcome the reference conductance limitation, providing enhanced and robust performance [23]. From a technology perspective, the addition of an engineered conductive-metal-oxide (CMO) layer in a conventional HfO x -based ReRAM metal/insulator/metal (M/I/M) stack has been shown to improve switching characteristics in terms of the number of analog states, stochasticity, symmetry point, and endurance, compared to conventional M/I/M technology [24, 25, 26]. However, while CMO/HfO x ReRAM technology has proven to meet all the fundamental device criteria for on-chip training [24], array-level assessment and BEOL integration remain unexplored. Furthermore, although accelerating DNN training using AIMC is more challenging than inference, a unified technology platform capable of performing on-chip training, retaining the weights, and enabling long-term inference acceleration has yet to be reported. This work fills this gap by demonstrating an all-in-one AI accelerator based on CMO/HfO x ReRAM technology, able to perform analog acceleration of both training and long-term inference operations. Such an integrated approach paves the way for highly autonomous, energy-efficient, and continuously adaptable AI systems, opening new paths for real-time learning and inference applications. The flowchart in Fig. 1 a illustrates the all-in-one analog training and inference challenge addressed in this study. To achieve this goal, CMO/HfO x ReRAM devices, integrated into the BEOL of a $\mathrm{130\,nm}$ complementary metal-oxide-semiconductor (CMOS) technology node with copper interconnects (see ”Methods” section ”Device fabrication” for details), are arranged in an array architecture using a 1T1R unit cell. Compared to implementations that use multiple transistors to control the resistive switching, the 1T1R unit cell maximizes memory density, which is crucial for storing large AI models on a single chip. Fig. 1 b shows an image of the all-in-one analog ReRAM-based AI core used in this work, with the corresponding 8x4 array architecture and the schematic of the BEOL integrated 1T1R cells. The CMO/HfO x ReRAM array is first studied in a quasi-static regime by statistically characterizing the devices’ electro-forming step and quasi-static switching response. A physical 3D finite-element model (FEM) is developed to represent the geometry of the conductive filament and analytically describe the charge transport mechanism within these cells. Subsequently, the weight transfer accuracy and conductance relaxation are experimentally characterized on the 8x4 array. These measurements enable the demonstration of the core’s inference capabilities, validated through representative MVM accuracy simulations on a 64×64 array. After demonstrating the MVM accuracy of the CMO/HfO x ReRAM core, analog switching experiments using an open-loop identical pulse scheme demonstrated the suitability of the same core for analog on-chip training acceleration. To assess the training performance, a realistic device model was used in the simulation, accounting for measured characteristics such as non-linear and asymmetric switching behavior, as well as inter- and intra-device variabilities. The training performance was validated using AGAD on fully connected and long short-term memory (LSTM) neural networks, demonstrating scalability from small to large-scale neural networks.

<details>

<summary>x1.png Details</summary>

### Visual Description

## Diagram: AIMC Training/Inference Acceleration and ReRAM-Based AI Core Architecture

### Overview

The image presents two technical diagrams:

1. **AIMC Training/Inference Acceleration** (Left): A flowchart showing in-situ training and inference processes with gradient accumulation and weight updates.

2. **All-in-one Analog ReRAM-Based AI Core** (Right): A layered hardware architecture diagram illustrating a BEOL-integrated analog ReRAM array and 1T1R unit cells.

---

### Components/Axes

#### AIMC Training/Inference Acceleration (Left Diagram)

- **Steps**:

- **In-situ Training**:

- Forward pass (F) (short term)

- Backward pass (B)

- Gradient accumulation & Parallel Weight Update

- **In-situ Inference**:

- Forward pass (F) (long term)

- **Components**:

- Voltage sources: V₁, V₂, V₃

- Current sources: I₁, I₂

- Arrows indicate data flow direction (e.g., F → B → Gradient Update → Inference).

- **Color Coding**:

- Blue: Forward pass (F)

- Orange: Backward pass (B)

- Teal: Gradient accumulation & Weight Update

#### ReRAM-Based AI Core (Right Diagram)

- **Key Layers**:

- **BEOL (Bottom Electrode Layer)**:

- Analog ReRAM array with BL (Bit Line) and SL (Select Line) connections.

- 1T1R unit cells (1 Transistor, 1 Resistor) with BL, SL, and analog ReRAM.

- **Memory Stack**:

- M1–M8 layers (red, blue, green, yellow) with TIN (Titanium Nitride) and CMO (Copper Manganese Oxide) materials.

- **FEOL (Front Electrode Layer)**:

- 130-nm n-MOSFET transistors.

- **Color Coding**:

- Red: M1 layer

- Blue: M2–M7 layers

- Green: M8 layer

- Yellow: BL/SL lines

---

### Detailed Analysis

#### AIMC Training/Inference Acceleration

- **Training Process**:

- Forward pass (F) applies input data (V₁, V₂, V₃) to the system.

- Backward pass (B) propagates errors (I₁, I₂) for gradient calculation.

- Gradient accumulation and parallel weight updates occur simultaneously.

- **Inference Process**:

- Long-term forward pass (F) uses updated weights (V₁, V₂) for predictions.

#### ReRAM-Based AI Core

- **1T1R Unit Cell**:

- BL and SL lines control access to analog ReRAM cells.

- Analog ReRAM acts as both memory and computational element.

- **Material Stack**:

- TIN (Titanium Nitride) and CMO (Copper Manganese Oxide) layers enable resistive switching for analog computation.

- **Layering**:

- M1–M8 layers form a vertical stack, with BEOL at the bottom and FEOL at the top.

---

### Key Observations

1. **AIMC Acceleration**:

- Training and inference are optimized by integrating gradient updates during forward/backward passes.

- Parallel weight updates reduce latency compared to traditional training.

2. **ReRAM Architecture**:

- BEOL integration minimizes area overhead by embedding ReRAM directly with memory layers.

- 1T1R design balances transistor control with resistive memory for energy efficiency.

---

### Interpretation

- **AIMC Training**: The in-situ approach suggests a focus on real-time learning, where weights are updated dynamically during data processing. This could enable faster adaptation to new data without separate training phases.

- **ReRAM Core**: The analog ReRAM array leverages resistive switching for energy-efficient computation, while the 1T1R structure ensures precise control over memory cells. The vertical layering (M1–M8) indicates a compact, high-density design suitable for edge AI applications.

- **Synergy**: The AIMC training methodology likely complements the ReRAM core by enabling rapid weight updates during inference, enhancing overall system responsiveness.

No numerical data or trends are present in the image. The diagrams emphasize architectural design and process flow rather than quantitative metrics.

</details>

Figure 1: All-in-one AIMC challenge. a Schematic representation of the key steps required to perform on-chip training and inference with analog acceleration. Each step is executed using a crossbar array of resistive devices. b CMO/HfO x ReRAM AI core used in this work, consisting of an 8×4 array of 1T1R unit cells. From a fabrication perspective, each ReRAM cell is integrated into the BEOL of a $\mathrm{130\,nm}$ NMOS transistor with copper interconnects.

## 2 Results

### 2.1 Quasi-static array characterization and modelling

The quasi-static electrical characterization and analytical transport modelling of the 8x4 CMO/HfO x ReRAM array are presented here.

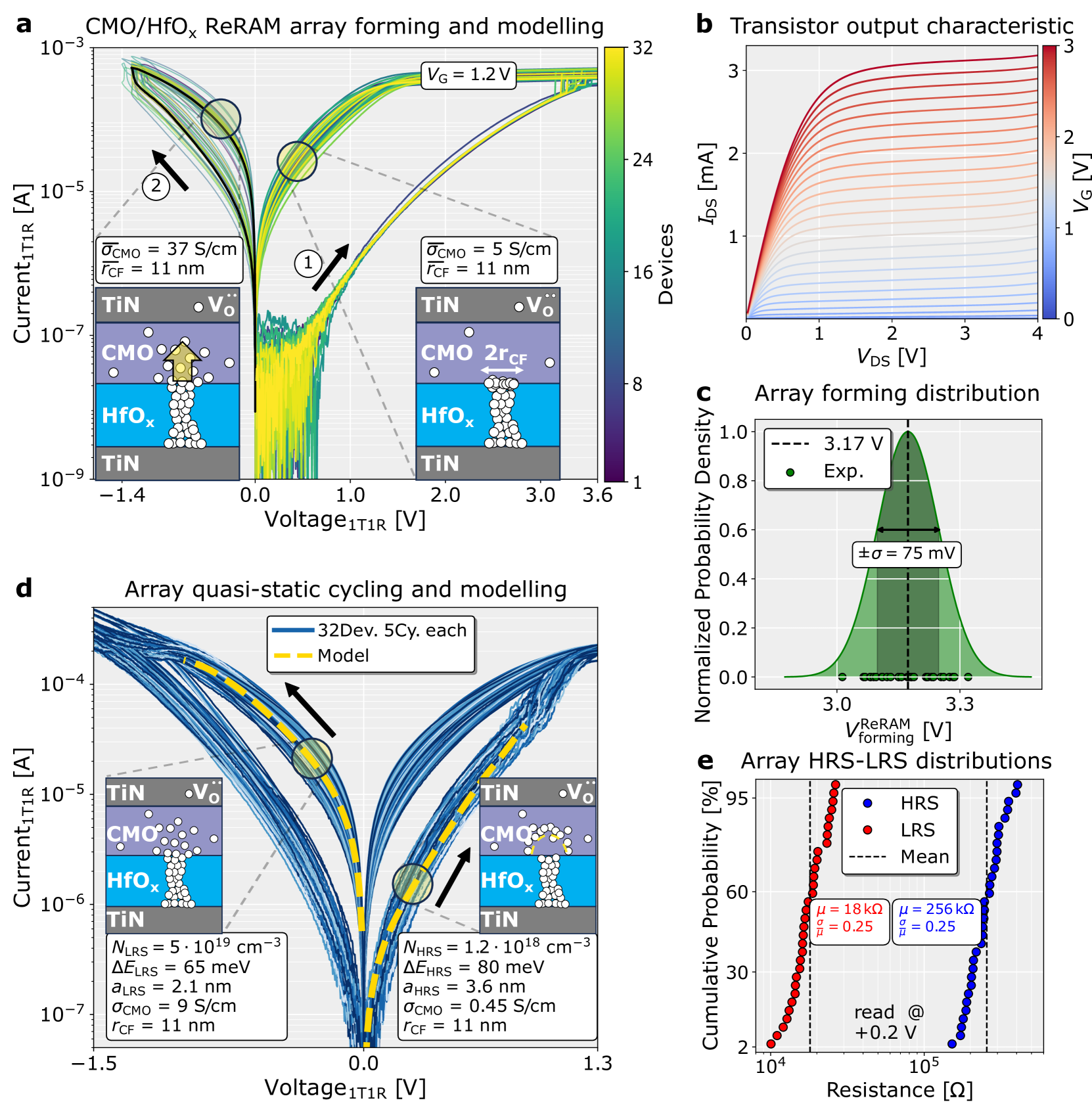

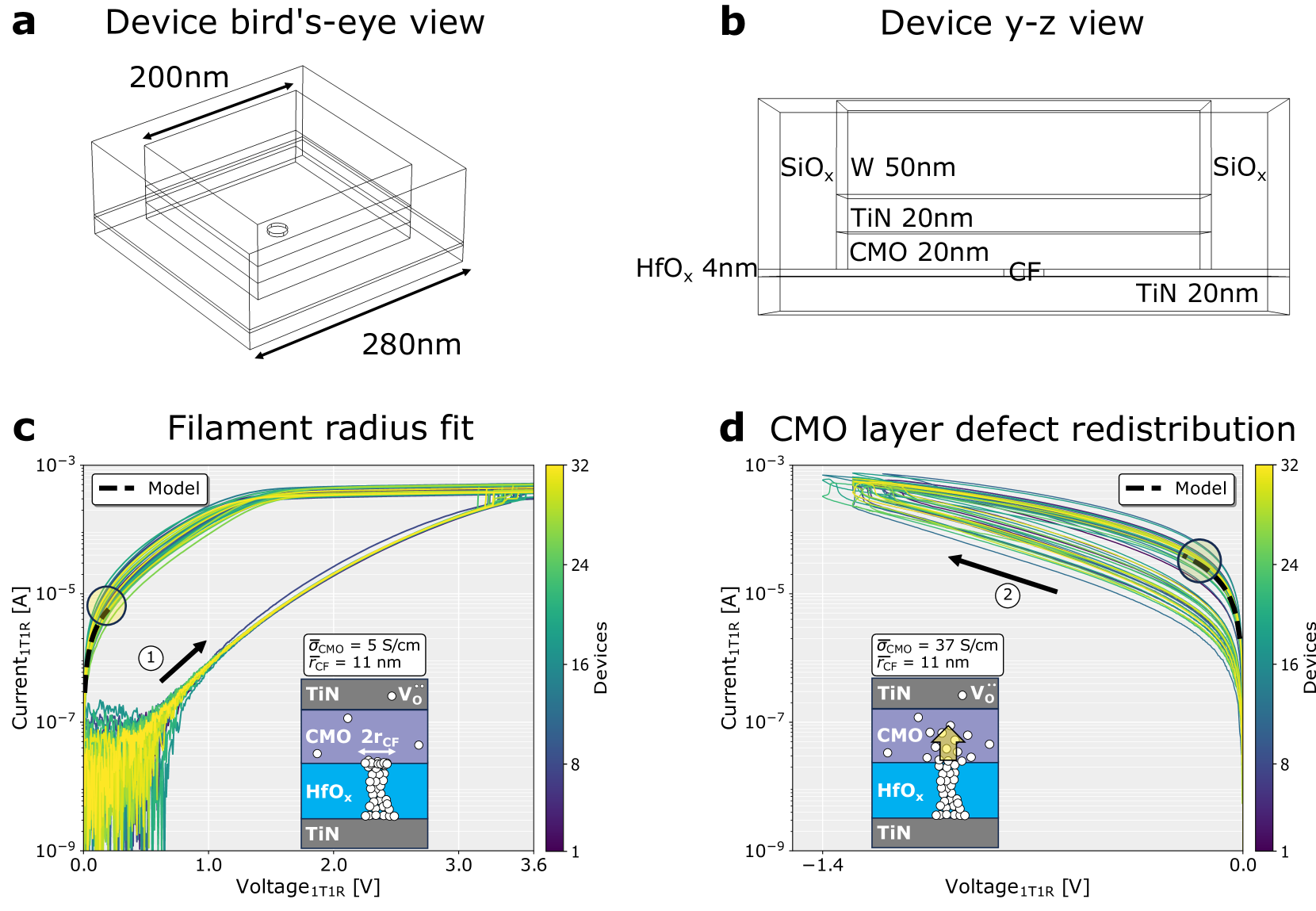

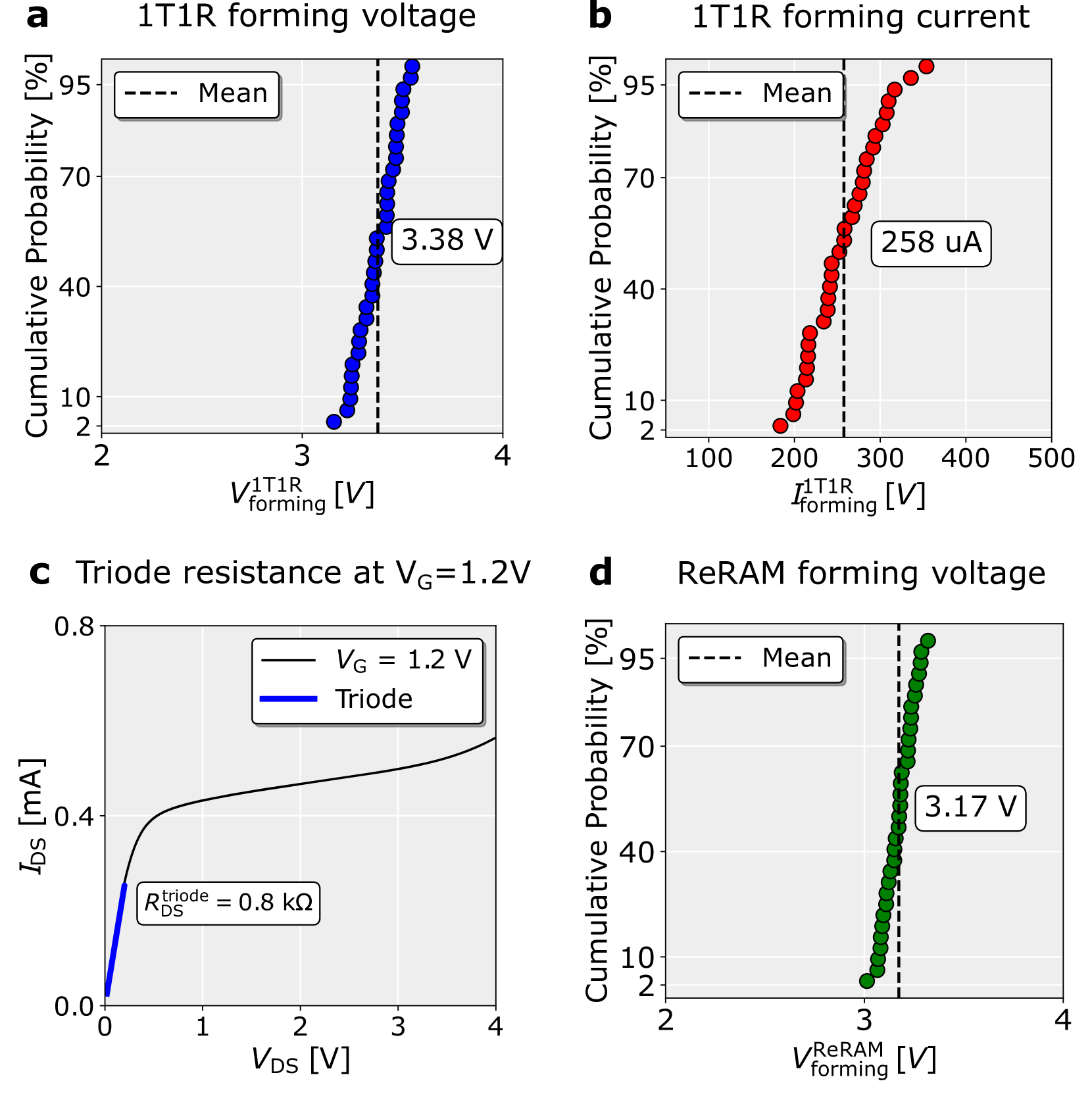

#### 2.1.1 Filament forming

Fig. 2 a shows the current-voltage characteristic of the ReRAM devices in the array, undergoing a soft-dielectric breakdown process, commonly referred to as forming [27]. During this step, a quasi-static voltage sweep up to $\mathrm{3.6\,V}$ is applied to the top electrode of each ReRAM device, while grounding the source and driving the gate of the corresponding NMOS selector with a constant $V_{\mathrm{G}}=\mathrm{1.2\,V}$ ensuring current compliance. This process leads to the formation of a highly defect-rich conductive filament in the HfO x layer. Due to the high oxygen vacancy ( $\rm V_{\rm O}^{\rm\cdot\cdot}$ in Kröger–Vink notation [28]) formation energy, ranging from $\mathrm{2.8\,eV}$ to $\mathrm{4.6\,eV}$ in HfO x depending on the stoichiometry [29, 30], defect generation occurs with statistical relevance only during the forming sweep within the HfO x layer [26]. The subsequent application of a negative voltage sweep up to $-1.4\,\mathrm{V}$ , with a constant $V_{\mathrm{G}}=\mathrm{3.3\,V}$ , induces a radial redistribution of the defects within the CMO layer, consistent with findings in literature [26]. This process leads to an increase of the ReRAM conductance and is modelled by considering a constant average radius of the conductive filament, with a local electrical conductivity increase of the CMO layer on top of the filament. Refer to the ”Methods” section ”ReRAM forming modelling” for details. To determine the experimental ReRAM forming voltage, the voltage drop across the NMOS selector must be subtracted from the voltage applied to the 1T1R cell. Fig. 2 b shows the experimental transistor output characteristic, from which the resistance in the triode region at $V_{\mathrm{G}}=\mathrm{1.2\,V}$ is measured and used to extract the distribution of $V_{\mathrm{forming}}^{\mathrm{ReRAM}}$ within the CMO/HfO x ReRAM array (reported in Fig. 2 c). Refer to the ”Methods” section ”ReRAM forming voltage extraction” for details. The highly reproducible CMO/HfO x ReRAM forming step exhibits a 100% yield with a narrow distribution ( $\sigma=\mathrm{75\,mV}$ ) around $V_{\mathrm{forming}}^{\mathrm{ReRAM}}\approx\mathrm{3.2\,V}$ , making it suitable for integration with $\mathrm{130\,nm}$ NMOS transistors rated for $\mathrm{3.3\,V}$ operation.

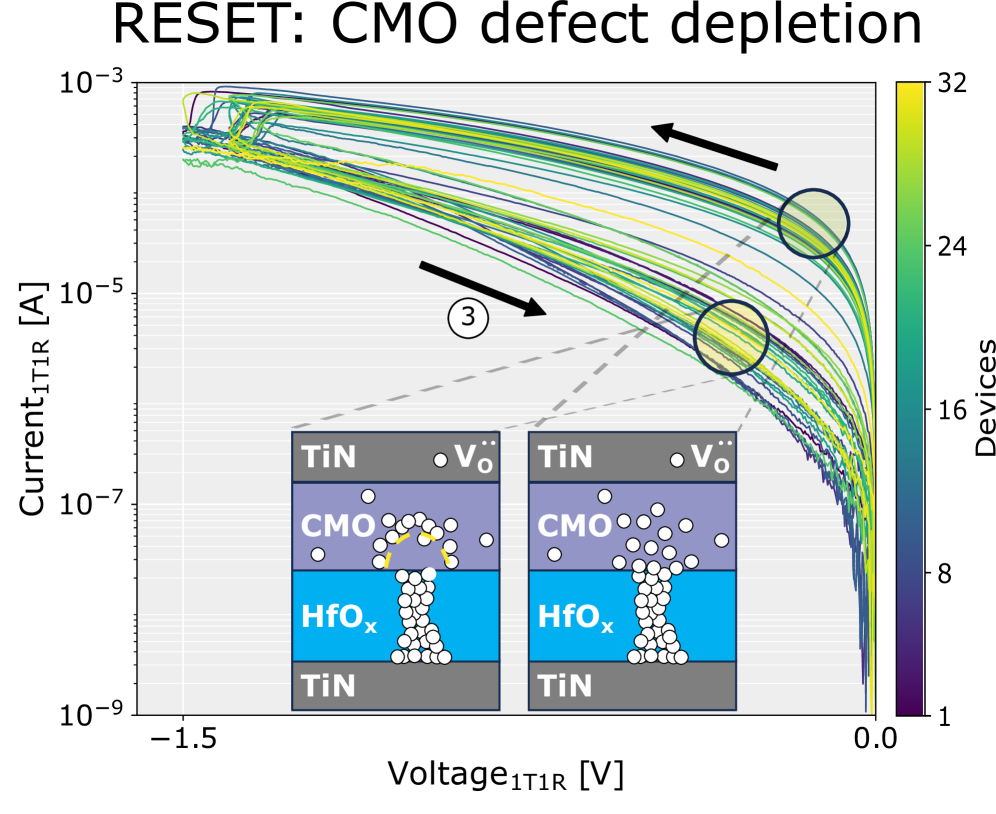

#### 2.1.2 Resistive switching and polarity optimization

The underlying physical mechanism behind the resistive switching in analog CMO/HfO x ReRAM devices has been recently unveiled [26, 31, 32]. The current transport is explained by a trap-to-trap tunneling process, and the resistive switching by a modulation of the defect density within the conductive sub-band of the CMO that behaves as electric field and temperature confinement layer. In these works, the analog CMO/HfO x ReRAM device shows a counter-eightwise (C8W) switching polarity, according to the definition proposed in literature [33]. The intrinsically gradual reset (from low to high resistance) process, marked by a temperature decrease, occurs during the positive voltage sweep on the ReRAM top electrode, while the exponential set (from high to low resistance) process, involving a rapid temperature increase, occurs on the negative side [26]. However, when arranged in a 1T1R cell configuration based on an NMOS selector, the C8W switching polarity prevents direct control of the transistor’s $V_{\mathrm{GS}}$ during the exponential set process. This results in reduced switching uniformity, which is critical for the array-level adoption of analog CMO/HfO x ReRAM devices. For this reason, in this work the analog CMO/HfO x ReRAM devices within the 1T1R cells are optimized to exhibit the desirable 8W switching polarity by extending the current switching model in literature [26]. To achieve this, following the positive forming and the initial negative voltage sweep, each device in the array is subjected to a forward and backward voltage sweep from 0 to $-1.5\,\mathrm{V}$ . During this process, oxygen vacancies in the CMO layer radially spread outward, depleting the CMO defect sub-band within a half-spherical volume at the interface with the conductive filament, leading to a reset process (Fig. S3 in Supplementary Information shows the experimental array’s response). Conversely, a voltage sweep from 0 to $1.3\,\mathrm{V}$ enables the migration of oxygen vacancies in the CMO layer in the reverse direction, resulting in a set transition, controlled by the transistor gate. For each 1T1R cell within the 8x4 array, Fig. 2 d shows 5 quasi-static I-V cycling sweeps to experimentally assess the reproducibility of the optimized 8W switching polarity. The electronic transport in both the low-resistive state (LRS) and high-resistive state (HRS) is modelled as a trap-to-trap tunneling process, described by the Mott and Gurney analytical formulation. The physical parameters characterizing the transport in both LRS and HRS ( $N_{\rm e}$ , $\Delta E_{\rm e}$ , $a_{\rm e}$ , $\sigma_{\rm CMO}$ and $r_{\rm CF}$ ) are shown in Fig. 2 d. Refer to the ”Methods” section ”Analytical ReRAM transport modelling” for details on the LRS and HRS modelling. Fig. 2 e illustrates the cumulative probability distribution of the experimental LRS and HRS within the array, demonstrating device-to-device uniformity and a resistance ratio HRS/LRS of approximately 15, with absolute switching voltages $\leq\mathrm{1.5\,V}$ . The excellent uniformity of the forming and the optimized 8W-cycling characteristics set the groundwork for AIMC-based inference and training AI-accelerators using the CMO/HfO x ReRAM technology.

<details>

<summary>x2.png Details</summary>

### Visual Description

## Composite Technical Diagram: ReRAM Array Characterization

### Overview

The image presents a multi-panel technical analysis of a CMOS/HfOₓ ReRAM array, combining experimental data, modeling, and device characterization. Panels a-e illustrate array forming behavior, transistor characteristics, statistical distributions, and operational states.

---

### Panel a: CMO/HfOₓ ReRAM Array Forming and Modelling

#### Components/Axes

- **Y-axis**: Current₁T1R [A] (log scale: 10⁻⁹ to 10⁻³)

- **X-axis**: Voltage₁T1R [V] (-1.4 to 3.6)

- **Legend**: Two curves with σ_CMO = 37 S/cm (green) and σ_CMO = 5 S/cm (blue), both with r_CF = 11 nm

- **Inset diagrams**: Cross-sectional views of TiN/CMO/HfOₓ/TiN layers with voltage polarity indicators

#### Detailed Analysis

1. **Forming Curves**:

- Two distinct forming curves show current increase during voltage sweep

- Higher σ_CMO (37 S/cm) exhibits steeper current rise (labeled "2" with arrow)

- Lower σ_CMO (5 S/cm) shows gradual transition (labeled "1" with arrow)

2. **Voltage Thresholds**:

- V_G = 1.2 V marked at upper right

- Current thresholds at 10⁻⁵ A and 10⁻⁷ A indicated

#### Key Observations

- Higher conductivity CMO layers enable faster forming transitions

- Both models predict similar final resistance states (r_CF = 11 nm)

---

### Panel b: Transistor Output Characteristic

#### Components/Axes

- **Y-axis**: I_DS [mA] (0 to 3)

- **X-axis**: V_DS [V] (0 to 4)

- **Color gradient**: V_G from 0 V (blue) to 3 V (red)

- **Legend**: Color bar on right with V_G scale

#### Detailed Analysis

- **I-V Curves**:

- All curves show saturation behavior

- Higher V_G (red) corresponds to higher saturation current

- Linear region slope increases with V_G

- **Key Trend**: V_G modulates channel conductivity through gate voltage

---

### Panel c: Array Forming Distribution

#### Components/Axes

- **X-axis**: V_ReRAM_forming [V] (2.8 to 3.4)

- **Y-axis**: Normalized Probability Density (0 to 1)

- **Legend**: Dashed line (theoretical) vs. dots (experimental)

- **Statistical markers**: Mean = 3.17 V, σ = 75 mV

#### Detailed Analysis

- **Distribution Shape**:

- Bell-shaped curve centered at 3.17 V

- Experimental data (dots) align with theoretical prediction

- ±σ range spans 2.995 V to 3.345 V

- **Key Insight**: Forming voltage follows Gaussian distribution with tight variance

---

### Panel d: Array Quasi-Static Cycling and Modelling

#### Components/Axes

- **Y-axis**: Current₁T1R [A] (10⁻⁷ to 10⁻⁴)

- **X-axis**: Voltage₁T1R [V] (-1.5 to 1.3)

- **Legend**: Blue (32 devices) vs. dashed yellow (model)

- **Inset parameters**:

- N_LRS = 5×10¹⁹ cm⁻³, ΔE_LRS = 65 meV

- N_HRS = 1.2×10¹⁸ cm⁻³, ΔE_HRS = 80 meV

#### Detailed Analysis

- **Cycling Behavior**:

- Experimental (blue) shows multi-state switching

- Model (yellow) predicts idealized switching thresholds

- Both show hysteresis loops with similar V_on/V_off

- **Key Difference**: Experimental data exhibits broader current distribution

---

### Panel e: Array HRS-LRS Distributions

#### Components/Axes

- **X-axis**: Resistance [Ω] (10⁴ to 10⁵)

- **Y-axis**: Cumulative Probability (%) (0 to 95)

- **Legend**: Blue dots (HRS) vs. red dots (LRS)

- **Statistical markers**: μ_HRS = 256 kΩ, μ_LRS = 18 kΩ; σ/μ = 0.25 for both

#### Detailed Analysis

- **State Separation**:

- HRS (blue) dominates high-resistance tail (>10⁵ Ω)

- LRS (red) occupies low-resistance region (<10⁴ Ω)

- Clear bimodal distribution with minimal overlap

- **Key Metric**: 95% probability threshold at 10⁵ Ω for HRS

---

### Interpretation

1. **Forming Mechanism**: Higher σ_CMO layers enable faster forming transitions, validated by steeper current rise in panel a

2. **Operational States**: Panel e confirms distinct HRS/LRS states with statistical separation, critical for binary logic applications

3. **Model Validation**: Panel d shows experimental data closely matches theoretical predictions, though real devices exhibit broader current distributions

4. **Voltage Control**: Panel b demonstrates V_G's role in modulating channel conductivity, essential for transistor operation

5. **Manufacturing Consistency**: Panel c's narrow forming voltage distribution (σ = 75 mV) suggests process control maturity

The data collectively demonstrates a mature ReRAM technology with well-defined forming characteristics, stable operational states, and effective voltage control mechanisms. Experimental results closely align with theoretical models, suggesting reliable device performance across multiple fabrication batches.

</details>

Figure 2: ReRAM array quasi-static electrical characterization and modelling. a (1) Experimental positive forming sweeps (with $V_{\mathrm{G}}=\mathrm{1.2\,V}$ ) of the 8x4 CMO/HfO x ReRAM devices in the array. This process results in an average filament radius of $11\,\mathrm{nm}$ in the HfO x layer. (2) Negative voltage sweeps (with $V_{\mathrm{G}}=\mathrm{3.3\,V}$ ) to enable defect redistribution within the CMO layer, resulting in an increase in the conductance of the ReRAM cells. A representative sweep is shown in black. The insets illustrate a schematic representation of the defect arrangement within the stack. b Experimental NMOS transistor output characteristic, with $V_{\mathrm{G}}$ up to $\mathrm{3\,V}$ . c Experimental ReRAM forming voltage distribution measured from the CMO/HfO x ReRAM array. The experimental data used to extract the distribution are represented as green points. d Superposition of 5 I-V quasi-static 8W-cycles (in blue) for each of the 32 devices in the array, using $V_{\mathrm{set}}=\mathrm{1.3\,V}$ , $V_{\mathrm{G}}=\mathrm{1.1\,V}$ and $V_{\mathrm{reset}}=\mathrm{-1.5\,V}$ , $V_{\mathrm{G}}=\mathrm{3.3\,V}$ for set and reset processes, respectively. The analytical trap-to-trap tunneling model effectively captures the electron transport in both the LRS and HRS (yellow dashed lines). The physical parameters characterizing the transport, extracted from the model, and a schematic representation of the defect distribution, are presented for both resistive states. e Cumulative probability distributions for both LRS and HRS. For each array cell, the average resistance over 5 I-V cycles in LRS and HRS is defined at a read voltage of $\mathrm{0.2\,V}$ .

### 2.2 Analog inference with CMO/HfO x ReRAM core

Here, the experimental characterization of the key metrics of the CMO/HfO x ReRAM array relevant to inference performance is presented. Specifically, the continuous conductance tuning capability is demonstrated over a range spanning approximately one order of magnitude. The trade-off between weight transfer programming noise of CMO/HfO x ReRAM devices and number of required iterations for programming convergence is analyzed across different acceptance ranges. Furthermore, conductance relaxation—defined as the change in conductance over time after programming—is characterized. Finally, the combined impact of weight transfer, conductance relaxation, limited input/output quantization of the digital-to-analog converter (DAC) and analog-to-digital converter (ADC), and IR drop on the array wires is evaluated with respect to MVM accuracy.

#### 2.2.1 Weight transfer accuracy

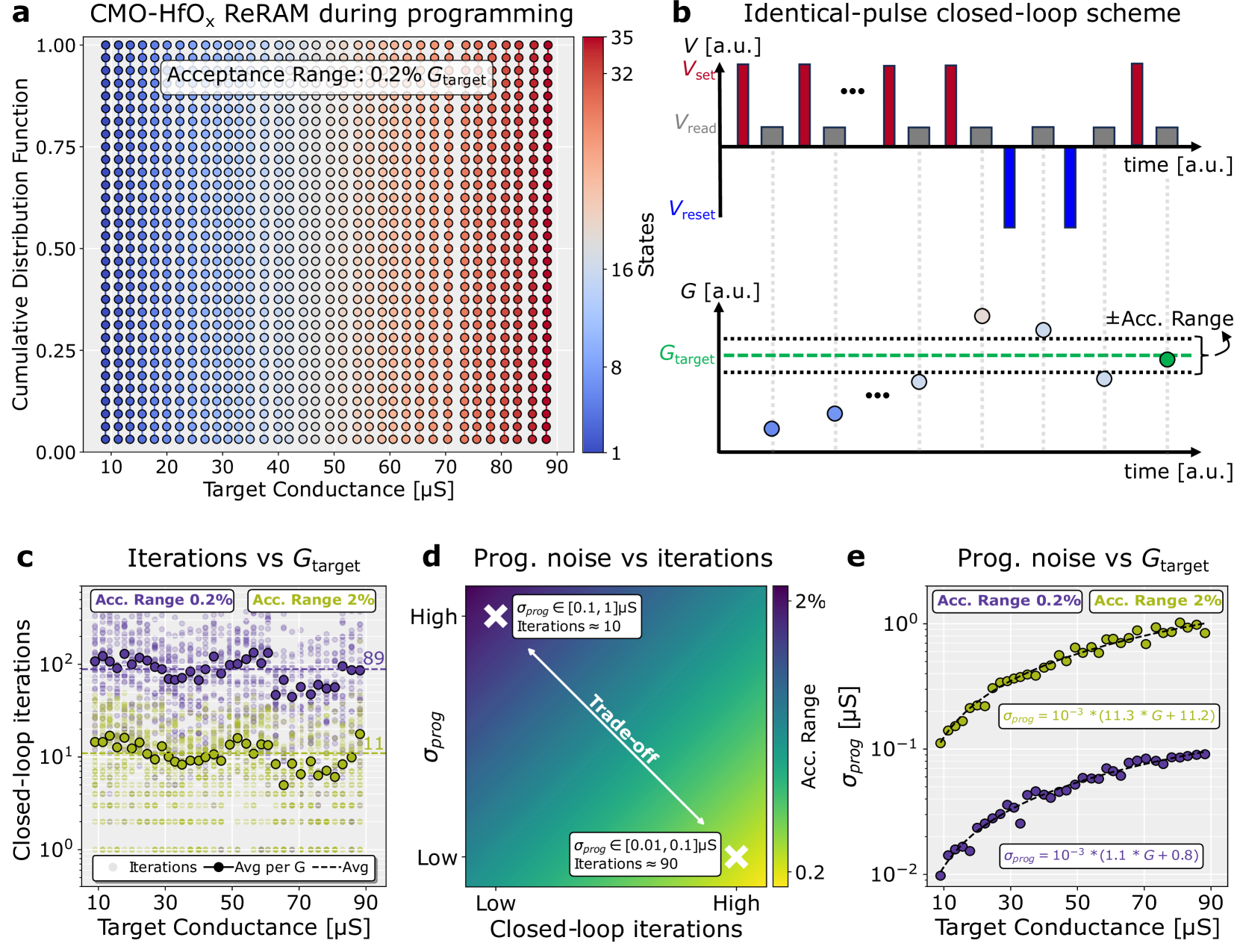

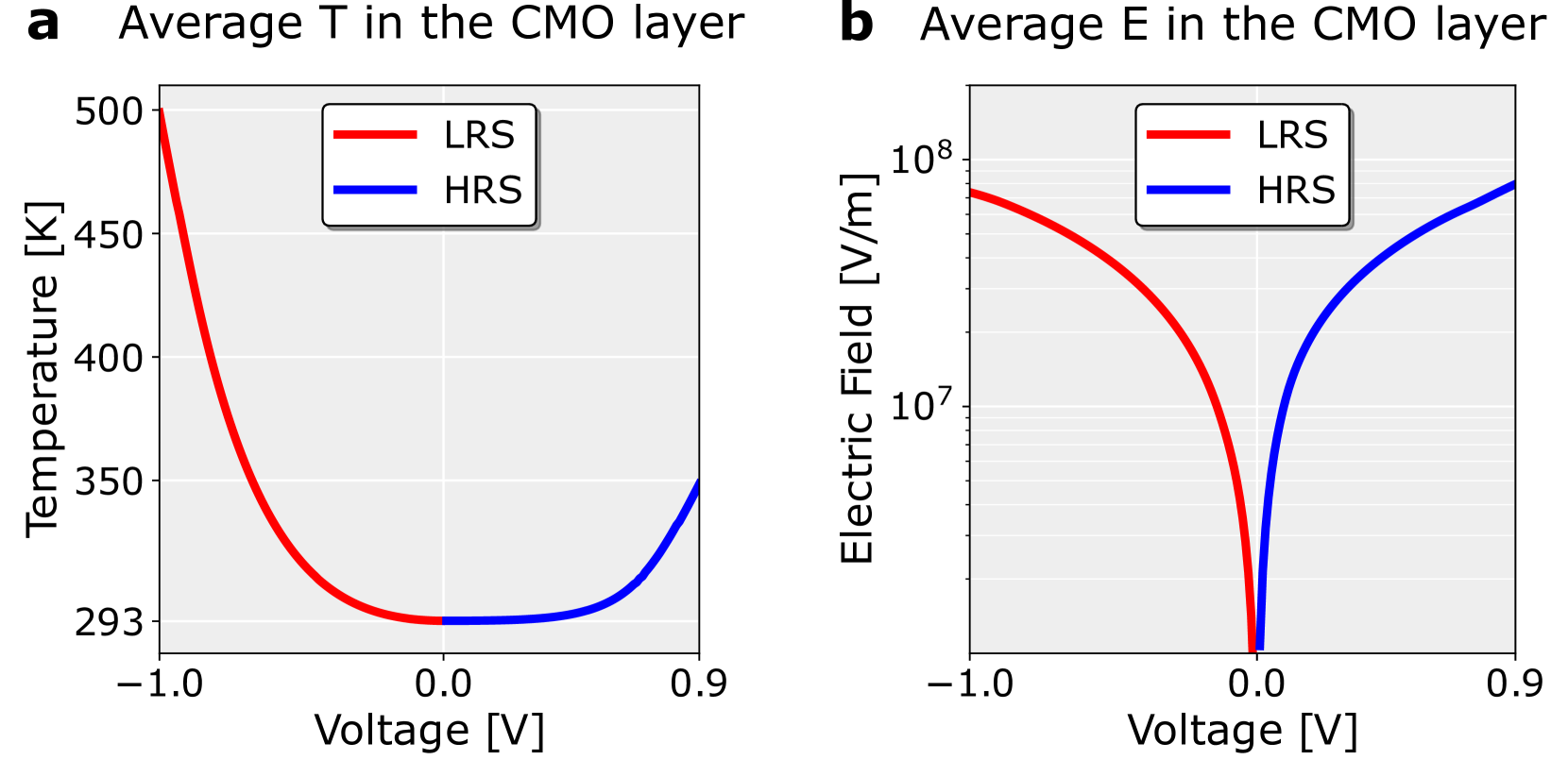

In memristor-based AIMC inference accelerators, pre-trained normalized weights are initially mapped into target conductances and subsequently programmed into hardware in an iterative process known as weight transfer. This iterative process, which stops once the programmed conductance converges to the target value within a defined acceptance range, inherently introduces an error due to the analog nature of conductance weights. This error, described by a normal distribution with the standard deviation referred to as programming noise ( $\sigma_{\rm prog}$ ), leads to a drop in MVM accuracy. To quantify this non-ideality, the non-volatile multi-level capability of the CMO/HfO x ReRAM array is characterized. Fig. 3 a shows the experimental cumulative distribution of conductance values for 35 representative levels, with all states sharply separated and without any overlap. Fig. 3 b shows a schematic representation of the closed-loop (i.e., program-verify) scheme, where identical set and reset pulse trains are employed to program each ReRAM cell to its target conductance within a desired acceptance range (see ”Methods” section ”Identical-pulse closed-loop scheme” for details). Selecting programming conditions involves a fundamental trade-off: a narrower acceptance range can improve programming precision by reducing programming noise, but it increases the number of iterations required for convergence (see Fig. 3 d). Besides the longer programming time, other non-idealities to consider when choosing the acceptance range are (1) the conductance relaxation immediately after programming, which is characterized in 2.2.2 for CMO/HfO x ReRAM devices, and (2) read noise, which has already been characterized between 0.2% and 2% of G target for CMO/HfO x ReRAM devices [25] within a similar conductance range used in this work. The trade-off between the programming noise and the number of iterations is characterized for two representative acceptance range intervals: 0.2% and 2% of G target, respectively. Fig. 3 c illustrates the experimental number of pulses needed to converge to the G target using the two representative acceptance ranges. On average, each cell requires approximately 11 and 89 set / reset pulses for acceptance ranges of 2% and 0.2% of G target, respectively. Since the acceptance range is defined as a percentage of G target, the number of iterations required for convergence is almost independent of the target conductance value. In the Supplementary Information, Fig. S5 a shows the experimental cumulative distribution of conductance values for the same 35 representative levels presented in Fig. 3 a, but using 2% G target as acceptance range. The standard deviation of the representative conductance levels is extracted and fitted as a linear function of the target conductance (dashed lines), as shown in Fig. 3 e, for both acceptance ranges. For all conductance levels, a standard deviation of less than 0.1 µS (1 µS) is achieved considering 0.2% G target (2% G target) as the acceptance range. This is more than one order of magnitude lower compared to other memristive technologies, such as phase-change memory (PCM) arrays, targeting similar conductance ranges [34, 35, 36]. These results demonstrate that CMO/HfO x ReRAM cells achieve an almost ideal weight transfer during programming, enabling the distinction of more than 32 states (5 bits).

<details>

<summary>x3.png Details</summary>

### Visual Description

## Heatmap: CMO-HfOₓ ReRAM during programming

### Overview

A heatmap visualizing the cumulative distribution function (CDF) of target conductance values during ReRAM programming. The color gradient represents the density of data points, with blue indicating lower values and red higher values.

### Components/Axes

- **X-axis**: Target Conductance [μS] (10–90 μS)

- **Y-axis**: Cumulative Distribution Function (0.00–1.00)

- **Color Scale**: Blue (low density) to Red (high density)

- **Legend**: "Acceptance Range: 0.2% G_target" (annotated in the top-left region)

### Detailed Analysis

- The heatmap shows a gradient from blue (left) to red (right), indicating increasing conductance values.

- The acceptance range (0.2% G_target) is highlighted in the upper-left quadrant, where data points cluster densely.

- No explicit numerical values are provided, but the color intensity suggests higher conductance values (e.g., >70 μS) dominate the red regions.

### Key Observations

- Conductance values below 30 μS are underrepresented (blue regions).

- The acceptance range annotation implies a focus on conductance values near the target threshold.

### Interpretation

The heatmap demonstrates the distribution of target conductance during ReRAM programming, with a concentration of data points near the 0.2% acceptance range. This suggests variability in programming outcomes, particularly at lower conductance values.

---

## Diagram: Identical-pulse closed-loop scheme

### Overview

A schematic of a closed-loop programming process for ReRAM, showing voltage pulses and conductance measurements over time.

### Components/Axes

- **X-axis**: Time [a.u.] (sequential steps)

- **Y-axis**: Voltage States (V_set, V_read, V_reset) and Conductance (G)

- **Key Elements**:

- Red bars: V_set pulses

- Gray bars: V_read measurements

- Blue bars: V_reset pulses

- Green dashed line: G_target threshold

- Acceptance range: ±0.2% G_target (annotated with arrows)

### Detailed Analysis

- The process alternates between V_set (programming), V_read (measurement), and V_reset (reset).

- Conductance (G) is measured after each V_read, with deviations from G_target marked by the acceptance range.

- The green dashed line (G_target) acts as a reference for successful programming.

### Key Observations

- Conductance measurements (G) are tightly controlled within ±0.2% of G_target.

- V_set pulses are consistently applied to adjust conductance toward G_target.

### Interpretation

This closed-loop scheme ensures precise control of ReRAM conductance by iteratively adjusting voltage pulses and measuring deviations from the target. The acceptance range indicates tolerance for minor variations.

---

## Scatter Plot: Iterations vs G_target

### Overview

A log-scale plot comparing closed-loop iterations to target conductance (G_target) for two acceptance ranges (0.2% and 2%).

### Components/Axes

- **X-axis**: Target Conductance [μS] (10–90 μS)

- **Y-axis**: Closed-loop Iterations (10⁰–10²)

- **Legend**:

- Purple: Acceptance Range 0.2%

- Green: Acceptance Range 2%

- Black dashed line: Average iterations per G_target

### Detailed Analysis

- **0.2% Acceptance Range (Purple)**:

- Iterations increase with G_target, peaking at ~100 iterations for G_target ≈ 80 μS.

- Data points cluster densely between 10–50 μS.

- **2% Acceptance Range (Green)**:

- Fewer iterations required (1–10 iterations) across all G_target values.

- Data points are sparser but show a general upward trend.

### Key Observations

- Tighter acceptance ranges (0.2%) require significantly more iterations, especially at higher G_target values.

- The average iterations per G_target (black dashed line) suggests a logarithmic relationship.

### Interpretation

Higher precision (0.2% acceptance) demands more iterations, highlighting the trade-off between accuracy and computational effort in ReRAM programming.

---

## Heatmap: Prog. noise vs iterations

### Overview

A heatmap showing the relationship between programming noise (σ_prog) and closed-loop iterations, with color gradients indicating acceptance ranges.

### Components/Axes

- **X-axis**: Closed-loop Iterations (Low to High)

- **Y-axis**: Programming Noise (σ_prog) [μS]

- **Color Scale**: Blue (low σ_prog) to Yellow (high σ_prog)

- **Annotations**:

- "Trade-off: σ_prog ∈ [0.01, 0.1] μS, Iterations ≈ 90"

- "σ_prog ∈ [0.1, 1] μS, Iterations ≈ 10"

### Detailed Analysis

- Lower σ_prog (blue regions) correlates with higher iterations (right side of the plot).

- Higher σ_prog (yellow regions) aligns with fewer iterations.

- The "trade-off" annotation emphasizes the inverse relationship between noise and iterations.

### Key Observations

- σ_prog values below 0.1 μS require ~90 iterations, while values above 0.1 μS drop to ~10 iterations.

- The acceptance range is not explicitly labeled but inferred from color intensity.

### Interpretation

Reducing programming noise improves precision but increases the number of iterations needed, reflecting a critical balance in ReRAM optimization.

---

## Scatter Plot: Prog. noise vs G_target

### Overview

A log-scale plot of programming noise (σ_prog) against target conductance (G_target), with two acceptance ranges (0.2% and 2%).

### Components/Axes

- **X-axis**: Target Conductance [μS] (10–90 μS)

- **Y-axis**: Programming Noise (σ_prog) [μS] (10⁻²–10⁰)

- **Legend**:

- Purple: Acceptance Range 0.2%

- Green: Acceptance Range 2%

- **Equations**:

- σ_prog = 10⁻³*(11.3*G + 11.2) (0.2% range)

- σ_prog = 10⁻³*(1.1*G + 0.8) (2% range)

### Detailed Analysis

- **0.2% Acceptance Range (Purple)**:

- σ_prog increases linearly with G_target (slope ≈ 11.3*10⁻³).

- Data points form a tight curve from ~0.1 μS (G=10 μS) to ~1.2 μS (G=90 μS).

- **2% Acceptance Range (Green)**:

- σ_prog increases more slowly (slope ≈ 1.1*10⁻³).

- Data points range from ~0.08 μS (G=10 μS) to ~1.0 μS (G=90 μS).

### Key Observations

- Tighter acceptance ranges (0.2%) exhibit higher σ_prog, especially at higher G_target values.

- The 2% range shows a flatter trend, indicating lower noise tolerance.

### Interpretation

Programming noise scales with target conductance, with stricter acceptance ranges amplifying noise effects. This underscores the challenge of maintaining precision in high-conductance ReRAM devices.

</details>

Figure 3: Weight transfer characterization. a Cumulative distributions of 35 conductance states obtained using an identical-pulse closed-loop scheme with a 0.2% G target acceptance range. For each distribution, the entire CMO/HfO x ReRAM array was programmed to the corresponding G target, and the conductance values measured during the final closed-loop iteration (during programming) is reported. Each dot represents a 1T1R cell. b An example sequence of the identical-pulse closed-loop programming scheme utilized in this work. c Experimental number of closed-loop iterations as a function of G target for the two representative acceptance ranges. Each semitransparent point represents a 1T1R cell, the opaque points represent the average number of iterations per G target, and the horizontal dashed line indicates the overall average of the opaque points. d Graphical representation of the trade-off between programming noise and the number of iterations required for convergence, as a function of the acceptance range. e Experimental programming noise as a function of G target for the two representative acceptance ranges. Each point represents the standard deviation of the normal distribution measured across the entire array. The dashed lines in black indicate the corresponding linear fits.

#### 2.2.2 Conductance relaxation and matrix-vector multiplication accuracy

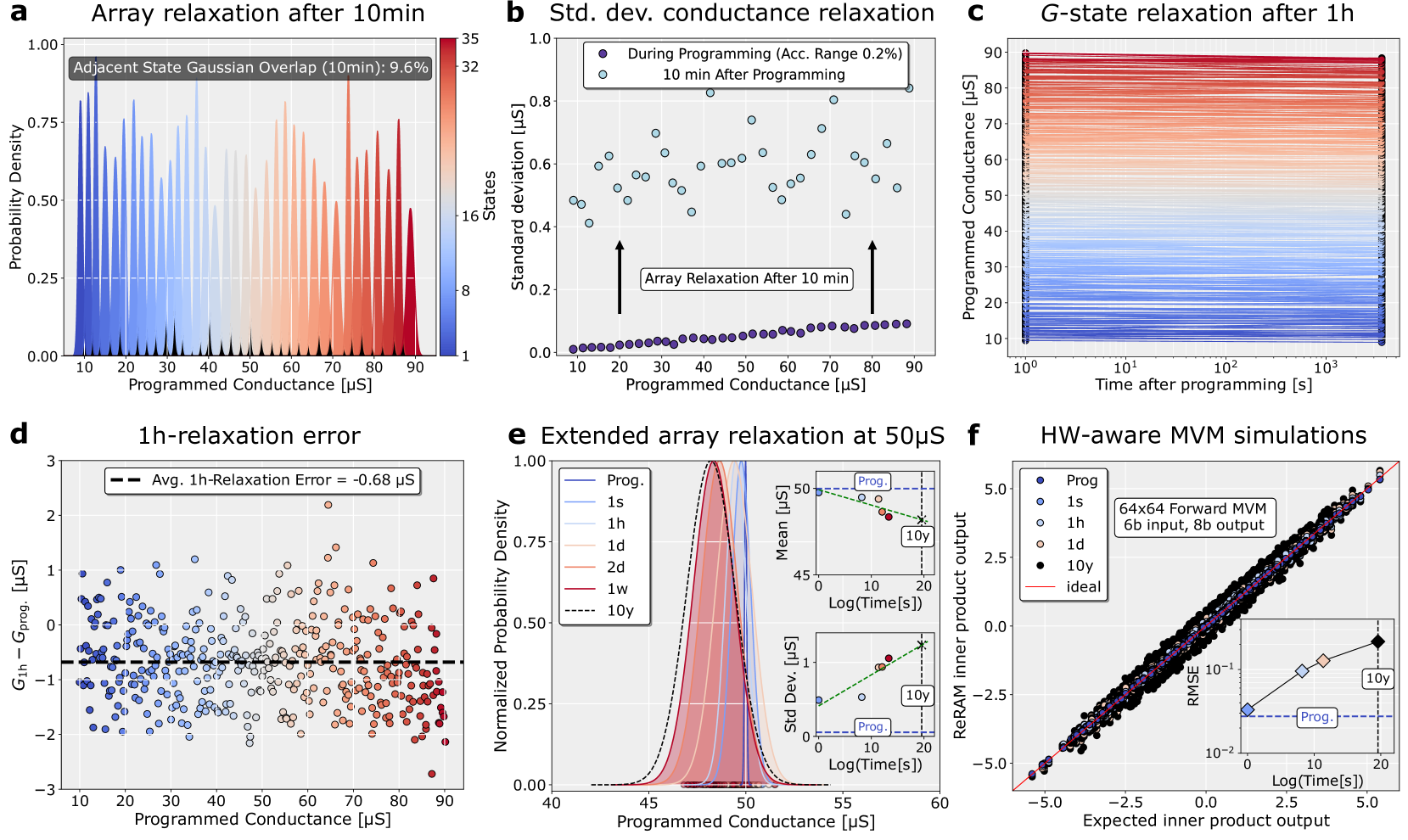

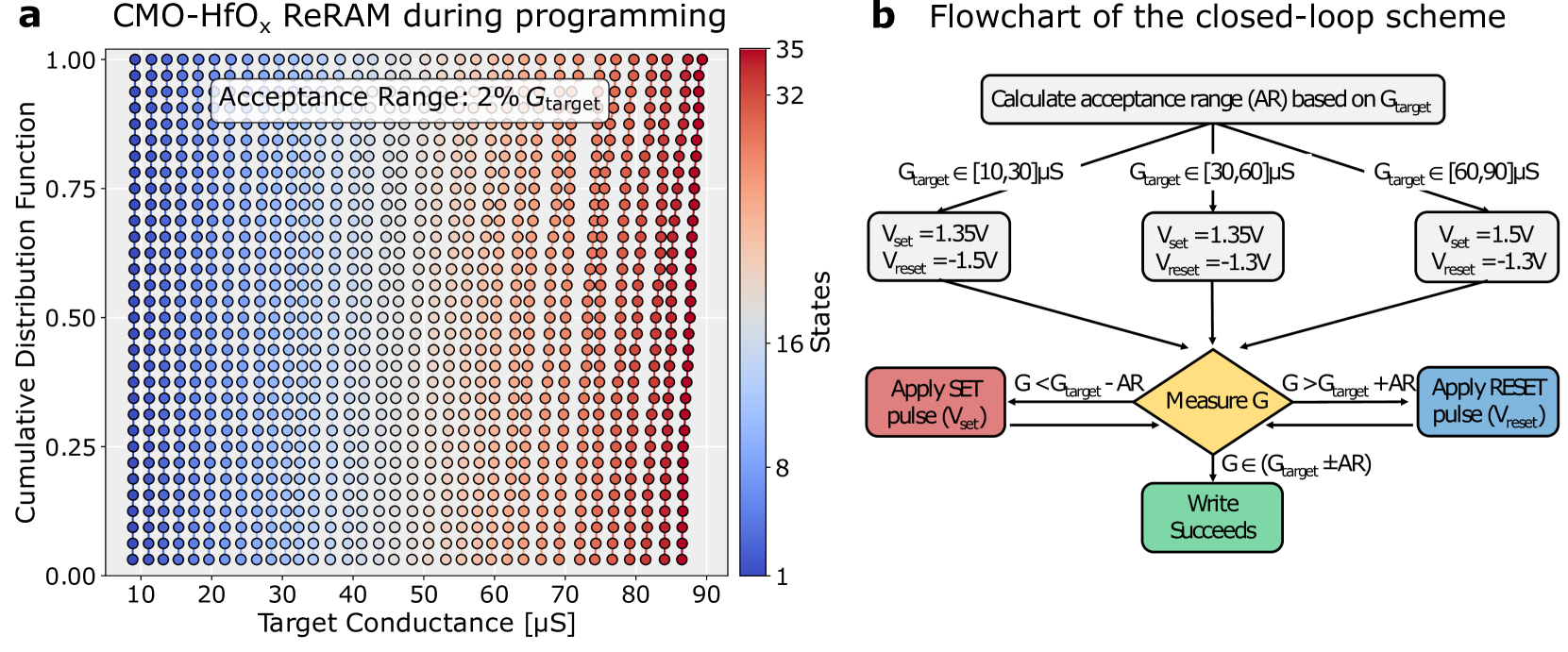

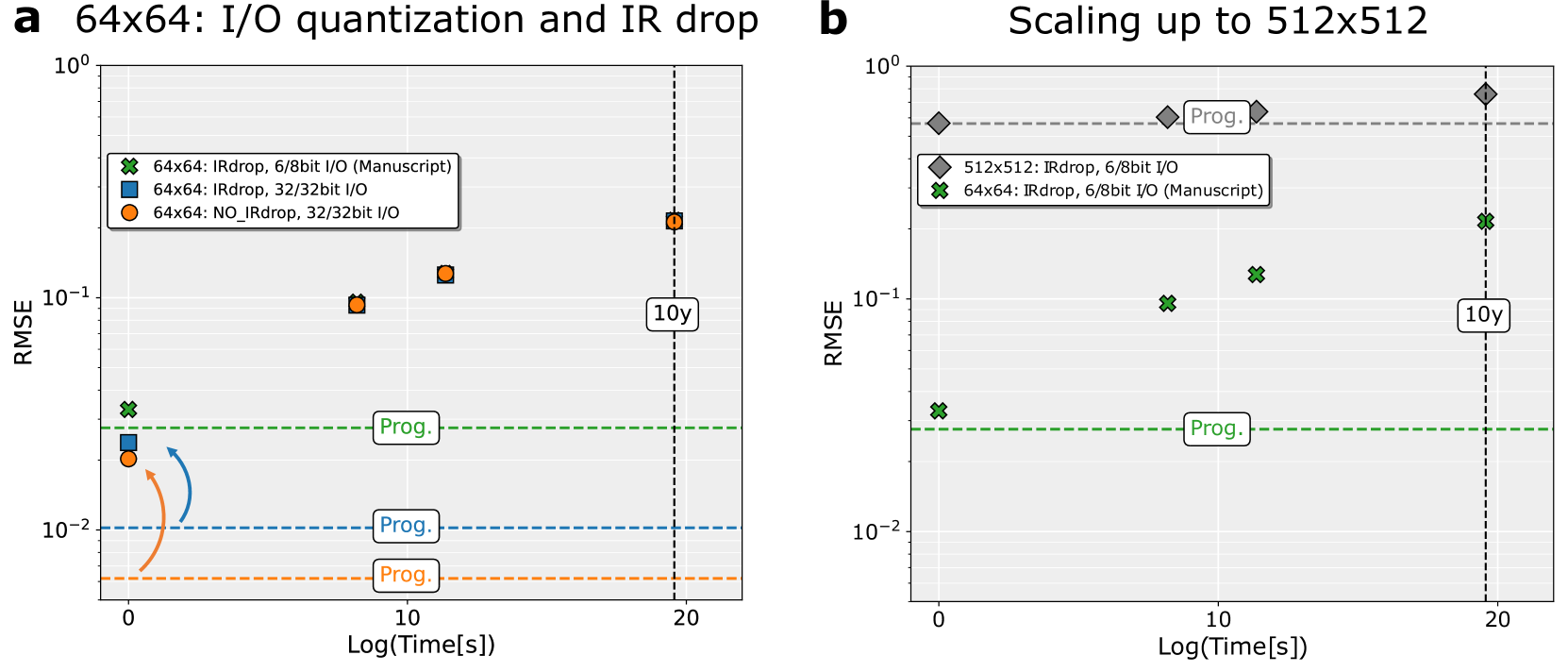

In addition to the excellent weight transfer accuracy during programming as presented in the previous section, the characterization of temporal conductance relaxation is critical to estimate the MVM accuracy over time. In analog ReRAM devices, a significant conductance relaxation has been observed immediately after programming (within 1 second) [9]. Following this initial abrupt conductance change, the relaxation process slows considerably [37, 9]. The physical cause of retention degradation is attributed to the Brownian motion of defects in the resistive switching layer [37]. In this section, the conductance relaxation of the CMO/HfO x ReRAM array after programming is characterized. Fig. 4 a shows the relaxation of the distributions previously reported in Fig. 3 a, approximately 10 minutes after programming. The 35 levels remain distinguishable 10 minutes after programming, with an average overlap of 9.6% between adjacent states gaussians, while the average standard deviation of the distributions increases to 0.6 µS, showing almost independence from the G target (see Fig. 4 b). The stability of the CMO/HfO x ReRAM conductance states is further assessed on a longer time-scale, up to 1 hour. To achieve so, a linearly spaced G target vector within the experimental conductance range of 10 µS to 90 µS is defined, with a fine step of 0.2 µS (400 points). Each G target value is programmed into a single ReRAM device within the array. Due to the size mismatch between the array (32 devices) and the G target vector (size 400), multiple measurement batches are needed. Fig. 4 c shows the experimental relaxation of the 400 programmed states within the entire conductance window, 1 second and 1 hour after programming, executed with the closed-loop scheme (see ”Methods” section ”Identical-pulse closed-loop scheme” for details) and with a 0.2% G target acceptance range. The exhibited conductance error induced by the relaxation process after 1 hour, computed as $G_{\mathrm{1h}}-G_{\mathrm{prog.}}$ , is plotted as a function of the programmed conductances in Fig. 4 d. After 1 hour, although both positive and negative relaxation errors are recorded, an average decrease in conductance is observed across all programmed states, with a relaxation error averaging around -0.7 µS. This highlights that the relaxation process in CMO/HfO x ReRAM devices leads, on average, to a decrease in the mean and an increase in the standard deviation of the Gaussian distributions regardless of the initial conductance state. Since the absolute magnitudes of the mean decrease and the standard deviation increase are independent of G target, an extended characterization of the relaxation process up to 1 week is conducted for a representative conductance state (50 µS). To achieve this, the array’s CMO/HfO x ReRAM devices are programmed using the identical-pulse closed-loop scheme to G target of 50 µS, with a 0.2% G target acceptance range. Fig. 4 e illustrates the experimental array relaxation over 1 week. The insets display the evolution of both the mean and standard deviation as a function of the logarithm of time after programming (in seconds), using a linear fit to predict the conductance distribution over a 10-year period. To assess the accuracy of analog MVM, a comprehensive set of non-idealities—both intrinsic to CMO/HfO x ReRAM devices and at the architecture level—is considered, including finite programming resolution with 0.2% G target acceptance range, conductance relaxation, limited ADC and DAC quantization, and IR-drop across array wires. Fig. 4 f shows the hardware-aware simulation results of the analog MVM using CMO/HfO x ReRAM cells, projected for up to 10 years from programming, compared to the expected floating-point (FP) result. The results are generated using a single 64×64 normally distributed random weight matrix and 100 normally distributed input vectors within the range [-1, 1] (see ”Methods” section ”HW-aware simulation of analog MVM” for details). Considering the input and output quantization of 6-bit and 8-bit respectively, the inset illustrates the time evolution of the root-mean-square error (RMSE) of the simulated analog MVM compared to the FP expected result. These results show that the CMO/HfO x ReRAM core enables accurate MVM operations, achieving an RMSE ranging from 0.03 at 1 second to 0.2 at 10 years after programming, compared to the ideal FP case. Fig. S6 in the Supplementary Information illustrates the impact of IR-drop and input/output quantization on the RMSE of an MVM performed on a 64×64 array. Over short time scales (within 1 hour), the primary accuracy bottleneck is the limited input/output quantization of 6-bit and 8-bit, respectively. Over longer periods, relaxation effects become the dominant source of non-ideality. In a larger 512×512 array, IR-drop emerges as the main accuracy bottleneck for analog MVM. Compared to the analog ReRAMs studied by Wan et al. [9], who report an experimentally determined RMSE of approximately 0.58 under conditions similar to those of this work, CMO/HfO x ReRAMs demonstrate a potential improvement in MVM accuracy by a factor of 20 and 3, 1 second and 10 years after programming, respectively. The excellent MVM accuracy results demonstrate the suitability of CMO/HfO x ReRAM devices for long-term AI inference applications, and lay the foundation for AI training acceleration, where short-term forward and backward MVMs are key steps.

<details>

<summary>x4.png Details</summary>

### Visual Description

## Array Relaxation and Conductance Analysis

### Overview

The image presents six panels (a-f) analyzing array relaxation dynamics, conductance stability, and simulation accuracy in resistive memory devices. Panels a-e focus on experimental data, while panel f presents simulation results. Key themes include temporal relaxation behavior, error quantification, and long-term stability.

### Components/Axes

**Panel a**:

- **X-axis**: Programmed Conductance [µS] (10-90 µS)

- **Y-axis**: Probability Density (0-1.0)

- **Legend**: Adjacent State Gaussian Overlap (10min): 9.6%

- **Color Gradient**: Blue (low) → Red (high) probability density

**Panel b**:

- **X-axis**: Programmed Conductance [µS] (10-90 µS)

- **Y-axis**: Standard Deviation [µS] (0-1.0)

- **Markers**:

- Purple circles: During Programming (Acc. Range 0.2%)

- Green circles: 10 min After Programming

- **Annotations**: Arrows labeled "Array Relaxation After 10 min"

**Panel c**:

- **X-axis**: Time after Programming [s] (log scale: 10⁰-10³)

- **Y-axis**: Programmed Conductance [µS] (10-90 µS)

- **Color Gradient**: Red (high G-state) → Blue (low G-state)

**Panel d**:

- **X-axis**: Programmed Conductance [µS] (10-90 µS)

- **Y-axis**: 1h-Relaxation Error [G₁h - G_prog] [µS] (-3 to +3)

- **Trendline**: Dashed black line (Avg. Error = -0.68 µS)

**Panel e**:

- **X-axis**: Programmed Conductance [µS] (40-60 µS)

- **Y-axis**: Normalized Probability Density (0-1.0)

- **Legend**: Time Intervals (1s, 1h, 1d, 1w, 10y)

- **Inset Graphs**:

- Top: Mean vs. Log(Time) [10y marker at 45 µS]

- Bottom: Std. Dev. vs. Log(Time) [10y marker at 55 µS]

**Panel f**:

- **X-axis**: Expected Inner Product Output (-5 to +5)

- **Y-axis**: ReRAM Inner Product Output (-5 to +5)

- **Markers**:

- Purple circles: Program (Prog)

- Blue squares: 1s

- Green diamonds: 1h

- Red triangles: 10y

- **Trendline**: Red dashed line (Ideal 1:1 correlation)

- **Inset Graph**: RMSE vs. Log(Time) [10y marker at 10⁻¹ RMSE]

### Detailed Analysis

**Panel a**:

- Probability density peaks at ~45 µS (blue) and ~75 µS (red), indicating bimodal distribution.

- Adjacent state overlap (9.6%) suggests partial conductance state interference.

**Panel b**:

- Standard deviation decreases by ~0.4 µS after 10 min (green markers vs. purple).

- Lower conductance states (<30 µS) show larger relaxation effects.

**Panel c**:

- G-state relaxation follows exponential decay:

- 90 µS → 70 µS in 1s

- Stabilizes near 50 µS after 1h.

**Panel d**:

- Negative average error (-0.68 µS) indicates systematic underestimation of G₁h.

- Errors cluster around ±1 µS for mid-range conductances (40-60 µS).

**Panel e**:

- Conductance stabilizes at ~50 µS after 10y (dashed black line).

- Insets show:

- Mean shifts from 45 µS (1s) to 55 µS (10y)

- Std. Dev. decreases from 5 µS (1s) to 2 µS (10y)

**Panel f**:

- Strong linear correlation (R² > 0.95) between expected and observed outputs.

- 10y data points deviate by <0.5 units from ideal line.

- RMSE improves from 0.1 (1s) to 0.01 (10y).

### Key Observations

1. **Temporal Relaxation**: Conductance states relax toward ~50 µS across all time scales (panels a, c, e).

2. **Error Patterns**: Systematic underestimation (-0.68 µS avg.) suggests calibration requirements (panel d).

3. **Simulation Accuracy**: MVM models achieve <1% error after 10y (panel f).

4. **Bimodal Distribution**: Two dominant conductance states emerge post-programming (panel a).

### Interpretation

The data demonstrates that resistive memory arrays exhibit predictable relaxation toward a stable conductance state (~50 µS) over time, with errors decreasing systematically in simulations. The 9.6% adjacent state overlap (panel a) and -0.68 µS average error (panel d) highlight the need for error-correction mechanisms in multi-state devices. The MVM simulations (panel f) validate the physical model's accuracy, showing <1% deviation after long-term operation. These findings suggest that array relaxation is both time-dependent and conductance-range specific, with implications for multi-bit storage architectures.

</details>

Figure 4: Conductance relaxation and MVM accuracy. a Probability density distributions of 35 conductance states approximately 10 minutes after programming. The black areas between adjacent Gaussian distributions represent the overlap of their tails. On average, an overlap of 9.6% is observed after 10 minutes. b The standard deviations of the 35 conductance states during programming (in purple) and 10 minutes after it (light blue). c Relaxation of 400 conductance states, with one device per G-state, measured 1 second and 1 hour after programming. d Relaxation error 1 hour after programming. A negative and nearly G-independent average error (dashed line) indicates that relaxation in CMO/HfO x ReRAMs tends toward a slight conductance decrease and is state-independent. e Experimental array relaxation of a representative 50 µS state, up to 1 week after programming with 0.2% G target acceptance range. Each probability density distribution is normalized to its maximum for graphical representation. The experimental data used to extract the distributions are represented as points aligned to the y=0 horizontal axis. Insets show the time dependence of the mean and standard deviation. Dashed blue lines represent the conditions during programming, once the convergence to G target is reached, while a linear fit (green dashed line) extrapolates the distribution 10 years after programming (dashed black line). f Analog MVM accuracy simulations using a 64x64 CMO/HfO x ReRAM array as a function of time after programming (indicated by different colors). The inset shows the expected RMSE compared to the ideal FP result. Experimental programming noise, conductance relaxation, limited input/output quantization and IR-drop are considered in this assessment.

### 2.3 Analog training with CMO/HfO x ReRAM core

To efficiently tackle deep learning workloads, the analog AI accelerator must not only perform forward and backward passes (MVMs), but most importantly, allow for weight updates [38]. During backpropagation, the synaptic weights are modified according to the gradient of the corresponding layer. Therefore, the device conductance must be gradually modified in both positive and negative directions to represent analog weight changes. Analog CMO/HfO x ReRAM arrays not only allow for bidirectional conductance updates, but additionally enable parallel weight updating by following a stochastic open-loop pulse scheme [20, 21]. Remarkably, the parallel and open-loop update scheme significantly accelerates training compared to serial and closed-loop methods, providing efficiency gains of several orders of magnitude and advantages in system design complexity [39]. In this section, the bidirectional open-loop response of the CMO/HfO x ReRAM array, required during Tiki-Taka training, is characterized. Specifically, the analog conductance potentiation, depression and symmetry point are measured. Subsequently, the devices’ responses are statistically reproduced in the open-source ’aihwkit’ simulation platform developed by IBM [38]. Finally, this hardware-aware device model, which includes device variabilities, is used to simulate the training of representative neural networks using the AGAD learning algorithm. This novel analog training algorithm relaxes the symmetry requirements of previous Tiki-Taka versions by incorporating additional digital computations on-the-fly [23].

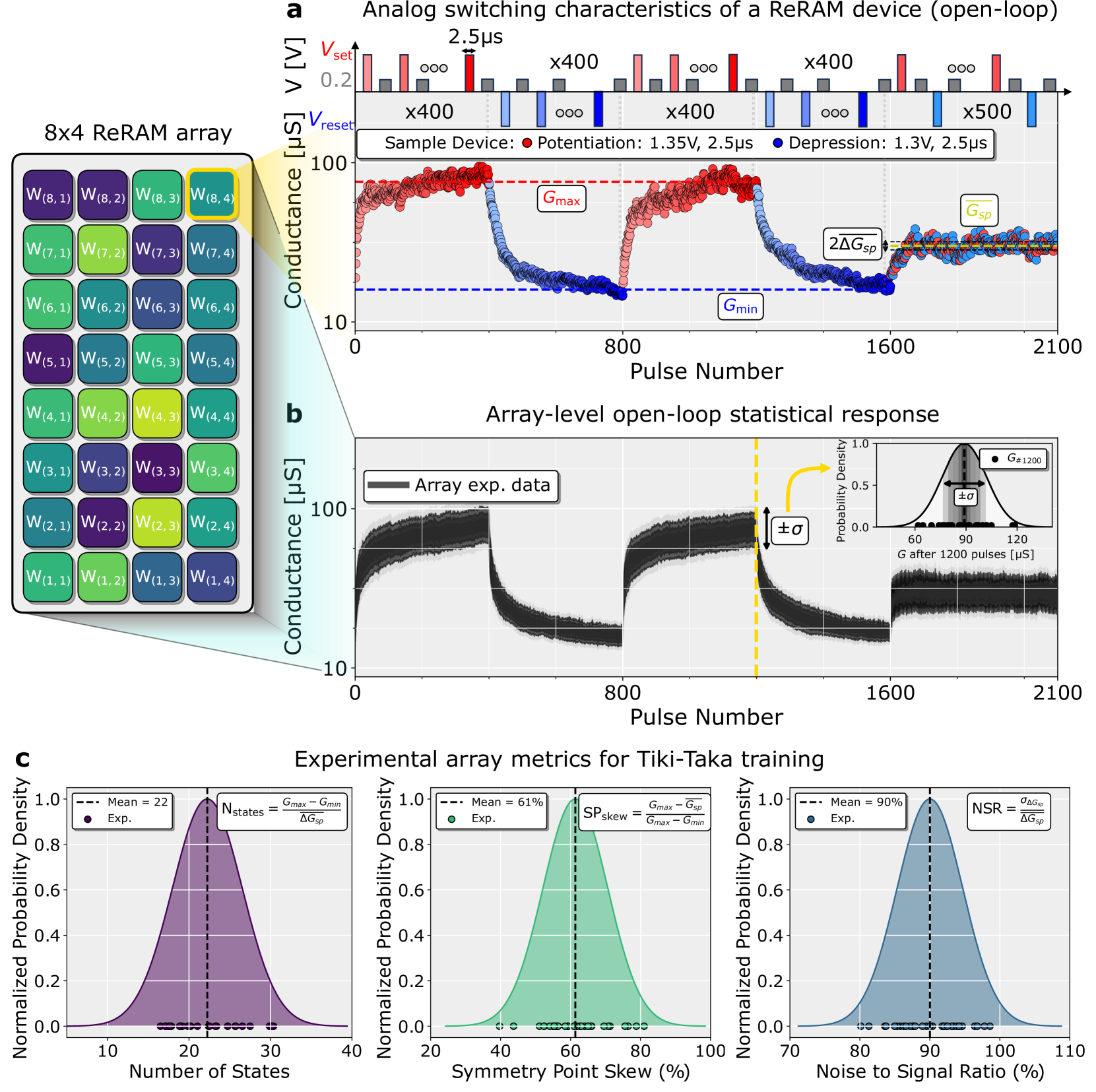

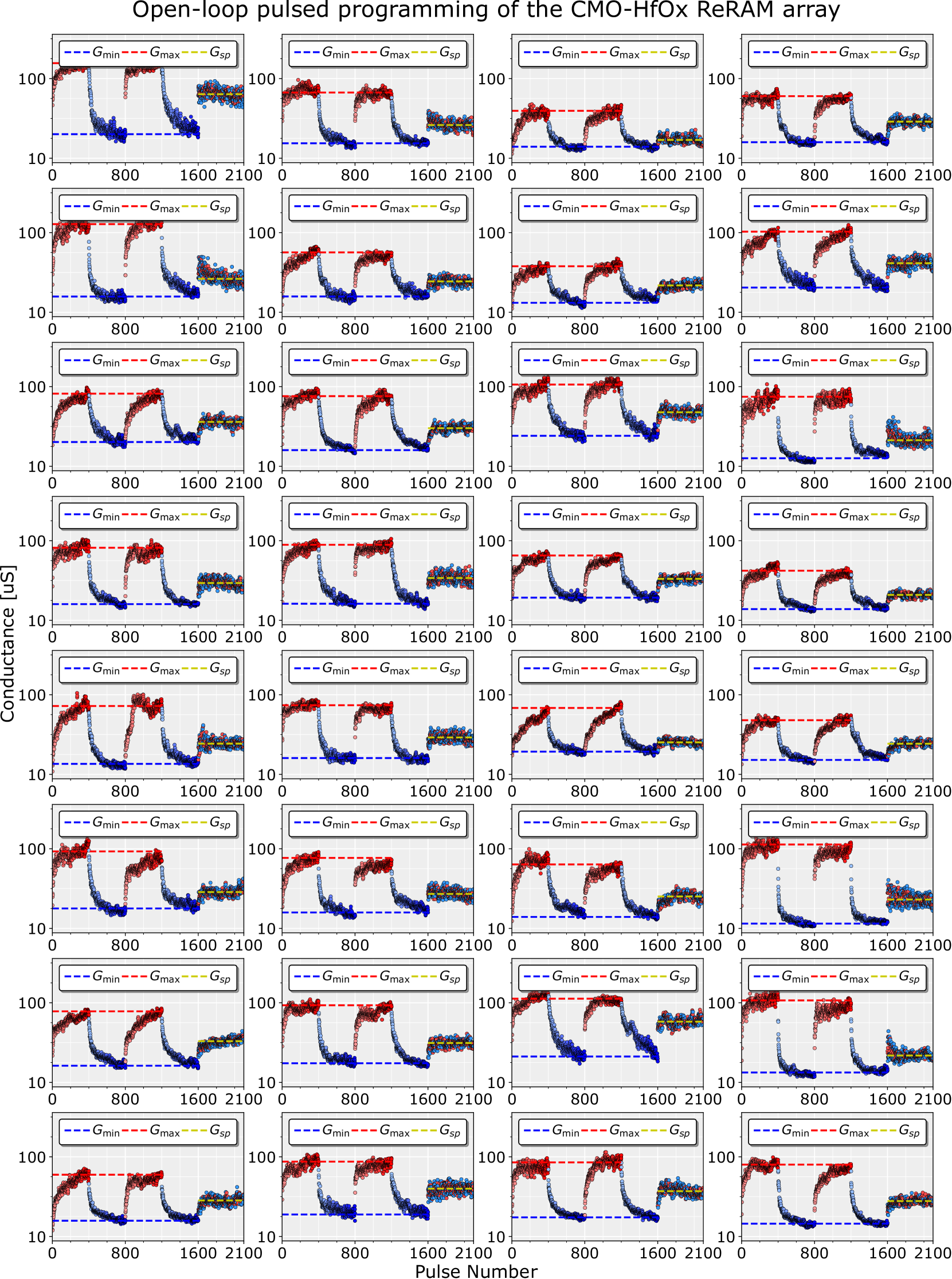

#### 2.3.1 Open-loop ReRAM array characterization

Fig. 5 a shows the experimental conductance change of a representative CMO/HfO x ReRAM device within the array upon applying identical-voltage pulse trains with alternating polarity in batches of 400. Subsequently, a sequence of 500 pulses with alternating polarity, consisting of 1-pulse-up followed by 1-pulse-down, is applied to experimentally determine the symmetry point. The same open-loop programming scheme, with $V_{\rm set}=1.35\,\mathrm{V}$ ( $V_{\rm G}=1.4\,\mathrm{V}$ ) and $V_{\rm reset}=-1.3\,\mathrm{V}$ ( $V_{\rm G}=3.3\,\mathrm{V}$ ), each lasting 2.5 µs, is applied to all devices in the 8x4 array. The set / reset pulse width is limited by the experimental setup, although previous work has demonstrated CMO/HfO x ReRAM switching with pulses as short as $60\,\mathrm{ns}$ [25]. Due to inter-device (device-to-device) and intra-device (cycle-to-cycle) variabilities, the experimental response of each device to a given number of identical pulses exhibits some level of variability (see Fig. S7 in the Supplementary Information). Therefore, for each pulse, a Gaussian distribution of the measured conductance states among the devices is extracted. For statistical relevance, Fig. 5 b shows the experimental standard deviation of the array response to the open-loop scheme as a function of the pulse number, represented in grey. To realistically assess the accuracy of analog training with CMO/HfO x ReRAM devices, the key figures of merit of the device training characterization—such as the number of states, the symmetry point skew, and the noise-to-signal ratio (NSR)—are first extracted from experimental data, as defined below.

$$

\displaystyle\mathrm{N}_{\rm states}=\frac{G_{\rm max}-G_{\rm min}}{\overline{

\Delta G_{\rm sp}}} \tag{1}

$$

$$

\displaystyle\mathrm{SP}_{\rm skew}=\frac{G_{\rm max}-\overline{G_{\rm sp}}}{G

_{\rm max}-G_{\rm min}} \tag{2}

$$

$$

\displaystyle\mathrm{NSR}=\frac{\sigma_{\Delta G_{\rm sp}}}{\overline{\Delta G

_{\rm sp}}} \tag{3}

$$

$G_{\rm max}$ and $G_{\rm min}$ represent the maximum and minimum values extracted from the full conductance swings, while $\overline{G_{\rm sp}}$ , $\overline{\Delta G_{\rm sp}}$ and $\sigma_{\Delta G_{sp}}$ denote the values of the mean conductance, mean conductance update and standard deviation of the conductance update at the symmetry point during the 1-pulse-up, 1-pulse-down procedure, respectively. Fig. 5 c shows the experimental Gaussian distributions of these metrics for the 32 devices within the array. The results indicate an average of 22 states, with a range from 16 to 33. A shift in the $G_{\rm sp}$ (or SP skew) of 61% is measured, reflecting a negative trend in the device asymmetry where the down response is steeper than the up response. An average NSR of 90% among the devices is obtained, demonstrating the capability to discriminate between pulses up and down around the symmetry point. This parameter reflects the intrinsic noise on the device’s response under identical conditions, highlighting an intra-device variation [38]. Previous studies on similar CMO/HfO x ReRAM systems [24] extracted these metrics from isolated 1R devices using an optimized open-loop scheme tailored to each device. In contrast, this work demonstrates for the first time that a single open-loop identical pulse scheme enables reliable operation of the entire CMO/HfO x 1T1R array, ensuring consistent performance across the array.

<details>

<summary>x5.png Details</summary>

### Visual Description

## Chart/Diagram Type: Analog Switching Characteristics of a ReRAM Device (Open-Loop)

### Overview

The image presents three interconnected technical visualizations analyzing a ReRAM (Resistive Random-Access Memory) device's behavior. Section **a** shows analog switching characteristics, **b** depicts array-level statistical responses, and **c** summarizes experimental metrics for Tiki-Taka training.

---

### Components/Axes

#### Section a: Analog Switching Characteristics

- **X-axis**: Pulse Number (0–2100)

- **Y-axis**: Conductance [μS] (logarithmic scale: 0–100)

- **Legend**:

- Red: Potentiation (1.35V, 2.5μs)

- Blue: Depression (1.3V, 2.5μs)

- **Inset**: Histogram of conductance after 1200 pulses (G₁₂₀₀) with ±σ shading.

#### Section b: Array-Level Open-Loop Statistical Response

- **X-axis**: Pulse Number (0–2100)

- **Y-axis**: Conductance [μS] (logarithmic scale: 0–100)

- **Legend**: Array experimental data (black line with ±σ shading).

- **Inset**: Histogram of conductance after 1200 pulses (G₁₂₀₀) with ±σ shading.

#### Section c: Experimental Array Metrics for Tiki-Taka Training

- **Histograms**:

1. **Number of States**: X-axis (0–40), mean = 22.

2. **Symmetry Point Skew (%)**: X-axis (20–110), mean = 61%.

3. **Noise to Signal Ratio (%)**: X-axis (70–110), mean = 90%.

- **Formulas**:

- N_states = (G_max - G_min) / ΔG_sp

- SP_skew = (G_max - G_sp) / G_max

- NSR = σΔG_sp / ΔG_sp

---

### Detailed Analysis

#### Section a

- **Potentiation (Red)**: Conductance increases sharply to ~100 μS at ~800 pulses, then stabilizes.

- **Depression (Blue)**: Conductance drops to ~10 μS at ~1600 pulses, then stabilizes.

- **Key Labels**:

- G_max ≈ 100 μS (potentiation peak).

- G_min ≈ 10 μS (depression trough).

- ΔG_sp ≈ 90 μS (difference between G_max and G_sp).

- G_sp ≈ 10 μS (conductance at symmetry point).

#### Section b

- **Array Data**: Conductance fluctuates between ~10 μS and ~100 μS, with ±σ shading indicating variability.

- **Inset Histogram**: Conductance distribution after 1200 pulses is approximately normal (G₁₂₀₀ ≈ 50 μS, ±σ ≈ ±10 μS).

#### Section c

- **Number of States**: Bimodal distribution with mean = 22.

- **Symmetry Point Skew**: Right-skewed distribution (mean = 61%).

- **Noise to Signal Ratio**: Left-skewed distribution (mean = 90%).

---

### Key Observations

1. **Conductance Switching**: Potentiation and depression create distinct conductance states (G_max ≈ 100 μS, G_min ≈ 10 μS).

2. **Statistical Variability**: Shaded regions in **b** indicate device-to-device or batch-to-batch variability.

3. **Training Metrics**:

- Tiki-Taka training increases the number of conductance states (mean = 22).

- Symmetry point skew (61%) and noise-to-signal ratio (90%) suggest trade-offs between precision and noise.

---

### Interpretation

- **ReRAM Behavior**: The device exhibits bistable conductance switching, critical for memory applications.

- **Array-Level Variability**: The ±σ shading in **b** highlights manufacturing or operational inconsistencies.

- **Tiki-Taka Training**: The metrics in **c** quantify how training affects device performance:

- Increased states (N_states) improve memory capacity.

- High skew (61%) and noise (90%) may limit reliability.

- **Trade-offs**: Optimizing for one metric (e.g., N_states) may degrade others (e.g., NSR).

---

**Note**: All values are approximate, derived from visual inspection of axis scales and legend labels. Uncertainties (e.g., ±σ) are inferred from shaded regions and histogram spreads.

</details>

Figure 5: Open-loop array characterization for on-chip training. a Bidirectional accumulative response and symmetry point of a representative device in the array. The top inset shows the open-loop identical pulse scheme used for the synaptic potentiation (red) and depression (blue). A conceptual illustration of the 8x4 CMO/HfO x ReRAM array is depicted on the left. b Array statistical open-loop response to identical pulses. The grey area represents the standard deviation of the experimental Gaussian distributions, each corresponding to a specific pulse number. The inset shows a representative example of the experimental G-distribution at pulse number 1200. The raw data can be found in Figure S9 of the Supporting Information. c The experimental probability densities of N states, SP skew and NSR, respectively. The experimental data used to extract the distributions are represented as points aligned along the y=0 horizontal axis.

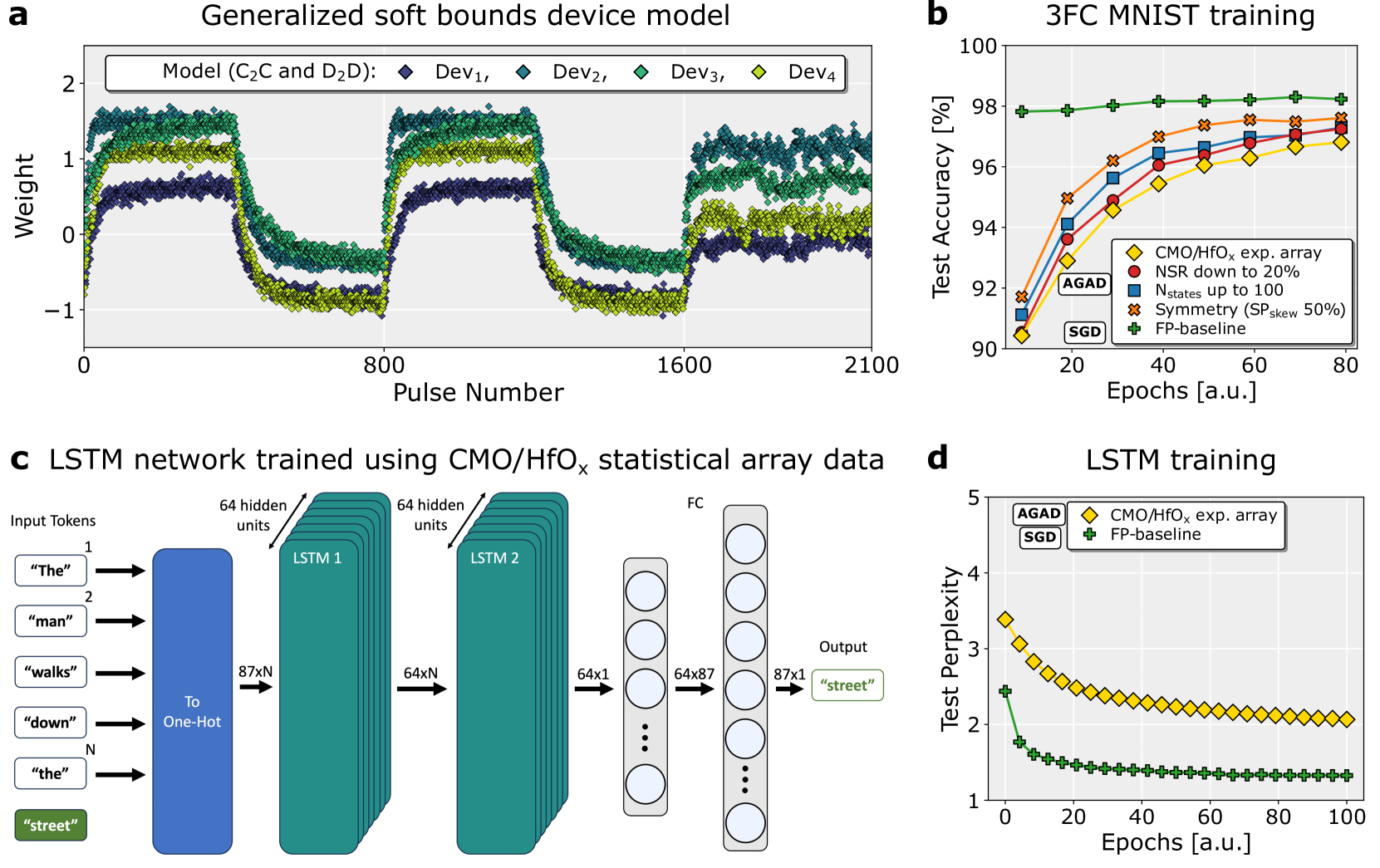

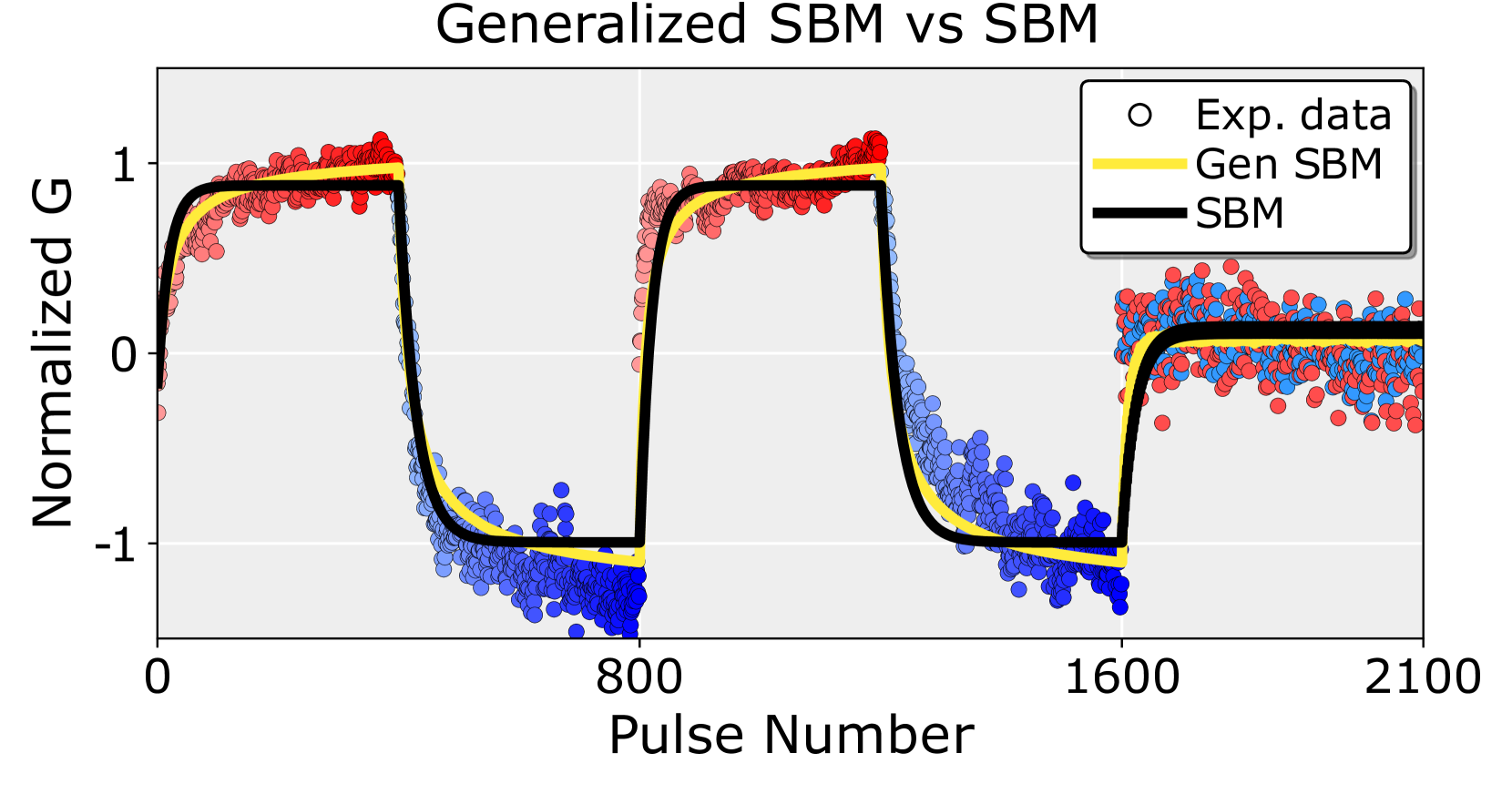

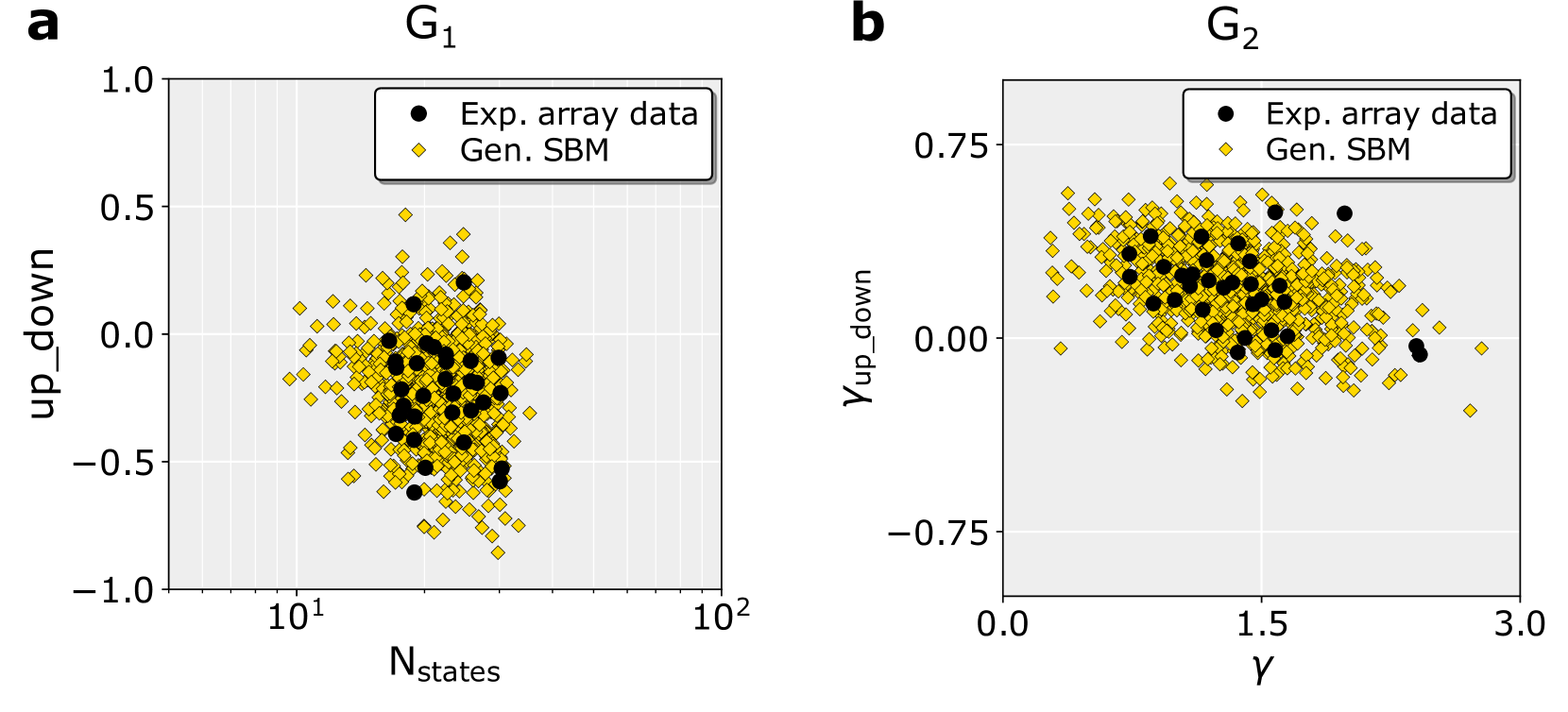

#### 2.3.2 Tiki-Taka training simulations

To perform realistic hardware-aware training simulations, the experimental device response is reproduced on software using the generalized soft bounds model implemented in the ’aihwkit’ [40], which better captures the bidirectional resistive switching behavior (see Fig. S8 in Supplementary Information) and accounts for intra- and inter-device variabilities (see cycle-to-cycle and device-to-device variations in Fig. 6 a). Additionally, Gaussian distributions are modelled based on parameters extracted from device characterization ( $G_{\rm max}$ , $G_{\rm min}$ , $\Delta G_{\rm sp}$ , NSR, SP skew) to account for device-to-device variability observed in the experimental characterization (see ”Methods” section ”Intra and inter-device variability” for details). This Gaussian fitting approach allows defining various device presets—characterized by the same model but with different parameter settings—to represent the synapses across the neural network. A realistic simulation setup is obtained by exclusively considering experimentally obtained parameters to reproduce the device trace (see ”Methods” section ”Generalized soft bounds model” for details). The device model is defined based on the observed conductance window and number of states, without assuming asymptotic behavior for an infinite number of pulses. This prevents overestimation of both the conductance window and the number of states (material states), enhancing the fidelity of the simulation. To validate analog training with CMO/HfO x ReRAM technology, a 3-layer fully connected (FC) neural network was trained on the MNIST dataset for image classification. In addition, the impact of the device’s number of states, asymmetry, and noise-to-signal ratio on accuracy and convergence time is evaluated by simulating identical networks in which each property is individually enhanced, while keeping the others fixed at the experimentally derived values. Literature has shown that these device characteristics critically influence the convergence of analog training algorithms [23]. Therefore, this method assesses the deviation of the current CMO/HfO x ReRAM device properties from the ideal analog resistive device scenario. Moreover, to show the scalability of the CMO/HfO x ReRAM technology to more computationally-intensive tasks, such as time series processing, a 2-layer long short-term memory (LSTM) network was trained on War and Peace text sequences to predict the next token. Each network is initially trained using conventional stochastic gradient descent (SGD) based backpropagation with 32-bit FP precision, serving as the baseline performance. Fig. 6 b illustrates the accuracy per epoch for the FP-baseline trained with SGD (in green) and the analog network trained using AGAD, evaluated under four different parameter settings: (1) properties extracted from the experimental array (in yellow), (2) reduced NSR to 20% (in red), (3) average of N states = 100 states (in blue), and (4) zero average device asymmetry (in orange). Using symmetrical device presets, i.e. with an average SP skew of 50%, improves accuracy by 0.7% with respect to analog training with CMO/HfO x ReRAM experimentally derived configuration (96.9%), landing an accuracy of 97.6%, a 0.7% lower than the FP-SGD baseline (98.3%). The other two configurations show less performance improvement, indicating more resilience of the AGAD-training to device’s N states and NSR. Additionally, a 2-layer LSTM network with 64 memory states each (see Fig. 6 c), is trained with the experimentally obtained configuration. The performance is measured using the exponential of the cross-entropy loss, i.e. the test perplexity metric, which quantifies the certainty of the token prediction. Results in Fig. 6 d demonstrate the capabilities of the CMO/HfO x ReRAM technology on more complex network architectures, such as LSTMs, and computationally demanding tasks, exhibiting performance comparable to the FP-equivalent, with an approximate 0.7% difference in test perplexity.

<details>

<summary>x6.png Details</summary>

### Visual Description

## Line Graph: Generalized Soft Bounds Device Model

### Overview

A line graph showing weight fluctuations across four devices (Dev1–Dev4) over 2100 pulses. The y-axis ranges from -1 to 2, with overlapping lines indicating device-specific weight variations.

### Components/Axes

- **X-axis**: Pulse Number (0–2100)

- **Y-axis**: Weight (-1 to 2)

- **Legend**:

- Dev1: Dark blue diamonds

- Dev2: Teal diamonds

- Dev3: Green diamonds

- Dev4: Yellow diamonds

### Detailed Analysis

- **Dev1 (Dark Blue)**: Starts at ~1.5, dips to ~0.5 at pulse 800, then rises to ~1.8 by pulse 2100.

- **Dev2 (Teal)**: Peaks at ~1.8 near pulse 0, drops to ~0.2 at pulse 800, then stabilizes at ~1.6.

- **Dev3 (Green)**: Begins at ~1.2, fluctuates between ~0.8 and ~1.5, ending at ~1.4.

- **Dev4 (Yellow)**: Starts at ~0.9, dips to ~0.3 at pulse 800, then rises to ~1.3.

### Key Observations

- All devices exhibit periodic dips around pulse 800.

- Dev1 and Dev2 show the most pronounced fluctuations.

- Dev4 has the smallest amplitude in weight changes.

### Interpretation

The graph suggests device-specific weight dynamics under a generalized model. The synchronized dip at pulse 800 may indicate a shared response to a stimulus or system reset. Dev1’s final weight (~1.8) implies higher sensitivity compared to others.

---

## Bar Chart: 3FC MNIST Training

### Overview

A bar chart comparing test accuracy (%) of five training methods over 80 epochs. The y-axis ranges from 90% to 100%.

### Components/Axes

- **X-axis**: Epochs (0–80, labeled "a.u.")

- **Y-axis**: Test Accuracy (%)

- **Legend**:

- CMO/HFOₓ exp. array: Yellow diamonds

- NSR down to 20%: Red circles

- Nstates up to 100: Blue squares

- Symmetry (SP_skew 50%): Orange crosses

- SGD: Green pluses

- FP-baseline: Green pluses (baseline)

### Detailed Analysis

- **CMO/HFOₓ exp. array**: Peaks at ~98% by 80 epochs.

- **NSR down to 20%**: Reaches ~97% by 80 epochs.

- **Nstates up to 100**: Stabilizes at ~96.5%.

- **Symmetry (SP_skew 50%)**: ~97.5% at 80 epochs.

- **SGD**: ~94% at 80 epochs.

- **FP-baseline**: ~98% (constant across epochs).

### Key Observations

- CMO/HFOₓ exp. array and FP-baseline achieve the highest accuracy.

- Symmetry (SP_skew 50%) outperforms Nstates and NSR.

- SGD lags significantly behind other methods.

### Interpretation

CMO/HFOₓ exp. array and FP-baseline demonstrate superior convergence, suggesting robust training dynamics. The FP-baseline’s consistency implies it serves as a strong benchmark. SGD’s lower performance highlights its limitations in this context.

---

## Diagram: LSTM Network Trained Using CMO/HFOₓ Statistical Array Data

### Overview

A block diagram of an LSTM network processing input tokens ("The", "man", "walks", etc.) to output "street".

### Components

1. **Input Layer**:

- Tokens converted to one-hot encoding (87xN).

2. **LSTM Layers**:

- **LSTM1**: 64 hidden units, 87x64xN input.

- **LSTM2**: 64 hidden units, 64x64xN input.

3. **Fully Connected (FC) Layer**: 64x87x1 output.

4. **Output**: "street" (87x1).

### Flow

Input → One-Hot Encoding → LSTM1 → LSTM2 → FC → Output.

### Key Observations

- The network uses two LSTM layers for sequential processing.

- The FC layer maps hidden states to output tokens.

### Interpretation

This architecture is designed for sequence-to-sequence tasks, leveraging LSTM’s memory capabilities. The one-hot encoding ensures discrete token representation, while the FC layer finalizes predictions.

---

## Line Graph: LSTM Training

### Overview

A line graph comparing test perplexity (1–5) of three methods over 100 epochs.

### Components/Axes

- **X-axis**: Epochs (0–100, labeled "a.u.")

- **Y-axis**: Test Perplexity

- **Legend**:

- AGAD: Yellow diamonds

- CMO/HFOₓ exp. array: Orange crosses

- FP-baseline: Green pluses

### Detailed Analysis

- **AGAD**: Starts at ~3.5, decreases to ~2.0 by 100 epochs.

- **CMO/HFOₓ exp. array**: Drops from ~3.0 to ~2.2.

- **FP-baseline**: Remains flat at ~1.2.

### Key Observations

- AGAD shows the steepest decline in perplexity.

- FP-baseline maintains the lowest perplexity throughout.

### Interpretation

AGAD’s rapid improvement suggests effective training dynamics. FP-baseline’s stability indicates it may represent an optimized or pre-trained model. The divergence between AGAD and FP-baseline highlights differences in training strategies.

</details>

Figure 6: Device model and on-chip training simulations. a Device presets generated using the generalized soft bounds model with experimentally extracted parameters of CMO/HfO x devices, including inter- and intra-device variabilities. b Training simulations of a 3-layer fully-connected neural network on MNIST (235K parameters), using 32-bit FP precision trained on SGD (in green). Analog training simulations were performed using AGAD considering the empirical distribution of the parameters (in yellow), enhanced NSR (in red), increased N states (in blue), and symmetrical device configurations (in orange). c LSTM network architecture for text forecasting on the War and Peace dataset (79K parameters). The architecture considers a sequence length of 100 tokens and accounts for 2 layers with 64 hidden units. d Training results of the FP baseline (in green) and the analog training with AGAD on the experimental device configuration (in yellow). The training setup can be found in the Supporting Information.

## 3 Discussion

An all-in-one technology platform based on analog filamentary CMO/HfO x ReRAM devices is presented. This platform addresses critical challenges in modern digital AI accelerators by overcoming the physical separation between memory and compute units. It enables the execution of forward and backward MVMs, along with weight updates and gradient computations, directly on a unified analog in-memory platform with $O(1)$ time complexity. This all-in-one approach fundamentally differs from DNN inference-only [9] and training-only [24, 41] analog accelerators. In inference-only accelerators, DNN weights are trained in software (i.e., off-chip) using traditional digital CPUs or GPUs and then programmed once onto the analog AI hardware accelerator. In training-only accelerators, the long-term retention capabilities and overall MVM accuracy for large array tiles are not assessed. In this work, a novel all-in-one analog computing platform, capable of both on-chip training and inference acceleration, is unveiled. The CMO/HfO x ReRAM devices are integrated in the BEOL of a NMOS transistor platform in a scalable 1T1R array architecture. The highly reproducible forming step demonstrates compatibility with NMOS rated for $\mathrm{3.3\,V}$ operation, while the uniform quasi-static 8W-cycling characteristics, achieved with voltage amplitudes of less than $\pm$ $\mathrm{1.5\,V}$ , exhibit a significant conductance window and a low off-state. The multi-bit capability of more than 32 states (5 bits), distinguishable after 10 minutes with less than 10% overlap error, is experimentally demonstrated using an identical-pulse closed-loop scheme. The characterization of the weight transfer reveals record-low programming noise ranging from $\mathrm{10\,nS}$ to $\mathrm{100\,nS}$ , more than one order of magnitude lower than that of other memristive technologies targeting similar conductance ranges [34, 35, 36]. Each conductance distribution exhibits a state-independent relaxation process over time, characterized by a slight shift of the mean toward lower conductance and an increase in the standard deviation. This independence of the relaxation process from the target conductance is advantageous for implementing effective compensation schemes in the future. Realistic MVM simulations on a 64x64 array tile, considering CMO/HfO x ReRAM device non-idealities such as finite weight transfer resolution, conductance relaxation, limited input/output quantization, and IR-drop across array wires, show an RMSE as low as 0.2 compared to the ideal FP-case, even 10 years after programming. This demonstrates that the CMO/HfO x ReRAM devices improve analog MVM accuracy by a factor of 20 and 3 compared to the state of the art [9], 1 second and 10 years after programming, respectively. Although this study was performed at room temperature, previous characterization of a similar CMO/HfO x ReRAM stack demonstrated the thermal stability of the analog states at high temperature (less than 4% drift after 72 hours at 85 °C) [24]. Future studies will focus on incorporating the experimental read noise of CMO/HfO x ReRAM devices, characterized between 0.2% and 2% of G target within a similar conductance range as used in this work [25], into MVM accuracy simulations. Although read noise is not included in the MVM simulations of this study, no significant additional drop in MVM accuracy is anticipated. In fact, the magnitude of read noise is much smaller than that of the relaxation process and of the effect of reduced input/output quantization, which dominate the RMSE on different timescales. Furthermore, simulation results demonstrate the suitability of CMO/HfO x ReRAM technology for large 512x512 array, with the IR-drop expected to become the primary accuracy bottleneck in this case. Finally, the electrical response of the CMO/HfO x ReRAM array to an open-loop scheme with identical pulses demonstrates the viability of this technology for on-chip training applications. A realistic device model, accounting for both inter- and intra-device variability, is derived from experimental data. Table 1 benchmarks the representative device model used in this work on the MNIST dataset against other approaches, highlighting its high fidelity in reproducing experimental device responses.

Table 1: Device model benchmarking: from simplified approaches to realistic non-ideality modeling

| Ti/HfO x [41] | Not-included | exp. states Measured number of analog states during open-loop device characterization. | BEOL array | TTv2 | Medium | 90.5 % |

| --- | --- | --- | --- | --- | --- | --- |

| Ta/TaO x [41] | Not-included | exp. states Measured number of analog states during open-loop device characterization. | BEOL array | TTv2 | Medium | 96.4 % |

| TaO x /HfO x [24] | included | material states The asymptotic number of states under an infinite number of pulses. | Single ReRAMs | TTv2 | Medium | 97.4 % |

| CMO x /HfO x This work. | included | exp. states Measured number of analog states during open-loop device characterization. | BEOL array | AGAD | High | 96.9 % |

The impact of the device’s number of states, asymmetry and noise-to-signal ratio on training accuracy using the AGAD algorithm on MNIST is evaluated. This analysis demonstrates that, with the current device’s experimental properties, AGAD analog training achieves 96.9% accuracy, comparable to the ideal FP-baseline of 98.3%. To further improve analog training performance and bring results closer to the software equivalent, the key metric to enhance in the device is the symmetry. Finally, the on-chip analog training capabilities of the CMO/HfO x ReRAM technology are demonstrated on a more complex 2-layer LSTM network, showing comparable performance to its floating-point equivalent. In conclusion, the novel CMO/HfO x ReRAM all-in-one technology platform presented in this work lays the foundation for efficient and versatile analog chips capable of combining both training and inference capabilities, enabling autonomous, energy-efficient, and adaptable AI systems.

## 4 Methods

### 4.1 Device fabrication