# REASON: Accelerating Probabilistic Logical Reasoning for Scalable Neuro-Symbolic Intelligence

**Authors**: Zishen Wan, Che-Kai Liu, Jiayi Qian, Hanchen Yang, Arijit Raychowdhury, Tushar Krishna

## Abstract

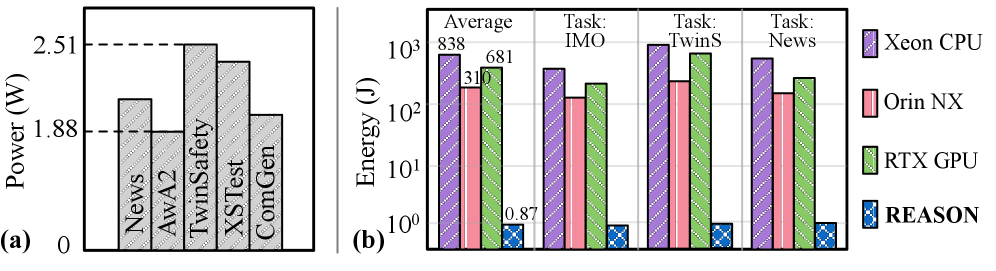

Neuro-symbolic AI systems integrate neural perception with symbolic and probabilistic reasoning to enable data-efficient, interpretable, and robust intelligence beyond purely neural models. Although this compositional paradigm has shown superior performance in domains such as mathematical reasoning, planning, and verification, its deployment remains challenging due to severe inefficiencies in symbolic and probabilistic inference. Through systematic analysis of representative neuro-symbolic workloads, we identify probabilistic logical reasoning as the inefficiency bottleneck, characterized by irregular control flow, low arithmetic intensity, uncoalesced memory accesses, and poor hardware utilization on CPUs and GPUs.

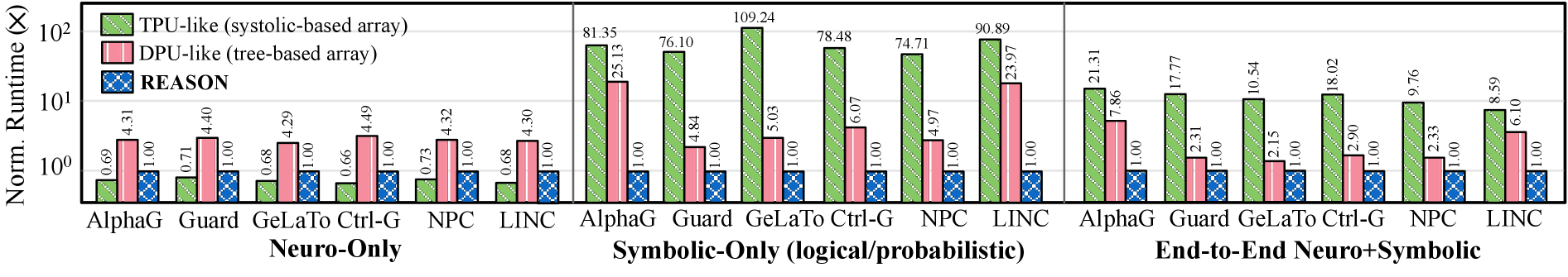

This paper presents REASON, an integrated acceleration framework for probabilistic logical reasoning in neuro-symbolic AI. At the algorithm level, REASON introduces a unified directed acyclic graph representation that captures common structure across symbolic and probabilistic models, coupled with adaptive pruning and regularization. At the architecture level, REASON features a reconfigurable, tree-based processing fabric optimized for irregular traversal, symbolic deduction, and probabilistic aggregation. At the system level, REASON is tightly integrated with GPU streaming multiprocessors through a programmable interface and multi-level pipeline that efficiently orchestrates neural, symbolic, and probabilistic execution. Evaluated across six neuro-symbolic workloads, REASON achieves 12-50 $\times$ speedup and 310-681 $\times$ energy efficiency over desktop and edge GPUs under TSMC 28 nm node. REASON enables real-time probabilistic logical reasoning, completing end-to-end tasks in 0.8 s with 6 mm ${}^{\text{2}}$ area and 2.12 W power, demonstrating that targeted acceleration of probabilistic logical reasoning is critical for practical and scalable neuro-symbolic AI and positioning REASON as a foundational system architecture for next-generation cognitive intelligence.

## I Introduction

Large Language Models (LLMs) have demonstrated remarkable capabilities in natural language understanding, image recognition, and complex pattern learning from vast datasets [23, 46, 42, 16]. However, despite their success, LLMs often struggle with factual accuracy, hallucinations, multi-step reasoning, and interpretability [35, 62, 2, 61]. These limitations have spurred the development of compositional AI systems, which integrate neural with symbolic and probabilistic reasoning to create robust, transparent, and intelligent cognitive systems. footnotetext: † Corresponding author

One promising compositional paradigm is neuro-symbolic AI, which integrates neural, symbolic, and probabilistic components into a unified cognitive architecture [60, 1, 72, 9, 75]. In this system, the neural module captures the statistical, pattern-matching behavior of learned models, performing rapid function approximation and token prediction for intuitive perception and feature extraction. The symbolic and probabilistic modules perform explicit, verifiable reasoning that is structured, interpretable, and robust under uncertainty, managing logic-based reasoning and probabilistic updates. This paradigm integrates intuitive generalization and deliberate reasoning.

Neuro-symbolic AI has demonstrated superior abstract deduction, complex question answering, mathematical reasoning, logical reasoning, and cognitive robotics [28, 66, 55, 81, 12, 38, 41, 71]. Its ability to learn efficiently from fewer data points, produce transparent and verifiable outputs, and robustly handle uncertainty and ambiguity makes it particularly advantageous compared to purely neural approaches. For example, recently Meta’s LIPS [28] and Google’s AlphaGeometry [66] leverage compositional neuro-symbolic approaches to solve complex math problems and achieve a level of human Olympiad gold medalists. R 2 -Guard [20] leverages LLM and probabilistic models to improve robust reasoning capability and resilience against jailbreaks. They represent a paradigm shift for AI that requires robust, verifiable, and explainable reasoning.

Despite impressive algorithmic advances in neuro-symbolic AI – often demonstrated on large-scale distributed GPU clusters – efficient deployment at the edge remains a fundamental challenge. Neuro-symbolic agents, particularly in robotics, planning, interactive cognition, and verification, require real-time logical inference to interact effectively with physical environments and multi-agent systems. For example, Ctrl-G, a text-infilling neuro-symbolic agent [83], must execute hundreds of reasoning steps per second to remain responsive, yet current implementations take over 5 minutes on a desktop GPU to complete a single task. This latency gap makes practical deployment of neuro-symbolic AI systems challenging.

To understand the root causes of this inefficiency, we systematically analyze a diverse set of neuro-symbolic workloads and uncover several system- and architecture-level challenges. Symbolic and probabilistic kernels frequently dominate end-to-end runtime and exhibit highly irregular execution characteristics, including heterogeneous compute patterns and memory-bound behavior with low ALU utilization. These kernels suffer from limited exploitable parallelism and irregular, uncoalesced memory accesses, leading to poor performance and efficiency on CPU and GPU architectures.

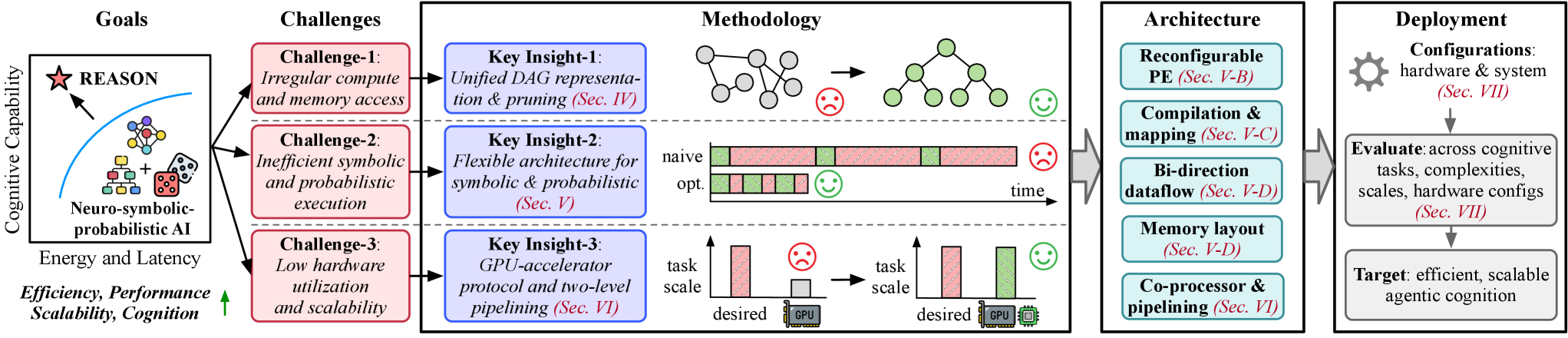

To address these challenges, we develop an integrated acceleration framework, REASON, which to the best of our knowledge, is the first to accelerate probabilistic logical reasoning-based neuro-symbolic AI systems. REASON is designed to close the efficiency gap of compositional AI by jointly optimizing algorithms, architecture, and system integration for the irregular and heterogeneous workloads inherent to neuro-symbolic reasoning.

At the algorithm level, REASON introduces a unified directed acyclic graph (DAG) representation that captures shared computational structure across symbolic and probabilistic kernels. An adaptive pruning and regularization technique further reduces model size and computational complexity while preserving task accuracy. At the architecture level, REASON features a flexible design optimized for various irregular symbolic and probabilistic computations, leveraging the unified DAG representation. The architecture comprises reconfigurable tree-based processing elements (PEs), compiler-driven workload mapping, and memory layout to enable highly parallel and energy-efficient symbolic and probabilistic computation. At the system level, REASON is tightly integrated with GPU streaming multiprocessors (SMs), forming a heterogeneous system with a programmable interface and multi-level execution pipeline that efficiently orchestrates neural, symbolic, and probabilistic kernels while maintaining high hardware utilization and scalability as neuro-symbolic models evolve. Notably, unlike conventional tree-like computing arrays optimized primarily for neural workloads, REASON provides reconfigurable support for neural, symbolic, and probabilistic kernels within a unified execution fabric, enabling efficient and scalable neuro-symbolic AI systems.

This paper, therefore, makes the following contributions:

- We conduct a systematic workload characterization of representative logical- and probabilistic-reasoning-based neuro-symbolic AI models, identifying key performance bottlenecks and architectural optimization opportunities (Sec. II, Sec. III).

- We propose REASON, an integrated co-design framework, to efficiently accelerate probabilistic logical reasoning in neuro-symbolic AI, enabling practical and scalable deployment of compositional intelligence (Fig. 4).

- REASON introduces cross-layer innovations spanning (i) a unified DAG representation with adaptive pruning at the algorithm level (Sec. IV), (ii) a reconfigurable symbolic/probabilistic architecture and compiler-driven dataflow and mapping at the hardware level (Sec. V), and (iii) a programmable system interface with a multi-level execution pipeline at the system level (Sec. VI) to improve neuro-symbolic efficiency.

- Evaluated across cognitive tasks, REASON enables flexible support for symbolic and probabilistic operations, achieving 12-50 $\times$ speedup and 310-681 $\times$ energy efficiency compared to desktop and edge GPUs. REASON enables fast and efficient logical and probabilistic reasoning in 0.8 s per task with 6 mm 2 area and 2.12 W power consumption. (Sec. VII).

## II Neuro-Symbolic AI Systems

This section presents the preliminaries of neuro-symbolic AI with its algorithm flow (Sec. II-A), scaling performance analysis (Sec. II-B), and key computational primitives (Sec. II-C).

<details>

<summary>x1.png Details</summary>

### Visual Description

\n

## Diagram: Neuro-Symbolic AI Architecture and Applications

### Overview

This image is a technical diagram illustrating a hybrid neuro-symbolic artificial intelligence architecture. It visually explains how neural networks (fast thinking) integrate with symbolic reasoning systems (slow, logical, and probabilistic thinking) and provides concrete application examples of this combined approach.

### Components/Axes

The diagram is organized into three main horizontal sections:

1. **Top Section (Architecture Diagram):**

* **Left Block (Pink):** Labeled "Neuro". Contains an icon of a neural network and the text "DNN/LLM (Fast Thinking)".

* **Center Block (Green/Blue):** Labeled "Symbolic". This is a larger container split into two sub-blocks:

* **Top Sub-block (Green):** Labeled "Logical (Slow Thinking)" with a logic gate icon.

* **Bottom Sub-block (Blue):** Labeled "Probabilistic (Bayesian Thinking)" with a dice icon.

* **Right Section (Detailed Models):** This area expands on the "Symbolic" components with two shaded boxes:

* **Top Box (Light Green):** Titled "First-Order Logic (FOL) Boolean Satisfiability (SAT)". Contains a circuit-like diagram with inputs `X₁`, `X₂`, `X₃`, `X₄` connected through logical operators (∩, ∪, ¬) to outputs `Y₁`, `Y₂`.

* **Bottom Box (Light Blue):** Contains two models:

* **Left Model:** Titled "Probabilistic Circuit (PC)". Shows a network diagram with inputs `X₁`, `X₂`, `X₃`, `X₄` connected to nodes labeled `f` and `g` with multiplication (×) and addition (+) operations.

* **Right Model:** Titled "Hidden Markov Model (HMM)". Shows a state transition diagram with observed states `X₁`, `X₂`, `X₃` and hidden states `S₁`, `S₂`, `S₃` connected in a chain.

2. **Bottom Section (Application Examples):**

* **Left Column:** Header "Application Examples".

* **Main Grid:** A 5-row table mapping application domains to a three-stage pipeline. Each row has a domain name followed by three process steps connected by arrows (→). The steps are color-coded to correspond with the architecture above (pink for neural, green for logical, blue for probabilistic).

| Application Domain | Stage 1 (Neural - Pink) | Stage 2 (Logical - Green) | Stage 3 (Probabilistic - Blue) |

|--------------------|-------------------------|---------------------------|--------------------------------|

| Commonsense Reason | feature extraction → | rule logic → | uncertainty infer. |

| Cognitive Robotics | scene graph → | logic-based planning → | uncertainty infer. |

| Medical Diagnosis | feature extraction → | rule reasoning → | likelihood infer. |

| Question Answering | parsing → | symbolic query planning → | missing fact infer. |

| Math Solving | initial sol. gen. → | algebra solver → | uncertainty infer. |

### Detailed Analysis

**Architecture Flow:**

The diagram shows a directional flow from left to right. The "Neuro" (DNN/LLM) component, responsible for "Fast Thinking," feeds into the "Symbolic" component. The Symbolic component is bifurcated into "Logical (Slow Thinking)" and "Probabilistic (Bayesian Thinking)" modules, which interact bidirectionally (indicated by up/down arrows between them). Dashed lines connect these high-level symbolic modules to their specific formal implementations (FOL/SAT, PC, HMM) on the right.

**Application Pipeline Details:**

Each application follows a consistent three-stage pattern:

1. **Stage 1 (Pink - Neural):** Initial data processing or representation.

2. **Stage 2 (Green - Logical):** Structured reasoning or planning.

3. **Stage 3 (Blue - Probabilistic):** Inference under uncertainty.

The specific pipelines are as shown in the table above.

### Key Observations

1. **Clear Conceptual Mapping:** The color coding (pink, green, blue) is consistently applied across the high-level architecture and the application pipelines, creating a strong visual link between theory and practice.

2. **Bidirectional Interaction:** The arrows between the "Logical" and "Probabilistic" blocks indicate that these reasoning modes are not sequential but interactive and mutually informative within the symbolic system.

3. **Formal Grounding:** The diagram explicitly connects abstract concepts ("Logical Thinking") to concrete, established formal methods (First-Order Logic, SAT), providing technical specificity.

4. **Pipeline Consistency:** All five diverse applications (from robotics to math) are shown to follow the same fundamental neuro-symbolic processing paradigm, suggesting the framework's generality.

### Interpretation

This diagram argues for a unified AI architecture that marries the pattern recognition strengths of neural networks ("fast thinking") with the rigorous, explainable reasoning of symbolic systems ("slow thinking"). The "Neuro" component likely handles raw data perception and initial feature extraction, while the "Symbolic" component performs structured reasoning, planning, and inference.

The inclusion of both deterministic (Logical/FOL) and stochastic (Probabilistic/Bayesian) models within the symbolic half acknowledges that real-world reasoning requires handling both strict rules and inherent uncertainty. The application examples demonstrate the practical value of this hybrid approach: it enables systems that can not only perceive and parse the world (via neural nets) but also plan, explain decisions, and reason about missing or uncertain information (via symbolic logic and probability).

The overall message is that moving beyond pure neural or pure symbolic AI towards an integrated neuro-symbolic paradigm is a powerful direction for creating more robust, generalizable, and trustworthy AI systems capable of complex tasks like medical diagnosis and cognitive robotics.

</details>

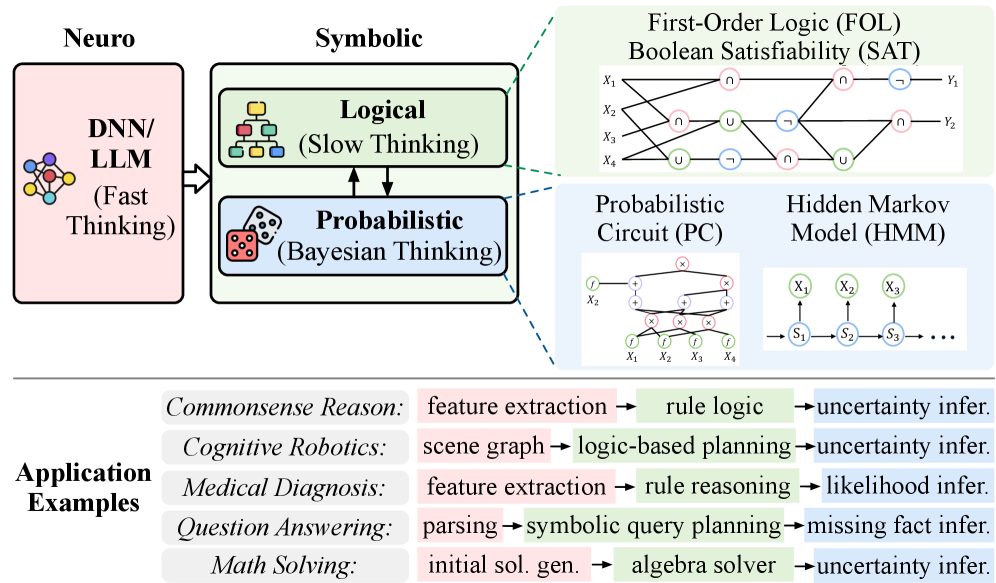

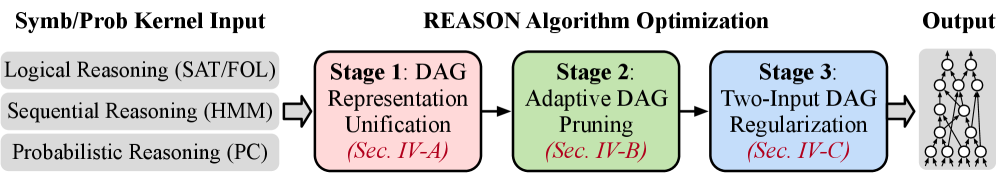

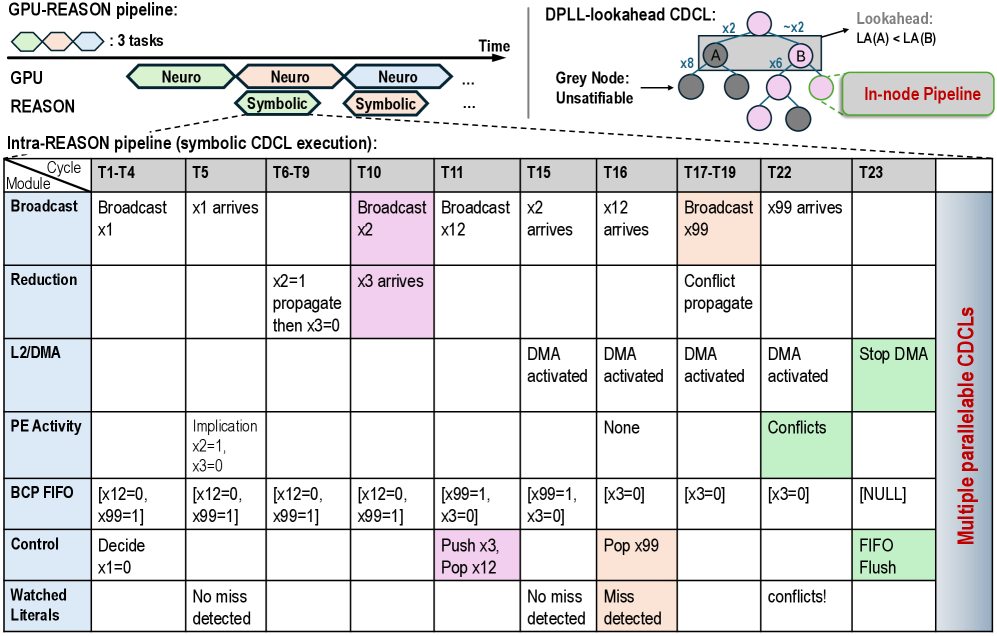

Figure 1: Neuro-symbolic algorithmic flow and operations. The neural module serves as a perceptual and intuitive engine for representation learning, while the symbolic module performs structured logical reasoning with probabilistic inference. This compositional pipeline enables complex cognitive tasks across diverse scenarios.

### II-A Neuro-Symbolic Cognitive Intelligence

LLMs and DNNs excel at natural language understanding and image recognition. However, they remain prone to factual errors, hallucinations, challenges in complex multi-step reasoning, and vulnerability to out-of-distribution or adversarial inputs. Their black-box nature also impedes interpretability and formal verification, undermining trust in safety-critical domains. These limitations motivate the development of compositional systems that integrate neural models with symbolic and probabilistic reasoning to achieve greater robustness, transparency, and intelligence.

Neuro-symbolic AI represents a paradigm shift toward more integrated and trustworthy intelligence by combining neural, symbolic, and probabilistic techniques. This hybrid approach has shown superior performance in abstract deduction [81, 12], complex question answering [38, 41], and logical reasoning [66, 55]. By learning from limited data and producing transparent, verifiable outputs, neuro-symbolic systems provide a foundation for cognitive intelligence. Fig. 1 presents a unified neuro-symbolic pipeline, illustrating how its components collaborate to solve complex tasks.

<details>

<summary>x2.png Details</summary>

### Visual Description

## Scaling Performance Analysis: Task Accuracy vs. Model Size & Scaling Efficiency Analysis: Task Runtime vs. Complexity

### Overview

The image is a composite figure containing four distinct charts, labeled (a), (b), (c), and (d). The first three charts (a, b, c) are scatter plots analyzing the relationship between **Model Size** and **Task Accuracy (%)** across different task categories. The fourth chart (d) is a line graph comparing the **Task runtime (min)** of two different model types against increasing problem complexity. The overall theme is the scaling behavior of AI models in terms of accuracy and computational efficiency.

### Components/Axes

**Common Elements (Charts a, b, c):**

* **X-Axis:** "Model Size" with categorical markers: `7B`, `8B`, `13B`, `70B`, `GPT`.

* **Y-Axis:** "Task Accuracy (%)" with a linear scale from 0 to 100, marked at intervals of 20.

* **Legends:** Each chart has a legend positioned in the top-left corner, listing specific tasks with unique color and marker shape combinations. The legend distinguishes between two variants for each task, denoted by `(C)` and `(M)`.

* **Data Points:** Each data point is a marker (circle, square, triangle, etc.) representing the accuracy of a specific task variant on a specific model size.

**Chart (d) Specifics:**

* **Title:** "Scaling Efficiency Analysis: Task Runtime vs. Complexity"

* **X-Axis:** "Inter. Math Olympiad reasoning (Year_Problem)" with categorical labels: `P01_P08`, `P06_P12`, `P04_P12`, `P12_P15`, `P20_P16`, `P19_P6`. These likely represent problem sets from different years.

* **Y-Axis:** "Task runtime (min)" with a linear scale from 0 to 30, marked at intervals of 10.

* **Legend:** Positioned in the top-left corner, identifying two data series:

* `Neuro-symbolic models (AlphaGeometry)`: Represented by a blue line with circular markers.

* `RL-based OST reasoning models`: Represented by a gray line with circular markers.

### Detailed Analysis

**Chart (a): Complex Reasoning Tasks**

* **Tasks & Legend:**

* `TextEdit (C)`: Blue circle

* `ACLUTR (C)`: Orange triangle (pointing up)

* `ProofWriter (C)`: Green triangle (pointing down)

* `TextEdit (M)`: Gray square

* `ACLUTR (M)`: Brown diamond

* `ProofWriter (M)`: Light blue circle

* **Trend & Data Points (Approximate):**

* **General Trend:** Accuracy for all tasks generally increases with model size. The `(C)` variants consistently outperform their `(M)` counterparts.

* `TextEdit (C)`: Starts high (~90% at 7B), approaches ~100% at GPT.

* `ACLUTR (C)`: Starts low (~20% at 7B), shows strong improvement to ~70% at GPT.

* `ProofWriter (C)`: Starts very low (~10% at 7B), improves to ~80% at GPT.

* `TextEdit (M)`: Starts around 50% at 7B, improves to ~90% at GPT.

* `ACLUTR (M)`: Starts around 20% at 7B, improves to ~60% at GPT.

* `ProofWriter (M)`: Starts near 0% at 7B, improves to ~40% at GPT.

**Chart (b): Math Reasoning Tasks**

* **Tasks & Legend:**

* `GSM8K (C)`: Blue circle

* `SVAMP (C)`: Orange triangle (pointing up)

* `TabMWP (C)`: Green triangle (pointing down)

* `In-Domain GSM8K (C)`: Gray square

* `In-Domain MATH (C)`: Brown diamond

* **Trend & Data Points (Approximate):**

* **General Trend:** Accuracy improves with model size, but performance is more varied and generally lower than in complex reasoning tasks. `In-Domain MATH (C)` is the most challenging.

* `GSM8K (C)`: Starts ~55% at 7B, improves to ~95% at GPT.

* `SVAMP (C)`: Starts ~60% at 7B, improves to ~90% at GPT.

* `TabMWP (C)`: Starts ~40% at 7B, improves to ~85% at GPT.

* `In-Domain GSM8K (C)`: Starts ~25% at 7B, improves to ~70% at GPT.

* `In-Domain MATH (C)`: Starts ~10% at 7B, improves to ~50% at GPT.

**Chart (c): Question-Answering Tasks**

* **Tasks & Legend:**

* `AmbigNQ (C)`: Blue circle

* `TriviaQA (C)`: Orange triangle (pointing up)

* `HotpotQA (C)`: Green triangle (pointing down)

* `AmbigNQ (M)`: Gray square

* `TriviaQA (M)`: Brown diamond

* `HotpotQA (M)`: Light blue circle

* **Trend & Data Points (Approximate):**

* **General Trend:** Strong positive correlation between model size and accuracy. `(C)` variants again outperform `(M)` variants.

* `AmbigNQ (C)`: Starts ~65% at 7B, improves to ~95% at GPT.

* `TriviaQA (C)`: Starts ~60% at 7B, improves to ~90% at GPT.

* `HotpotQA (C)`: Starts ~55% at 7B, improves to ~85% at GPT.

* `AmbigNQ (M)`: Starts ~55% at 7B, improves to ~80% at GPT.

* `TriviaQA (M)`: Starts ~40% at 7B, improves to ~75% at GPT.

* `HotpotQA (M)`: Starts ~30% at 7B, improves to ~60% at GPT.

**Chart (d): Scaling Efficiency Analysis**

* **Trend & Data Points (Approximate):**

* **Neuro-symbolic models (AlphaGeometry) - Blue Line:** Shows a steep, near-linear increase in runtime with problem complexity. Starts at ~8 min for `P01_P08`, rises to ~13 min for `P19_P6`.

* **RL-based OST reasoning models - Gray Line:** Shows a more gradual, slightly super-linear increase. Starts at ~12 min for `P01_P08`, rises to ~28 min for `P19_P6`.

* **Key Observation:** The RL-based models have a higher initial runtime but scale worse (steeper slope) than the neuro-symbolic models as problem complexity increases. The lines cross between `P04_P12` and `P12_P15`, after which the neuro-symbolic models become more efficient.

### Key Observations

1. **Consistent Scaling:** Across all task types (Complex Reasoning, Math, QA), increasing model size from 7B to GPT leads to significant accuracy gains.

2. **Task Difficulty Hierarchy:** Within each chart, certain tasks are consistently harder. For example, `ProofWriter (M)` in (a), `In-Domain MATH (C)` in (b), and `HotpotQA (M)` in (c) show the lowest accuracies.

3. **Variant Performance Gap:** The `(C)` variant of each task consistently achieves higher accuracy than the `(M)` variant across all model sizes, suggesting a fundamental difference in difficulty or evaluation setup.

4. **Efficiency Trade-off (Chart d):** There is a clear trade-off between model architecture and scaling efficiency. While RL-based models may have higher base runtime, neuro-symbolic models (AlphaGeometry) demonstrate superior scaling characteristics for this specific reasoning domain, becoming more efficient on more complex problems.

### Interpretation

The data presents a multi-faceted view of AI scaling. Charts (a-c) demonstrate the **"scaling law"** phenomenon: larger models are more capable, as measured by task accuracy. However, the gains are not uniform; they depend heavily on the specific task and its variant. The persistent gap between `(C)` and `(M)` variants suggests that model improvements alone may not close performance gaps on inherently more difficult problem formulations.

Chart (d) shifts the focus from capability (accuracy) to **efficiency (runtime)**. It reveals that scaling behavior is not monolithic. Different architectural paradigms (neuro-symbolic vs. reinforcement learning-based) exhibit fundamentally different computational cost profiles as problem complexity grows. The crossover point indicates that the "best" model depends on the operational context—specifically, the expected complexity of the problems to be solved. For simpler problems, one architecture may be preferable, while for highly complex Olympiad-level reasoning, the other becomes more efficient.

In summary, the image argues that evaluating AI systems requires looking beyond a single metric. True understanding comes from analyzing **capability scaling** (accuracy vs. size) alongside **efficiency scaling** (runtime vs. complexity), and doing so across a diverse set of tasks that probe different facets of intelligence.

</details>

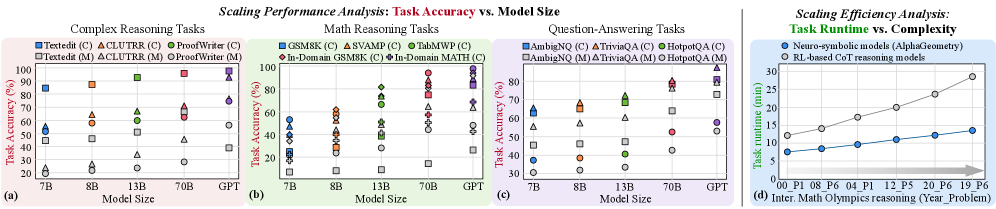

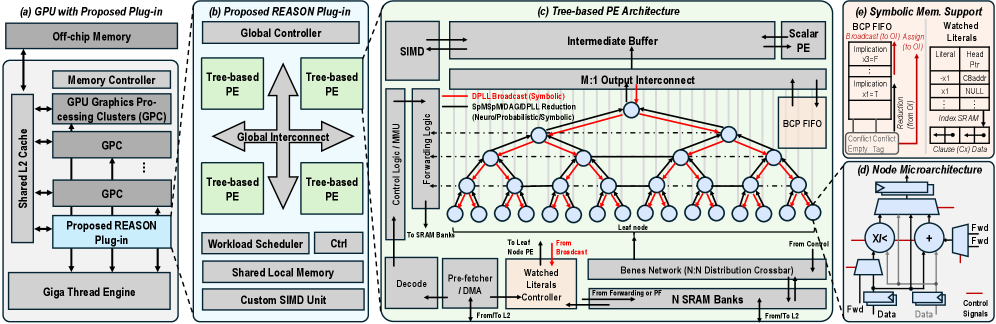

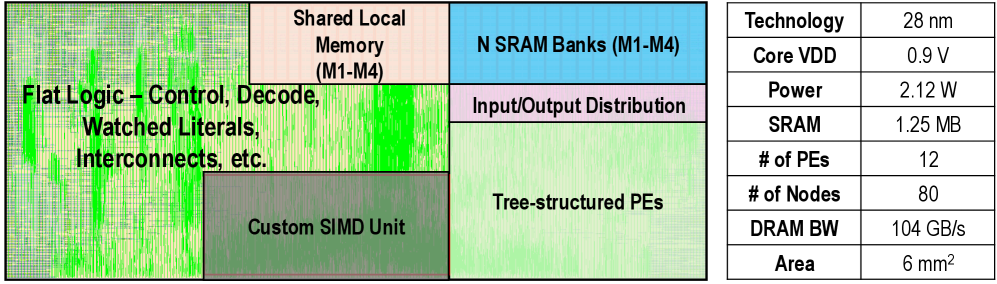

Figure 2: Scaling performance and efficiency. (a)-(c) Task accuracy of compositional LLM-symbolic models (C) and monolithic LLMs (M - shown in gray) across model sizes on complex reasoning, mathematical reasoning, and question-answering tasks. (d) Runtime efficiency comparison between LLM-symbolic models and RL-based CoT models on mathematical reasoning tasks [76].

Neural module. The neural module serves as the perceptual and intuitive engine, typically DNN or LLM, excelling at processing high-dimensional sensory inputs (e.g., images, audio, text) and converting them into feature representations. It handles perception, feature extraction, and associative learning, providing the abstractions needed for higher-level cognition.

Symbolic module. The symbolic module is the logical core operating on neural abstractions and includes symbolic and probabilistic operations. Logical components apply formal logic, rules, and ontologies for structured reasoning and planning, enabling logically sound solutions. Probabilistic components manage uncertainty by representing knowledge probabilistically, supporting belief updates and decision-making under ambiguity, reflecting a nuanced reasoning model.

Together, these modules form a complementary reasoning hierarchy. Neural module captures statistical, pattern-matching behavior of learned models, producing rapid but non-verifiable outputs (Fast Thinking), while symbolic modules perform explicit, verifiable reasoning that is structured and reliable (Slow Thinking). The probabilistic module complements both and enables robust planning under ambiguity (Bayesian Thinking). This framework integrates intuitive generalization with deliberate reasoning.

### II-B Scaling Performance Analysis of Neuro-Symbolic Systems

Scaling performance analysis. Neuro-symbolic AI systems exhibit superior reasoning capability and scaling behavior compared to monolithic LLMs on complex tasks. We compare representative neuro-symbolic systems against monolithic LLMs across complex reasoning, mathematical reasoning, and question-answering benchmarks (Fig. 2 (a)-(c)). The results reveal two advantages. First, higher accuracy: compositional neuro-symbolic models consistently outperform monolithic LLMs of comparable size. Second, improved scaling efficiency: smaller neuro-symbolic models are sufficient to match or exceed the performance of significantly larger closed-source LLMs. Together, these results highlight the potential scaling limitations of monolithic LLMs and the efficiency benefits of compositional neuro-symbolic reasoning.

Comparison with RL-based reasoning models. Beyond monolithic LLMs, recent advancements in reinforcement learning (RL) and chain-of-thought (CoT) prompting improve LLM reasoning accuracy but incur significant computational and scalability overheads (Fig. 2 (d)). First, computational cost: RL-based reasoning often requires hundreds to thousands of LLM queries per decision step, resulting in prohibitively high inference latency and energy consumption. Second, scalability: task-specific fine-tuning constrains generality, whereas neuro-symbolic models use symbolic and probabilistic reasoning modules or tools without retraining. Fig. 2 (d) reveals that neuro-symbolic models AlphaGeometry [66] achieve over $2\times$ efficiency gains and superior data efficiency compared to CoT-based LLMs on mathematical reasoning tasks.

### II-C Computational Primitives in Neuro-Symbolic AI

We identify the core computational primitives that are commonly used in neuro-symbolic AI systems (Fig. 1). While neural modules rely on DNNs or LLMs for perception and representation learning, the symbolic and probabilistic components implement structured reasoning. In particular, logical reasoning is typically realized through First-Order Logic (FOL) and Boolean Satisfiability (SAT), probabilistic reasoning through Probabilistic Circuits (PCs), and sequential reasoning through Hidden Markov Models (HMMs). Together, these primitives form the algorithmic foundation of neuro-symbolic systems that integrate learning, logic, and uncertainty-aware inference.

First-Order Logic (FOL) and Boolean Satisfiability (SAT). FOL provides a formal symbolic language for representing structured knowledge using predicates, functions, constants, variables and quantifiers ( $\forall,\exists$ ), combined with logical connectives. For instance, the statement “every student has a mentor” can be expressed as $\forall x\bigl(\mathrm{Student}(x)\to\exists y\,(\mathrm{Mentor}(y)\wedge\mathrm{hasMentor}(x,y))\bigr)$ , where predicates encode properties and relations over domain elements. FOL semantics map symbols to domain objects and relations, enabling precise and interpretable logical reasoning. SAT operates over propositional logic and asks whether a conjunctive normal form (CNF) formula $\varphi=\bigwedge_{i=1}^{m}\Bigl(\bigvee_{j=1}^{k_{i}}l_{ij}\Bigr)$ admits a satisfying assignment, where each literal $l_{ij}$ is a Boolean variable or its negation. Modern SAT solvers extend the DPLL algorithm with conflict-driven clause learning (CDCL), incorporating non-chronological backtracking and clause learning to improve scalability [40, 33]. Cube-and-conquer further parallelizes search by splitting into “cube” DPLL subproblems and concurrent CDCL “conquer” solvers [13, 67]. Together, FOL’s expressive representations and SAT’s solving mechanisms form the logic backbone of neuro-symbolic systems, enabling exact logical inference alongside neural learning.

| Representative Neuro- Symbolic Workloads | AlphaGeometry [66] | R 2 -Guard [20] | GeLaTo [82] | Ctrl-G [83] | NeuroPC [6] | LINC [52] | |

| --- | --- | --- | --- | --- | --- | --- | --- |

| Deployment Scenario | Application | Math theorem proving & reasoning | Unsafety detection | Constrained text generation | Interactive text editing, text infilling | Classification | Logical reasoning, Deductive reasoning |

| Advantage vs. LLM | Higher deductive reasoning, higher generalization | Higher LLM resilience, higher data efficiency, effective adaptability | Guaranteed constraint satisfaction, higher generalization | Guaranteed constraints satisfaction, higher generalization | Enhanced interpretability, theoretical guarantee | Higher precision, reduced overconfidence, higher scalability | |

| Computation Pattern | Neural | LLM | LLM | LLM | LLM | DNN | LLM |

| Symbolic | First-order logic, SAT solver, acyclic graph | First-order logic, probabilistic circuit, Hidden Markov model | First-order logic, SAT solver, Hidden Markov model | Hidden Markov model, probabilistic circuits | First-order logic, probabilistic circuit | First-order logic, solver | |

TABLE I: Representative neuro-symbolic workloads. Selected neuro-symbolic workloads used in our analysis, spanning diverse application domains, deployment scenarios, and neural-symbolic computation patterns.

<details>

<summary>x3.png Details</summary>

### Visual Description

## Multi-Panel Technical Performance Analysis

### Overview

The image contains four distinct subplots (labeled a, b, c, d) presenting performance metrics for various AI systems, primarily comparing "Neuro" (neural) and "Symbolic" approaches across different tasks and hardware. The charts analyze runtime composition, latency, and computational efficiency.

### Components/Axes

The image is divided into four panels:

* **Panel (a):** A stacked bar chart titled "Runtime Percentage". The Y-axis is labeled "Runtime Percentage" from 0% to 100%. The X-axis lists 14 different systems or tasks. A legend on the left defines two categories: "Neuro" (red, diagonal hatch pattern) and "Symbolic" (green, cross-hatch pattern).

* **Panel (b):** A grouped bar chart titled "Runtime Latency (min)". The Y-axis is labeled "Runtime Latency (min)" from 0 to 12. The X-axis groups data by five systems (Alpha, R²-G, GeLaTo, Ctrl-G, LINC), each with two bars labeled "Small" and "Large". A legend within the chart area defines "Neuro" (red) and "Symbolic" (green).

* **Panel (c):** A grouped bar chart titled "Runtime Latency (min)". The Y-axis is labeled "Runtime Latency (min)" from 0 to 24. The X-axis groups data by two systems (Alpha, R²-G), each with two bars labeled "A6000" and "Orin". A legend within the chart area defines "Neuro" (red) and "Symbolic" (green).

* **Panel (d):** A scatter plot on a log-log scale. The Y-axis is labeled "Attainable Performance (TFLOPS/s)" ranging from 10⁻¹ to 10². The X-axis is labeled "Operation Intensity (FLOPS/Byte)" ranging from 10⁻¹ to 10². Data points are labeled with system names and their type (Neuro or Symb). A diagonal line represents a performance roofline.

### Detailed Analysis

#### **Panel (a): Runtime Percentage Breakdown**

This chart shows the proportion of runtime spent on Neuro vs. Symbolic components for 14 different systems/tasks.

* **IMO:** Neuro ~32.6%, Symbolic ~67.4%

* **MiniF:** Neuro ~39.8%, Symbolic ~60.2%

* **2F:** Neuro ~36.5%, Symbolic ~63.5%

* **TwinS:** Neuro ~33.2%, Symbolic ~66.8%

* **XSTest:** Neuro ~42.1%, Symbolic ~57.9%

* **Mod:** Neuro ~63.4%, Symbolic ~36.6%

* **ComGen:** Neuro ~65.1%, Symbolic ~34.9%

* **Review:** Neuro ~61.6%, Symbolic ~38.4%

* **News:** Neuro ~36.1%, Symbolic ~63.9%

* **ComGen (2nd instance):** Neuro ~39.9%, Symbolic ~60.1%

* **TextF:** Neuro ~32.3%, Symbolic ~67.7%

* **Math:** Neuro ~49.5%, Symbolic ~50.5%

* **AwA2:** Neuro ~66.0%, Symbolic ~34.0%

* **FOLIO:** Neuro ~64.3%, Symbolic ~35.7%

* **Proof:** Neuro ~64.3%, Symbolic ~35.7% (Note: This appears to be a duplicate label for the last bar, which is visually identical to the FOLIO bar).

**Trend:** The Neuro component's runtime share varies significantly, from a low of ~32.3% (TextF) to a high of ~66.0% (AwA2). Systems like Mod, ComGen, Review, AwA2, FOLIO, and Proof are Neuro-dominant (>50% Neuro runtime). Others like IMO, MiniF, 2F, TwinS, XSTest, News, and TextF are Symbolic-dominant.

#### **Panel (b): Runtime Latency by Model Size**

This chart compares the total runtime latency (in minutes) for "Small" and "Large" model variants across five systems and five tasks.

* **Alpha:**

* Task IMO: Small ~5.5 min, Large ~10 min

* Task Safety: Small ~2.5 min, Large ~7 min

* **R²-G:**

* Task CoGen: Small ~4.8 min, Large ~9.5 min

* Task Text: Small ~4 min, Large ~9 min

* **GeLaTo:** Task FOLIO: Small ~5 min, Large ~10.5 min

* **Ctrl-G:** (Data for specific tasks not fully labeled on bars, but bars are present)

* **LINC:** (Data for specific tasks not fully labeled on bars, but bars are present)

**Trend:** For all visible paired comparisons (Alpha-IMO, Alpha-Safety, R²-G-CoGen, R²-G-Text, GeLaTo-FOLIO), the "Large" model variant consistently has a higher runtime latency than the "Small" variant, often approximately double. The Neuro (red) portion of the latency also increases with model size.

#### **Panel (c): Runtime Latency by Hardware**

This chart compares runtime latency on two hardware platforms (A6000 GPU and Orin SoC) for two systems.

* **Alpha:**

* Task MiniF: A6000 ~4 min, Orin ~20 min

* Task XSTest: A6000 ~3 min, Orin ~19 min

* **R²-G:** (Bars are present but specific task labels are not visible on the X-axis for this group).

**Trend:** There is a dramatic increase in runtime latency when moving from the A6000 GPU to the Orin platform for the Alpha system. The latency on Orin is approximately 4-5 times higher than on A6000 for both tasks shown. The Symbolic (green) component constitutes the majority of the latency on both platforms.

#### **Panel (d): Performance Roofline Analysis**

This scatter plot maps various systems on an Operation Intensity vs. Attainable Performance plane.

* **Data Points (Approximate Coordinates):**

* **LLaMA-3-8B (Neuro):** (~15 FLOPS/Byte, ~15 TFLOPS/s) - Highest performance, high intensity.

* **AlphaGeo (Symb):** (~2 FLOPS/Byte, ~8 TFLOPS/s)

* **LINC (Symb):** (~0.5 FLOPS/Byte, ~1.5 TFLOPS/s)

* **Ctrl-G (Symb):** (~8 FLOPS/Byte, ~1.2 TFLOPS/s)

* **R²-Guard (Symb):** (~5 FLOPS/Byte, ~0.8 TFLOPS/s)

* **GeLaTo (Symb):** (~0.8 FLOPS/Byte, ~0.1 TFLOPS/s)

* **NeuroPC (Symb):** (~1.5 FLOPS/Byte, ~0.15 TFLOPS/s)

* Several other unlabeled green (Symbolic) points are clustered between 0.5-5 FLOPS/Byte and 0.1-1 TFLOPS/s.

**Trend:** Neuro systems (only LLaMA-3-8B shown) achieve significantly higher attainable performance and operate at higher operation intensity compared to the plotted Symbolic systems. The Symbolic systems are distributed across a lower performance band (0.1 to ~8 TFLOPS/s) and generally lower operation intensity. The diagonal roofline suggests a memory-bound region (lower left) and a compute-bound region (upper right).

### Key Observations

1. **Neuro/Symbolic Trade-off:** Panel (a) reveals a clear dichotomy: some tasks are dominated by Neuro computation, others by Symbolic. This suggests fundamental architectural differences in how these systems approach different problem types.

2. **Scalability Cost:** Panel (b) shows a consistent and significant latency penalty for scaling from "Small" to "Large" models across multiple tasks and systems.

3. **Hardware Disparity:** Panel (c) highlights a massive performance gap between high-end GPU (A6000) and embedded SoC (Orin) hardware, with latency increasing by a factor of 4-5x.

4. **Performance Frontier:** Panel (d) indicates that the evaluated Neuro system (LLaMA-3-8B) operates on a different performance frontier than the Symbolic systems, achieving higher throughput at higher operational intensity.

### Interpretation

This composite figure provides a multi-faceted analysis of Neuro-Symbolic AI system performance. The data suggests that:

* **Task Specialization:** The choice between Neuro and Symbolic approaches is not universal but highly task-dependent (Panel a). This implies hybrid systems might dynamically allocate resources based on the sub-task.

* **The Cost of Scale:** Increasing model size ("Small" to "Large") comes with a predictable and substantial runtime cost (Panel b), which must be weighed against potential accuracy gains.

* **Deployment Constraints:** Hardware platform choice (Panel c) is a critical factor, with embedded systems (Orin) incurring severe latency penalties compared to datacenter GPUs (A6000), impacting real-time application feasibility.

* **Architectural Efficiency:** The roofline analysis (Panel d) suggests current Symbolic systems are less efficient at utilizing available computational throughput (lower TFLOPS/s) and have lower operational intensity, making them potentially more memory-bound. The Neuro system demonstrates a more compute-bound profile. This gap highlights an area for optimization in Symbolic or hybrid architectures.

The overall narrative points to a complex design space where task requirements, model scale, hardware constraints, and architectural paradigm (Neuro vs. Symbolic) must be co-optimized for efficient AI system deployment.

</details>

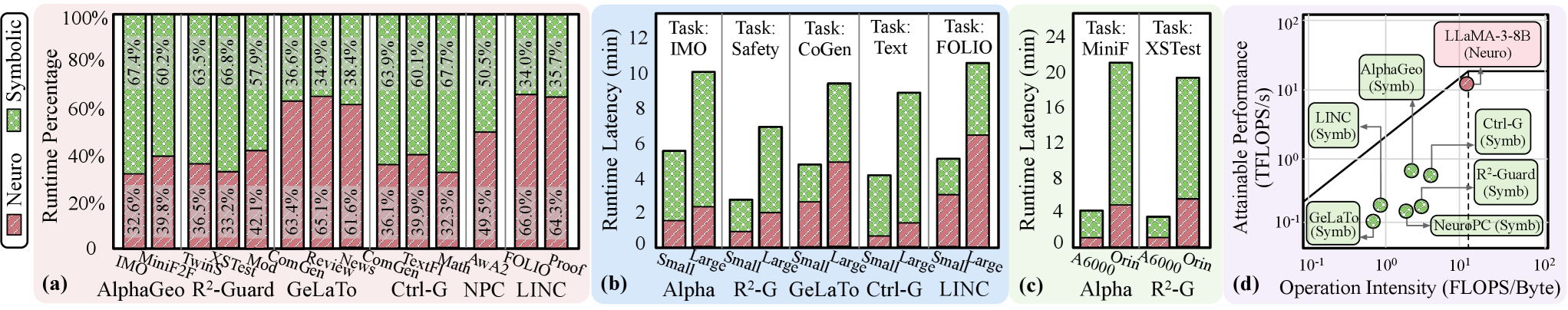

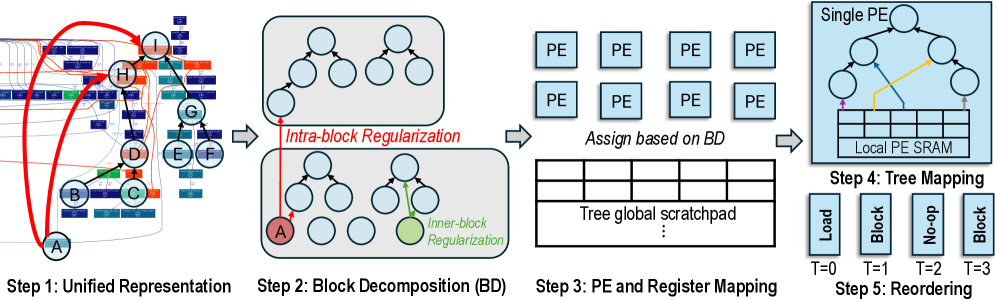

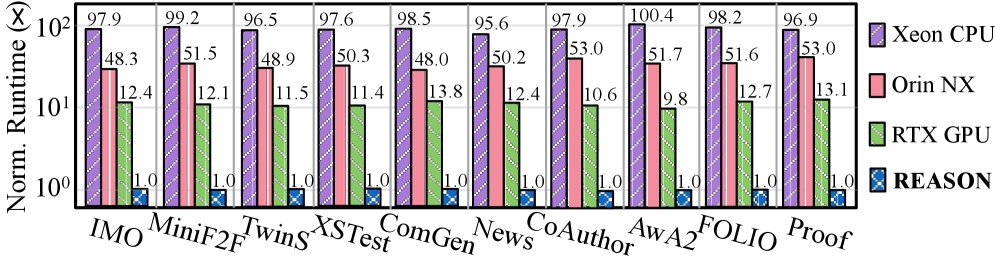

Figure 3: End-to-end neuro-symbolic workload characterization. (a) Benchmark six neuro-symbolic workloads (AlphaGeometry, R 2 -Guard, GeLaTo, Ctrl-G, NeuroPC, LINC) on CPU+GPU system, showing symbolic and probabilistic may serve as system bottlenecks. (b) Benchmark neuro-symbolic workloads on tasks with different scales, indicating that real-time performance cannot be satisfied and the potential efficiency issues. (c) Benchmark on A6000 and Orin GPU. (d) Roofline analysis, indicating server memory-bound of symbolic and probabilistic kernels.

Probabilistic Circuits (PC). PCs represent tractable probabilistic models over variables $\mathbf{X}$ as directed acyclic graphs [30, 22, 32]. Each node $n$ performs a probabilistic computation: leaf nodes specify primitive distributions $f_{n}(x)$ , while interior nodes combine their children $ch(n)$ via

$$

p_{n}(x)=\begin{cases}f_{n}(x),&\text{if }n\text{ is a leaf node}\\

\prod_{c\in\mathrm{ch}(n)}p_{c}(x),&\text{if }n\text{ is a product node}\\

\sum_{c\in\mathrm{ch}(n)}\theta_{n,c}p_{c}(x),&\text{if }n\text{ is a sum node}\end{cases} \tag{1}

$$

where $\theta_{n,c}$ denotes the non-negative weight associated with child $c$ . This recursive structure guarantees exact inference (e.g., marginals, conditionals) in time linear in circuit size. PCs’ combination of expressiveness and tractable computation makes them an ideal probabilistic backbone for neuro-symbolic systems, where neural modules learn circuit parameters while symbolic engines perform probabilistic reasoning.

Hidden Markov Model (HMM). HMMs are probabilistic model for sequential data [43], where a system evolves through hidden states governed by the first-order Markov property: the state at time step $t$ depends only on the state at time step $t-1$ . Each hidden state emits observations according to a probabilistic distribution. The joint distribution over sequence of hidden states $z_{1:T}$ and observations $x_{1:T}$ is given by

$$

p(z_{1:T},x_{1:T})=p(z_{1})p(x_{1}\mid z_{1})\prod_{t=2}^{T}p(z_{t}\mid z_{t-1})p(x_{t}\mid z_{t}) \tag{2}

$$

where $p(z_{1})$ is the initial state distribution, $p(z_{t}\mid z_{t-1})$ the transition probability, and $p(x_{t}\mid z_{t})$ the emission probability. HMMs naturally support sequential inference tasks such as filtering, smoothing, and decoding, enabling temporal reasoning in neuro-symbolic pipelines.

## III Neuro-Symbolic Workload Characterization

This section characterizes the system behavior of various neuro-symbolic workloads (Sec. III-A - III-B) and provides workload insights for computer architects (Sec. III-C - III-D).

Profiling workloads. To conduct comprehensive profiling analysis, we select six state-of-the-art representative neuro-symbolic workloads, as listed in Tab. I, covering a diverse range of applications and underlying computational patterns.

Profiling setup. We profile and analyze the selected neuro-symbolic models in terms of runtime, memory, and compute operators using cProfile for latency measurement, and NVIDIA Nsight for kernel-level profiling and analysis. Experiments are conducted on the system with NVIDIA A6000 GPU, Intel Sapphire Rapids CPUs, and DDR5 DRAM. Our software environment includes PyTorch 2.5 and JAX 0.4.6. We also conduct profiling on Jetson Orin [49] for edge scenario deployment. We track control and data flow by analyzing the profiling results in trace view and graph execution format.

### III-A Compute Latency Analysis

<details>

<summary>x4.png Details</summary>

### Visual Description

## Diagram: Research Pipeline for Neuro-Symbolic-Probabilistic AI Hardware Acceleration

### Overview

This image is a structured flowchart or research pipeline diagram illustrating the progression from high-level goals to deployment for a specialized AI hardware system. It is divided into five main vertical sections, connected by arrows indicating flow and dependency. The diagram outlines the motivation (Goals), identified problems (Challenges), proposed solutions (Methodology), system design (Architecture), and final application (Deployment) for a project focused on efficient, scalable "agentic cognition."

### Components/Axes

The diagram is organized into five primary columns or sections, from left to right:

1. **Goals (Leftmost Column):**

* **Main Title:** "Goals"

* **Central Graphic:** A box containing a star labeled "REASON" above a cluster of icons representing neural networks, logic symbols, and dice. Below this is the text "Neuro-symbolic-probabilistic AI".

* **Y-Axis Label (Left Side):** "Cognitive Capability" (with an upward-pointing arrow).

* **X-Axis Label (Bottom):** "Energy and Latency" (with a rightward-pointing arrow).

* **Bottom Text:** "Efficiency, Performance, Scalability, Cognition" with a green upward arrow next to it.

2. **Challenges (Second Column):**

* **Main Title:** "Challenges"

* Contains three red-bordered boxes, each listing a specific challenge:

* **Challenge-1:** "Irregular compute and memory access"

* **Challenge-2:** "Inefficient symbolic and probabilistic execution"

* **Challenge-3:** "Low hardware utilization and scalability"

* Arrows connect each challenge box to a corresponding "Key Insight" in the Methodology section.

3. **Methodology (Central, Largest Column):**

* **Main Title:** "Methodology"

* Contains three blue-bordered "Key Insight" boxes, each paired with a visual metaphor diagram to its right.

* **Key Insight-1:** "Unified DAG representation & pruning (Sec. IV)"

* **Diagram:** Shows a messy, irregular directed acyclic graph (DAG) on the left (with a red sad face emoji 😟) transforming into a clean, pruned tree structure on the right (with a green happy face emoji 😊).

* **Key Insight-2:** "Flexible architecture for symbolic & probabilistic (Sec. V)"

* **Diagram:** A timeline comparison. The top "naive" timeline shows long, irregular blocks of pink and green. The bottom "opt." (optimized) timeline shows shorter, more regular, and interleaved blocks. A red sad face 😟 is next to "naive," and a green happy face 😊 is next to "opt." The x-axis is labeled "time".

* **Key Insight-3:** "GPU-accelerator protocol and two-level pipelining (Sec. VI)"

* **Diagram:** Two bar charts comparing "task scale." The left chart shows a tall pink bar ("desired") next to a very short gray bar labeled "GPU" (with a red sad face 😟). The right chart shows the same tall pink bar ("desired") next to a tall green bar, with both a "GPU" icon and a chip icon (with a green happy face 😊).

4. **Architecture (Fourth Column):**

* **Main Title:** "Architecture"

* Contains five teal-bordered boxes listing architectural components:

* "Reconfigurable PE (Sec. V-B)"

* "Compilation & mapping (Sec. V-C)"

* "Bi-direction dataflow (Sec. V-D)"

* "Memory layout (Sec. V-D)"

* "Co-processor & pipelining (Sec. VI)"

* A large gray arrow points from the Methodology section to this Architecture section.

5. **Deployment (Rightmost Column):**

* **Main Title:** "Deployment"

* **Top Element:** A gear icon next to the text "Configurations: hardware & system (Sec. VII)".

* **Middle Element:** A gray box with the text "Evaluate: across cognitive tasks, complexities, scales, hardware configs (Sec. VII)". An arrow points from "Configurations" to this box.

* **Bottom Element:** A gray box with the text "Target: efficient, scalable agentic cognition". An arrow points from "Evaluate" to this box.

* A large gray arrow points from the Architecture section to this Deployment section.

### Detailed Analysis

The diagram presents a linear research and development workflow:

1. **Problem Framing:** The goal is to advance "Neuro-symbolic-probabilistic AI" towards higher "Cognitive Capability" while managing "Energy and Latency." The overarching aims are "Efficiency, Performance, Scalability, Cognition."

2. **Problem Identification:** Three core technical challenges are identified, each linked to a specific inefficiency in current systems (irregular access, inefficient execution, low utilization).

3. **Solution Methodology:** Each challenge is addressed by a corresponding key research insight, which is visually explained:

* Insight 1 tackles irregularity via graph pruning.

* Insight 2 addresses execution inefficiency through architectural flexibility, visualized as optimized scheduling.

* Insight 3 improves utilization and scalability via a specialized protocol and pipelining, visualized as closing the gap between desired and actual task scale.

4. **System Design:** The insights inform the design of a hardware architecture with five key components: a reconfigurable processing element (PE), a compilation/mapping system, bi-directional dataflow, a specialized memory layout, and co-processor/pipelining logic.

5. **Validation & Goal:** The architecture is deployed in various configurations and evaluated across a range of tasks. The final target is to achieve "efficient, scalable agentic cognition."

### Key Observations

* **Visual Metaphors:** The Methodology section uses simple but effective visual metaphors (graph pruning, timeline optimization, bar chart improvement) paired with emotive emojis (😟 to 😊) to quickly convey the benefit of each insight.

* **Section References:** Nearly every text box includes a parenthetical reference to a section in a supporting document (e.g., "Sec. IV", "Sec. V-B"), indicating this diagram is a summary of a more detailed technical paper.

* **Flow Arrows:** The diagram uses two types of arrows: thin black arrows for direct challenge-to-insight mapping, and large gray block arrows for the major phase transitions (Methodology -> Architecture -> Deployment).

* **Color Coding:** Colors are used functionally: red for problems/challenges, blue for insights/methods, teal for architectural components, and gray for deployment phases.

### Interpretation

This diagram is a high-level roadmap for a hardware-software co-design project aimed at a next-generation AI paradigm. It argues that current hardware is inefficient for neuro-symbolic-probabilistic AI due to three fundamental issues. The proposed research program systematically addresses each issue with a specific technical insight, which collectively define a novel computer architecture. The ultimate measure of success is not just raw performance, but the efficient and scalable realization of "agentic cognition"—implying AI systems that can reason, plan, and act autonomously. The heavy referencing of document sections suggests this visual is intended to orient a reader within a complex technical publication, providing a narrative thread from motivation to outcome. The progression from sad to happy faces visually reinforces the core thesis: the proposed methodology and architecture solve the identified pain points.

</details>

Figure 4: REASON overview. REASON is an integrated acceleration framework for probabilistic logical reasoning grounded neuro-symbolic AI with the goal to achieve efficient and scalable agentic cognition. REASON addresses the challenges of irregular compute and memory, symbolic and probabilistic latency bottleneck, and hardware underutilization, by proposing methodologies including unified DAG representation, reconfigurable PE, efficient dataflow, mapping, scalable architecture, two-level parallelism and programming interface. REASON is deployed across cognitive tasks and consistently demonstrates performance-efficiency improvements for compositional neuro-symbolic systems.

Latency bottleneck. We characterize the latency of representative neuro-symbolic workloads (Fig. 3 (a)). Compared to neuro kernels, symbolic and probabilistic kernels are not negligible in latency and may become system bottlenecks. For instance, the neural (symbolic) components account for 36.2% (63.8%), 37.3% (62.7%), 63.4% (36.6%), 36.1% (63.9%), 49.5% (50.5%), and 65.2% (34.8%) of runtime in AlphaGeometry, R 2 -Guard, GeLaTo, Ctrl-G, NeuroPC, and LINC, respectively. Symbolic kernels dominate AlphaGeometry’s runtime, and probabilistic kernels dominate R 2 -Guard and Ctrl-G’s, due to high irregular memory access, wrap divergence, thread underutilization, and execution parallelism. FLOPS and latency measurements further highlight this inefficiency. Notably, when using a smaller LLM (LLaMA-7B) for GeLaTo and LINC, overall accuracy remains stable, but the symbolic latency rises to 69.0% and 65.5%, respectively. We observe consistent trends in the Orin NX-based platform (Fig. 3 (c)). Symbolic components count for 63.8% of AlphaGeometry runtime on A6000 while its FLOPS count for only 19.3%, indicating inefficient hardware utilization.

Latency scalability. We evaluate runtime across reasoning tasks of varying difficulty and scale (Fig. 3 (b)). We observe that the relative runtime distribution between neural and symbolic components remains consistent of a single workload across task sizes. Total runtime increases with task complexity and scale. While LLM kernels scale efficiently due to their tensor-based GPU-friendly inference, logical and probabilistic kernels scale poorly due to the exponential growth of search space, making them slower compared to monolithic LLMs.

### III-B Roofline & Symbolic Operation & Inefficiency Analysis

Memory-bounded operation. Fig. 3 (d) presents a roofline analysis of GPU memory bandwidth versus compute efficiency. We observe that the symbolic and probabilistic components are typically memory-bound, limiting performance efficiency. For example, R 2 -Guard’s probabilistic circuits use sparse, scattered accesses for marginalization, and Ctrl-G’s HMM iteratively reads and writes state probabilities. Low compute per element makes these workloads constrained by memory access, underutilizing GPU compute resources.

TABLE II: Hardware inefficiency analysis. The compute, memory, and communication characteristics of representative neural, symbolic, and probabilistic kernels executed on CPU/GPU platform.

| | Neural Kernel | Symbolic Kernel | Probabilistic Kernel | | | |

| --- | --- | --- | --- | --- | --- | --- |

| MatMul | Softmax | Sparse MatVec | Logic | Marginal | Bayesian | |

| Compute Efficiency | | | | | | |

| Compute Throughput (%) | 96.8 | 62.2 | 32.5 | 14.7 | 35.0 | 31.1 |

| ALU Utilization (%) | 98.4 | 72.0 | 43.9 | 29.3 | 48.5 | 52.8 |

| Memory Behavior | | | | | | |

| L1 Cache Throughput (%) | 82.4 | 58.0 | 27.1 | 20.6 | 32.4 | 37.1 |

| L2 Cache Throughput (%) | 41.7 | 27.6 | 18.3 | 12.4 | 24.2 | 27.5 |

| L1 Cache Hit Rate (%) | 88.5 | 85.0 | 53.6 | 37.0 | 42.4 | 40.7 |

| L2 Cache Hit Rate (%) | 73.4 | 66.7 | 43.9 | 32.7 | 50.2 | 47.6 |

| DRAM BW Utilization (%) | 39.8 | 28.6 | 57.4 | 70.3 | 60.8 | 68.0 |

| Control Divergence and Scheduling | | | | | | |

| Warp Execution Efficiency (%) | 96.3 | 94.1 | 48.8 | 54.0 | 59.3 | 50.6 |

| Branch Efficiency (%) | 98.0 | 98.7 | 60.0 | 58.1 | 63.4 | 66.9 |

| Eligible Warps/Cycle (%) | 7.2 | 7.0 | 2.4 | 2.1 | 2.8 | 2.5 |

Hardware inefficiency analysis. We leverage Nsight Systems and Nsight Compute [51, 50] to analyze the computational, memory, and control irregularity of neural, symbolic, and probabilistic kernels, as listed in Tab. II. We observe that: First, compute throughput and ALU utilization: neural kernels achieve high throughput and ALU utilization, while symbolic/probabilistic kernels have low throughput and idle ALUs. Second, memory access and cache utilization: neural kernels see high L1 cache hit rates; symbolic kernels incur cache misses and stalls, and probabilistic kernels face high memory pressure. Third, DRAM bandwidth (BW) utilization and data movement overhead: neural workloads use on-chip caches with minimal DRAM usage, but symbolic/probabilistic workloads are DRAM-bound with heavy random-access overhead.

Sparsity analysis. We observe high, heterogeneous, irregular, and data-dependent sparsity across neuro-symbolic workloads. Symbolic and probabilistic kernels are often extremely sparse, exhibiting on average 82%, 87%, 75%, 83%, 89%, and 83% sparsity across six representative neuro-symbolic workloads, respectively, with many sparse computational paths based on low activation or probability mass. This observation motivates our adaptive DAG pruning (Sec IV-B).

### III-C Unique Characteristics of Neuro-Symbolic vs LLMs

In summary, neuro-symbolic workloads exhibit distinct characteristics compared to monolithic LLMs in compute kernels, memory behavior, dataflow, and performance scaling.

Compute kernels. LLMs are dominated by regular, highly parallel tensor operations well suited to GPUs. In contrast, neuro-symbolic workloads comprise heterogeneous symbolic and probabilistic kernels with irregular control flow, low arithmetic intensity, and poor cache locality, leading to low GPU utilization and frequent performance bottlenecks.

Memory behavior. Symbolic and probabilistic kernels are primarily memory-bound, operating over large, sparse, and irregular data structures. Probabilistic reasoning further increases memory pressure through large intermediate state caching, creating challenging trade-offs between latency, bandwidth, and on-chip storage.

Dataflow and parallelism. Neuro-symbolic workloads exhibit dynamic and tightly coupled data dependencies. Symbolic and probabilistic computations often depend on neural outputs or require compilation into LLM-compatible structures, resulting in serialized execution, limited parallelism, and amplified end-to-end latency.

Performance scaling. LLMs scale efficiently across GPUs via optimized data and model parallelism. In contrast, symbolic workloads are difficult to parallelize due to recursive control dependencies, while probabilistic kernels incur substantial inter-node communication, limiting scalability on multi-GPUs.

### III-D Identified Opportunities for Neuro-Symbolic Optimization

While neuro-symbolic systems show promise, improving their efficiency is critical for real-time and scalable deployment. Guided by the profiling insights above, we introduce REASON (Fig. 4), an algorithm-hardware co-design framework for accelerated probabilistic logical reasoning in neuro-symbolic AI. Algorithmically, a unified representation with adaptive pruning reduces memory footprint (Sec. IV). In hardware architecture, a flexible architecture and dataflow support various symbolic and probabilistic operations (Sec. V). REASON further provides adaptive scheduling and orchestration of heterogeneous LLM-symbolic agentic workloads through a programmable interface (Sec. VI). Across reasoning tasks, REASON consistently boosts performance, efficiency, and accuracy (Sec. VII).

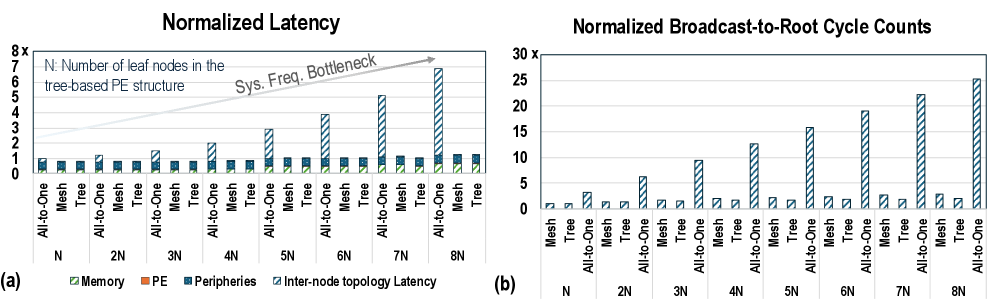

## IV REASON: Algorithm Optimizations

This section introduces the algorithmic optimizations in REASON for symbolic and probabilistic reasoning kernels. We present a unified DAG-based computational representation (Sec. IV-A), followed by adaptive pruning (Sec. IV-B) and regularization techniques (Sec. IV-C) that jointly reduce model complexity and enable efficient neuro-symbolic systems.

### IV-A Stage 1: DAG Representation Unification

Motivation. Despite addressing different reasoning goals, symbolic and probabilistic reasoning kernels often share common underlying computational patterns. For instance, logical deduction in FOL, constraint propagation in SAT, and marginal inference in PCs all rely on iterative graph-based computations. Capturing this shared structure is essential to system acceleration. DAGs provide a natural abstraction to unify these diverse kernels under a flexible computational model.

<details>

<summary>x5.png Details</summary>

### Visual Description

## Diagram: REASON Algorithm Optimization Flowchart

### Overview

The image is a technical flowchart illustrating the three-stage optimization pipeline of the "REASON Algorithm." It depicts how different symbolic and probabilistic reasoning kernels are processed through a series of transformations to produce an optimized output structure. The diagram is structured horizontally, flowing from left (input) to right (output).

### Components/Axes

The diagram is divided into three primary sections:

1. **Input Section (Left):** Labeled **"Symb/Prob Kernel Input"**. It consists of three stacked, rounded rectangular boxes, each representing a different reasoning paradigm:

* **Top Box:** "Logical Reasoning (SAT/FOL)"

* **Middle Box:** "Sequential Reasoning (HMM)"

* **Bottom Box:** "Probabilistic Reasoning (PC)"

* A single arrow points from this group to the first optimization stage.

2. **Optimization Pipeline (Center):** Labeled **"REASON Algorithm Optimization"**. This is the core of the diagram, featuring three sequential, color-coded stages:

* **Stage 1 (Pink Box):** "Stage 1: DAG Representation Unification" with a sub-label "(Sec. IV-A)".

* **Stage 2 (Green Box):** "Stage 2: Adaptive DAG Pruning" with a sub-label "(Sec. IV-B)".

* **Stage 3 (Blue Box):** "Stage 3: Two-Input DAG Regularization" with a sub-label "(Sec. IV-C)".

* Black arrows connect Stage 1 to Stage 2, and Stage 2 to Stage 3, indicating the processing flow.

3. **Output Section (Right):** Labeled **"Output"**. It contains a schematic diagram of a **Directed Acyclic Graph (DAG)**. The graph shows a hierarchical structure with multiple nodes (circles) connected by directed edges (arrows), representing the final optimized data structure.

### Detailed Analysis

* **Flow and Relationships:** The diagram establishes a clear, linear pipeline. The three distinct input reasoning methods (Logical, Sequential, Probabilistic) are first unified into a common representation (Stage 1). This unified structure is then simplified through pruning (Stage 2) and finally regularized, specifically for two-input operations (Stage 3), to yield the final DAG output.

* **Textual Content:** All text is in English. The diagram includes specific section references (Sec. IV-A, IV-B, IV-C), indicating it is likely excerpted from a larger technical paper or report where these stages are described in detail.

* **Spatial Grounding:** The legend/labels are integrated directly into the component boxes. The input is positioned at the far left, the three optimization stages are centered and arranged horizontally, and the output DAG is at the far right. The color-coding (pink, green, blue) is used solely to differentiate the three optimization stages.

### Key Observations

1. **Abstraction of Inputs:** The diagram abstracts complex reasoning methods (SAT/FOL, HMM, PC) into simple input blocks, focusing the viewer's attention on the optimization process itself rather than the specifics of the input formats.

2. **Progressive Refinement:** The stage names suggest a progression from structural unification ("Representation Unification") to efficiency improvement ("Pruning") and finally to structural refinement ("Regularization").

3. **Specific Output Target:** The final stage ("Two-Input DAG Regularization") and the output diagram imply the algorithm is optimized for producing DAGs that are particularly suited for operations involving two inputs.

### Interpretation

This flowchart visually summarizes a method for creating a unified, efficient computational structure (a DAG) from heterogeneous reasoning systems. The process aims to bridge different AI reasoning paradigms by converting them into a common graphical format and then applying a series of optimizations.

The **"DAG Representation Unification"** (Stage 1) is the critical translation step, allowing disparate logical, sequential, and probabilistic models to be processed by the same subsequent tools. **"Adaptive DAG Pruning"** (Stage 2) likely removes redundant or low-probability paths to reduce complexity and computational cost. The final **"Two-Input DAG Regularization"** (Stage 3) suggests a focus on standardizing the graph's structure for common binary operations, potentially improving predictability and performance in downstream tasks.

The overall pipeline demonstrates a modular approach to AI system integration, where the complexity of combining different reasoning types is managed through a standardized intermediate representation (the DAG) and a clear sequence of optimization steps. The references to specific sections (IV-A, B, C) indicate this is a high-level overview of a more detailed technical methodology.

</details>

| SAT/FOL PC HMM | Literals and logical operators Primitive distributions, sum and product nodes Hidden state variables at each time step | Logical dependencies between literals, clauses, and formulas Weighted dependencies encoding probabilistic factorization State transition and emission dependencies | Search and deduction via traversal (DPLL/CDCL) Bottom-up probability aggregation and top-down flow propagation Sequential message passing (forward–backward, decoding) |

| --- | --- | --- | --- |

Figure 5: Unified DAG representations of neuro-symbolic kernels. Logical (SAT/FOL), probabilistic (PC), and sequential (HMM) reasoning are expressed using DAG abstraction. Nodes represent atomic reasoning operations, edges encode dependency structure, and graph traversals implement inference procedures. This unification enables shared compilation, pruning, and hardware mapping in REASON.

Methodology. We unify symbolic and probabilistic reasoning kernels under a DAG abstraction, where each node represents an atomic reasoning operation and each directed edge encodes a data/control dependency (Fig. 5). This representation enables a uniform compilation flow – construction, transformation, and scheduling – across heterogeneous kernels (logical deduction, constraint solving, probabilistic aggregation, and sequential message passing), and serves as the algorithmic substrate for subsequent pruning and regularization.

#### For FOL and SAT solvers

DAG nodes represent variables and logical connectives, with edges indicating dependencies between literals and clauses. We represent a propositional CNF formula $\varphi=\bigwedge_{i=1}^{m}\Bigl(\bigvee_{j=1}^{k_{i}}l_{ij}\Bigr)$ as DAG with three layers: literal nodes for each literal $l_{ij}$ , clause nodes implementing disjunction over literals in $\bigvee_{j}l_{ij}$ , and formula nodes implementing conjunction over clauses $\bigwedge_{i}$ . In SAT, DAG captures the branching and conflict resolution structures in DPLL/CDCL procedures. In FOL, formulas are encoded as DAGs where inference rules act as graph transformation operators that derive contradictions through node and edge expansion. The compiler converts FOL and SAT inputs (clauses in CNF or quantifier-free predicates) into DAGs via: Step- 1 Normalization: predicates are transformed to CNF, removing quantifiers and forming disjunctions of literals. Step- 2 Node creation: each literal becomes a leaf node, each clause an OR node over its literals, and the formula an AND node over clauses. Step- 3 Edge encoding: edges capture dependencies (literal $\rightarrow$ clause $\rightarrow$ formula), while watch-lists as metadata.

#### For PCs

DAG nodes correspond to sum (mixture) or product (factorization) operations $p_{n}(x)$ over input $x$ (to variable $\mathbf{X}$ ), with children $ch(x)$ . Leaves represent primitive distributions $f_{n}(x)$ . Edges model conditional dependencies. The DAG structure facilitates efficient inference through bottom-up probability evaluation, exploiting structural independence and enabling effective pruning and memorization during probability queries (Eq. 1). The compiler converts PC into DAGs through: Step- 1 Graph extraction: nodes represent random variables, factors, or sub-circuits parsed from expressions such as $P_{n}(x)$ . Step- 2 Node typing: arithmetic operators map to sum nodes for marginalization and product nodes for factor conjunction, while leaf nodes store constants or probabilities.

#### For HMMs

The unrolled DAG spans time steps, with nodes representing transition factors $p(z_{t}|z_{t-1})$ and emission factors $p(x_{t}|z_{t})$ (Eq. 2), and edges connecting factors across adjacent time steps to reflect Markov dependency. Sequential inference (filtering/smoothing/decoding) becomes structured message passing on this DAG: each step aggregates contributions from predecessor states through transition factors and then applies emission factors. The compiler converts HMMs into DAGs through: Step- 1 Sequence unroll: Each time step becomes a DAG layer, representing states and transitions. Step- 2 Node mapping: Product nodes combine transition and emission probabilities; sum nodes aggregate over prior states.

The unified DAG abstraction lays the algorithmic foundation for subsequent pruning, regularization, and hardware mapping, supporting efficient acceleration of neuro-symbolic workloads.

<details>

<summary>x6.png Details</summary>

### Visual Description

\n

## Technical Diagram: REASON Plug-in Architecture for GPU Acceleration

### Overview

The image is a multi-part technical diagram illustrating a proposed hardware architecture called "REASON" designed to be integrated as a plug-in into a GPU. The diagram is divided into five interconnected sections labeled (a) through (e), detailing the system from the high-level GPU integration down to the microarchitecture of individual processing nodes and symbolic memory support.

### Components/Axes

The diagram is segmented into five primary regions:

1. **(a) GPU with Proposed Plug-in:** Shows the integration of the REASON plug-in within a standard GPU memory hierarchy.

2. **(b) Proposed REASON Plug-in:** Details the internal structure of the plug-in itself.

3. **(c) Tree-based PE Architecture:** A detailed view of the Processing Element (PE) array and its interconnect network.

4. **(d) Node Microarchitecture:** A close-up of the internal logic within a single processing node.

5. **(e) Symbolic Mem. Support:** Illustrates hardware structures for managing symbolic data.

**Key Labels and Components by Section:**

**(a) GPU with Proposed Plug-in (Leftmost block)**

* **Off-chip Memory** (Top)

* **Memory Controller**

* **GPU Graphics Processing Clusters (GPC)** (Two instances shown, stacked)

* **Shared L2 Cache** (Left side, connected to GPCs and Memory Controller)

* **Proposed REASON Plug-in** (Highlighted in light blue, connected to Shared L2 Cache and Giga Thread Engine)

* **Giga Thread Engine** (Bottom)

* Arrows indicate bidirectional data flow between the REASON Plug-in, Shared L2 Cache, and Giga Thread Engine.

**(b) Proposed REASON Plug-in (Second block from left)**

* **Global Controller** (Top)

* **Tree-based PE** (Four instances shown, arranged around a central interconnect)

* **Global Interconnect** (Central cross-shaped structure connecting the four PEs)

* **Workload Scheduler** (Bottom left)

* **Ctrl** (Bottom center)

* **Shared Local Memory** (Bottom)

* **Custom SIMD Unit** (Bottom right)

**(c) Tree-based PE Architecture (Central, largest block)**

* **SIMD** (Top left)

* **Intermediate Buffer** (Top center)

* **M:1 Output Interconnect** (Below Intermediate Buffer)

* **Scalar PE** (Top right)

* **BCP FIFO** (Right side, connected to Scalar PE)

* **Control Logic / MMU** (Left side)

* **Forwarding Logic** (Left side, below Control Logic)

* **Decode** (Bottom left)

* **Pre-fetcher / DMA** (Bottom left, next to Decode)

* **Watched Literals Controller** (Bottom center, with a red "From Broadcast" arrow pointing to it)

* **Benes Network (N:N Distribution Crossbar)** (Bottom center-right)

* **N SRAM Banks** (Bottom right)

* **Leaf Node** (Labels point to the bottom layer of circles in the tree)

* **From L2** (Arrow entering from bottom right)

* **To Last Node PE** (Arrow exiting bottom center)

* **From Forwarding or PE** (Arrow entering Benes Network from left)

* **Legend (within section c):**

* **Red Line:** `DPLL Broadcast (Symbolic)`

* **Blue Line:** `SpMIP/MDAG/DPLL Reduction (Neuro/Probabilistic/Symbolic)`

* The core visual is a **tree structure** of interconnected nodes (circles). Red and blue lines trace different communication paths through this tree. The tree has a root at the top, multiple intermediate layers, and leaf nodes at the bottom.

**(d) Node Microarchitecture (Bottom right inset)**

* **XIK** (A component, possibly a processing unit)

* **Adder** (Symbol: `+`)

* **Fwd** (Forwarding multiplexers, two instances)

* **Data** (Input/Output labels)

* **Control Signals** (Bottom)

* Arrows show data flow into the XIK and Adder, with forwarding paths (`Fwd`) around them.

**(e) Symbolic Mem. Support (Top right inset)**

* **BCP FIFO** (Top left)

* **Broadcast / Msg Assign** (Top center)

* **Watched Literals** (Top right, with sub-labels: `Literal`, `Head`, `x1`, `x2`, `NULL`, `Clause (Cnt) Data`)

* **Implication** (Two instances, with sub-labels: `x1=0`, `x1=1`)

* **Correl. Cache** (Bottom left)

* **Index RAM** (Bottom right)

* **Clause (Cnt) Data** (Bottom right, connected to Index RAM)

* Arrows indicate data flow between these components, including a path from "Broadcast / Msg Assign" to "Watched Literals."

### Detailed Analysis

The diagram presents a hierarchical hardware design for symbolic reasoning acceleration.

1. **System Integration (a):** The REASON Plug-in is positioned as a co-processor that interfaces directly with the GPU's Shared L2 Cache and the Giga Thread Engine, suggesting it operates at a high level within the memory hierarchy, close to the main compute units.

2. **Plug-in Structure (b):** The plug-in itself contains a Global Controller managing four Tree-based Processing Elements (PEs). These PEs communicate via a Global Interconnect. Supporting units include a Workload Scheduler, control logic (`Ctrl`), Shared Local Memory, and a Custom SIMD Unit, indicating a blend of control-driven and data-parallel processing.

3. **Tree-based PE Core (c):** This is the computational heart. A tree network of nodes facilitates parallel operations. The legend defines two critical communication protocols:

* **DPLL Broadcast (Symbolic) - Red Lines:** These paths flow *downward* from the root to the leaves, suggesting a broadcast of symbolic constraints or decisions (like in a DPLL SAT solver).

* **SpMIP/MDAG/DPLL Reduction - Blue Lines:** These paths flow *upward* from leaves to the root, indicating a reduction or aggregation of results (e.g., neuro-symbolic inference, probabilistic reasoning, or conflict analysis).

* The architecture includes dedicated hardware for instruction decode, DMA-based pre-fetching, a "Watched Literals Controller" (a key data structure in SAT solvers), a Benes Network for flexible data distribution, and multiple SRAM banks for local storage.

4. **Node-Level Detail (d):** Each node in the tree contains basic arithmetic (`Adder`) and a specialized unit (`XIK`), with forwarding paths to minimize pipeline stalls.

5. **Symbolic Memory (e):** Dedicated hardware manages symbolic concepts: FIFOs for Boolean Constraint Propagation (BCP), storage for "Watched Literals" (with fields for literal, head, and clause data), an implication queue, a correlation cache, and an index RAM. This structure is optimized for the memory access patterns of symbolic algorithms.

### Key Observations

* **Hybrid Architecture:** The design explicitly supports "Neuro/Probabilistic/Symbolic" processing (per the blue line legend), indicating a unified architecture for different AI paradigms.

* **SAT Solver Inspiration:** Multiple components (`Watched Literals`, `BCP FIFO`, `DPLL` in the legend) are direct references to algorithms used in Boolean Satisfiability (SAT) solvers, suggesting this hardware is optimized for such workloads.

* **Tree-Based Parallelism:** The core computational model is a tree, which is well-suited for divide-and-conquer algorithms common in search and reasoning tasks.

* **Custom Interconnects:** The use of a Benes Network (a non-blocking crossbar) and an M:1 Output Interconnect highlights a focus on low-latency, high-bandwidth communication between processing nodes.

* **Memory Hierarchy:** The design features a multi-level memory strategy: Off-chip Memory -> Shared L2 Cache -> Shared Local Memory (in the plug-in) -> N SRAM Banks (in the PE) -> Intermediate Buffer.

### Interpretation

This diagram details a specialized hardware accelerator designed to overcome the limitations of general-purpose GPUs for complex reasoning tasks. The **REASON Plug-in** is not just a simple compute unit; it's a self-contained subsystem with its own controller, memory, scheduler, and a massively parallel tree of processing nodes.

The architecture's primary innovation is its **hardware mapping of symbolic reasoning algorithms**. By implementing structures like watched literal queues and BCP FIFOs directly in silicon, and by creating a physical tree network that mirrors the logical tree traversal of algorithms like DPLL, the design aims to achieve orders-of-magnitude speedups over software implementations. The inclusion of neuro-symbolic and probabilistic paths indicates a forward-looking design intended for next-generation AI models that combine learning with logical reasoning.

The **spatial organization** is telling: the high-level GPU integration (a) shows *where* it fits, the plug-in view (b) shows *what* it contains, and the detailed PE (c) and node (d) views show *how* it works at the circuit level. The symbolic memory support (e) is the crucial link that feeds data into this computational tree. The entire system is a coherent pipeline from symbolic data management (e) through parallel tree-based processing (c, d) orchestrated by a global controller (b), all integrated into the GPU's memory ecosystem (a). This represents a significant architectural effort to harden AI reasoning workloads into dedicated, efficient silicon.

</details>

Figure 6: Overview of the REASON hardware acceleration system. (a) Integration of REASON as a GPU co-processor. (b) REASON plug-in architecture with PEs, shared local memory, and global scheduling. (c) Tree-based PE architecture enabling broadcast, reduction, and irregular DAG execution. (d) Micro-architecture of a tree node supporting arithmetic and logical operations. (e) FIFO and memory layout supporting symbolic reasoning.

### IV-B Stage 2: Adaptive DAG Pruning

Motivation. While the unified DAG representation provides a common abstraction, it may contain significant redundancy, such as logically implied literals, inactive substructures, or low-probability paths, that inflate DAG size and degrade performance without improving inference quality.