\n

## Diagram: DRAM Module Architecture

### Overview

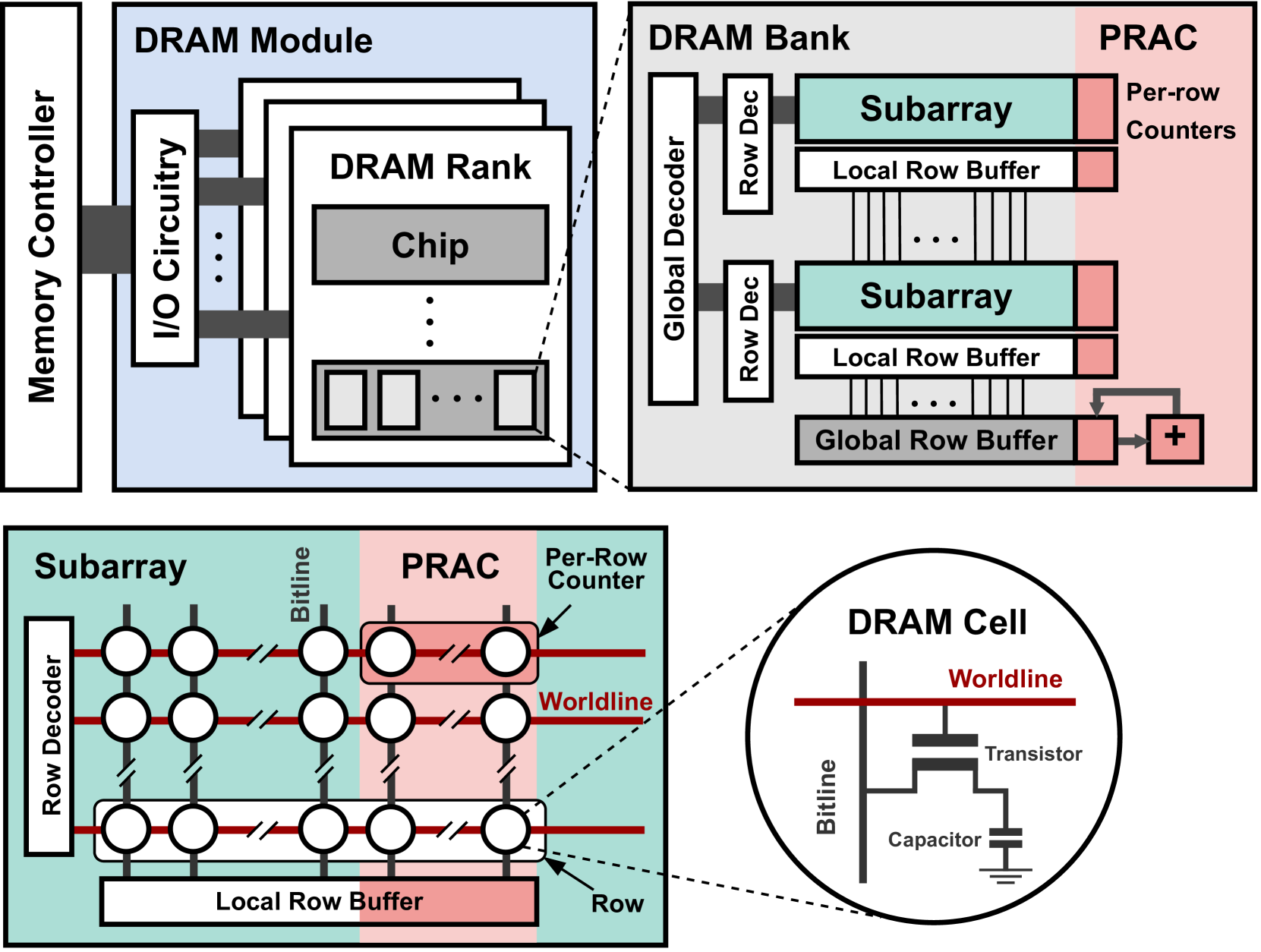

The image presents a hierarchical block diagram illustrating the architecture of a Dynamic Random Access Memory (DRAM) module. It details the organization from the Memory Controller down to the individual DRAM cell, highlighting key components like DRAM Ranks, Chips, Subarrays, PRAC (Per-row Access Counter), and the DRAM cell itself. The diagram is divided into three main sections: a high-level module view, a DRAM Bank view, and a detailed subarray/cell view.

### Components/Axes

The diagram features the following components:

* **Memory Controller:** Top-left corner.

* **I/O Circuitry:** Adjacent to the Memory Controller.

* **DRAM Module:** Encompassing the entire upper section.

* **DRAM Rank:** Within the DRAM Module, containing multiple Chips.

* **Chip:** Individual memory chips within a Rank.

* **DRAM Bank:** Upper-right section, detailing the internal organization of a DRAM Rank.

* **Global Decoder:** Connects the DRAM Bank to the DRAM Rank.

* **Row Dec:** Row Decoder within the DRAM Bank.

* **Subarray:** Multiple subarrays within a DRAM Bank.

* **Local Row Buffer:** Associated with each Subarray.

* **Global Row Buffer:** Connects the subarrays.

* **PRAC (Per-row Access Counter):** Adjacent to the Subarrays.

* **Subarray (Detailed):** Bottom-left section, showing the arrangement of cells.

* **Bitline:** Vertical lines connecting cells within the Subarray.

* **Wordline:** Horizontal lines selecting rows of cells.

* **Row:** Represents a row of cells.

* **DRAM Cell:** Bottom-right section, showing the transistor and capacitor structure.

* **Transistor:** Component of the DRAM cell.

* **Capacitor:** Component of the DRAM cell.

The diagram uses arrows to indicate data flow and connections between components.

### Detailed Analysis or Content Details

**DRAM Module Level:**

* The DRAM Module contains multiple DRAM Ranks.

* Each DRAM Rank contains multiple Chips.

* The I/O Circuitry connects the Memory Controller to the DRAM Ranks.

**DRAM Bank Level:**

* The DRAM Bank consists of multiple Subarrays.

* Each Subarray has a Local Row Buffer.

* A Global Row Buffer connects the Subarrays.

* The Global Decoder connects the DRAM Bank to the DRAM Rank.

* PRAC is positioned adjacent to the Subarrays.

**Subarray Level:**

* The Subarray is organized as a grid of DRAM Cells.

* Bitlines run vertically, and Wordlines run horizontally.

* The Row Decoder selects the Wordline for a specific Row.

* The Local Row Buffer is connected to the rows of the Subarray.

**DRAM Cell Level:**

* The DRAM Cell consists of a Transistor and a Capacitor.

* The Capacitor stores the data bit.

* The Transistor acts as a switch to access the Capacitor.

* The Wordline controls the Transistor.

* The Bitline reads/writes data to the Capacitor.

### Key Observations

* The diagram illustrates a hierarchical structure, with increasing levels of detail as you move from the Module to the Cell.

* The PRAC is a key component for managing access to rows within the Subarray.

* The Local Row Buffer acts as a cache for frequently accessed rows.

* The DRAM cell is a simple but effective storage element.

* The diagram emphasizes the parallel access capabilities of DRAM through the use of multiple Subarrays.

### Interpretation

The diagram demonstrates the complex organization required to implement a DRAM module. The hierarchical structure allows for efficient access to large amounts of data. The PRAC and Local Row Buffers are crucial for optimizing performance by reducing access latency. The diagram highlights the fundamental building block of DRAM – the DRAM cell – and its simple yet effective design. The arrangement of subarrays and the use of bitlines and wordlines enable parallel access to data, which is essential for high-bandwidth memory systems. The diagram suggests a focus on optimizing row access patterns, as evidenced by the prominence of the PRAC and Local Row Buffers. The overall architecture is designed to balance capacity, speed, and power consumption. The diagram is a simplified representation, and real-world DRAM modules are significantly more complex, but it provides a valuable overview of the key components and their relationships.